Анализатор спектра

Иллюстрации

Показать всеРеферат

АНАЛИЗАТОР СПЕКТРА, со-держащий п последовательно SKjaoЧениих идентичных блоков измерения , каждый из которых состоит из многовходойого кo iмyтaтopa, выходы KoTOi oro за исключением последнего, . подключены к ячейкам памяти первой группы линий задержки, группы цифроаналоговых перемножителей, вторые |входал которых подключены к выходам :постоянных запоминающих элементов, а выходы упомянутых Перемножителей, за исюпоЧением первого, через ячейки памяти второй группы линий задержки соединены с входами следую;щего блока измерения, а также синхронизатор , связанный с управляю;адими входами коммутатора, ячеек I памяти обеих групп линий задержки, постоянных запоминающих элементов, отличающийся тем, что, с целью повышения быстродействия анализатора, в каждый блок измерения введена резисторная матрица с постоянными и одинаковыми для ка5кдого блока коэффициентами,включенная между выходами памяти первой группы линий задержки и информационными входами Дифроаналоговых перемножителей, при этом последНИИ выход второго многовходового коммутатора подключен к соответствую (Л CZ ) цему , в ходу ре 3 исторной матрицы, а выход первого цифроаналогового перемножителя сбязан с соответствующим входом следующего блока измерения .

СООЗ СОВЕТСКИХ

63WNOtl

РЕСПУБЛИК ур) G 01 R 23/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOIVIV СВИДЕТЕЙЪСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3418692/18-21 (22) 07.04.82

{46) 07.08. 83. Бюл. Р 29 (72) Ю.В.Шубс, Б.A.Бойчук,В.A.Гудым и A.B.Èàéñòpóê . 1 53) 621 ° 317.757 (088 ° 8) (56) 1. Патент Cia Р 3544755, кл. 6 01 R 23/16, 1970. (54) (57) АНАЛИЗАТОР СПЕКТРА содержащий и последовательно включенных идентичных блоков измерения, каждый из которых состоит измноговходового коммутатора, выходы которого за исключением последнего, подключены к ячейкам памяти первой группы линий задержки, группы цифроаналоговых перемножителей, вторые ,входы которых подключены к выходам

:постоянных запоминающих элементов, а выходы упомянутых перемножителей, за исключением первого, через ячейки памяти второй группы линий за,SU„„1033978 A держки соединены с входами следую:щего блока измерения, а также синхронизатор, связанный с управляю;щими входами коммутатора, ячеек

;памяти обеих групп линий задержки, постоянных запоминающих элементов, отличающийся тем, что, с целью повышения быстродействия анализатора, в каждый блок измерения введена резисторная матрица с постоянными и одинаковыми для каждого блока коэффициентами,включенная между выходами ячеек памяти первой группы линий задержки и ин-. формационными входами цифроаналоговых перемножителей, при этом последний выход второго многовходового щ

Я коммутатора подключен к соответствующему .входу резисторной матрицы, а выход первого цифроаналогового перемножителя связан с соответствую- ( щим входом следующего блока измерения.

1033978

Изобретение относится к радиоизмерительной технике и предназначено для дискретной обработки сигна" лов в реальном масштабе времени.

Наиболее близким к предлагаемому является анализатор, содержащий последовательно включенные идентичные блоки измерения, каждый из которых состоит иэ многовходового коммутатора, выходы которого за исключением последнего. подключены к ячейкам памяти первой группы линий задержки, группы цифроаналоговых перемножителей, вторые входы которых подключены к выходам постоянных запоминающих элементов, а выходы )5. переглноиителей, эа исключением первого, через ячейки памяти второй группы линий задержки соединены с входами следующего блока измерения, а,так><е синхронизатор, связан- 20 ный с управляющими входами коммутатора, ячеек памяти обех групп линий задержки, постоянных запоминающих элементов Г 1 1.

Недостатком известного анализатора является большое время, затрачиваемое на операциях перемножения.

Цель изобретения — повышение быстродействия анализатора.

30, Поставленная цель достигается тем, что в анализатор спектра, содер><ащий .л последовательно вклю ченных идентичных блоков измерения, каждый из которых состоит из многовходового коммутатора, выходы кото35 рого за исключением последнего подключены к ячейкам памяти первой группы линий задержки, группы цифроаналоговы:< перемножителей, вторые входы которых подключены к .выходам 40 постоянных запоминающих элементов, а выходы упомянутых перемножителей, за ис><хпочением первого через ячейки памяти второй группы линий задерх<ки соединены с входами следующего блока 45 измерсния, а такие синхронизатор, .связанный с управляющими входами коммутатора, ячеек памяти обеих групп .линий задержки и постоянных запоминающих элементов, в каждый блок из-. 50 мерения введена резисторная .матрица с постоянными и одинаковыми для каждого блока коэффициентами,, включенная глежду выходами ячеек памяти .первой группы линий задержки и информа- 55 ционными входами цифроаналоговых перемножителей, прй этом последний .выход. второго многовходового коммутатора подключен к соответствующему входу резисторной матрицы, а выход первого -цифроаналогового перемноиителя связан с соответствую-, щим входом следующего блока измерения.

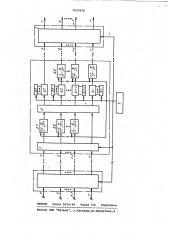

На черте>хе представлена .структур-» ная.схема предлагаемого анализатора. 65

Устройство содержит последовательно соединенные блоки измерения, каждый из которых состоит из многовходового коммутатора 1, ячеек 2 ° 12.<> памяти первой группы линий задер><ки, резистивной матрицы 3, аналого-цифровых перемножителей 4.1-4.)" постоянных запоминающих элементов

5. 1-5 л . ячеек б. 1-6, г пагляти второй группы линий задержки и синхронизатора 7.

Работа анализатора показана на примере одного блока, представленного в развернутом виде на чертеже.

Под воздействием последовательности тактовых импульсов от синхронизатора 7 выборка (реалиэаци» )из N эквидистантных временных отсчетов анализируемого процесса распределяется при помощи многовходового коммутатора 1 по информационным входам первого блока измерения. РасI ,пределяемые дискретные отсчеты пос-. тупают параллельно на .входы ячеек

2 ° 1-2.< памяти первой группы линий задержки. Число запоминающих ячеек 2.1-2.<. в линиях задержки группы различно и выбрано таковым, чтобы на выходах линий задержки на каждом также фиксировалось число отсчетов, необходимое для выполнения данной итерации быстрого преобразования Фурье (БПФ). С выходов ячеек 2.1-2.г задержанные отсчеты поступают на резисторную матрицу

3 вычисления частных дискретных преобразований Фурье (ДПФ).Коэффициен:ты передачи по каждому из входов матриць> 3 вычисления частных ДПФ в каждом блоке фиксированы (ввиду их постоянства для любой итерации

БПФ ) и равны значениям весовых коэффициентов Фурье по модулю tоснования разложения БПФ и, соответственно, одинаковы для всех реэисторных матриц в каждом блоке.

В результате на выходах матриц 3 формируются результаты вычисления частных дискретных преобразований

Фурье по модулю г, которые параллельно поступают на входы цифроаналоговых перемножителей 4.1-4. ..

Под воздействием последовательности тактовых импульсов от -..инхрони- затора 7 из цифровых постоянных зайоминающих элементов 5.1-5.r параллельно считываются W/г весовых (поворачивающих )коэффициен" тов Фурье, значения которых взяты по модулю полного преобразования и отличаются для каждого блока. Эти весовые коэффициенты поступают на вторые цифровые входы цифроаналоговых перемножителей 4.1-4.Ь и в результате линейного декодированияпреобразования с весом (иными словами перемножения ) на выходах

1033978

4.1-4.г формируются результаты вычисления частных дискретных пре. образований Фурье, домноженные на ! поворачивающие весовые коэффициенты. Затем, также под воздействием последовательности тактовых импульсов от синхронизатора 7, эти результаты поступают на входы ячеек 6.2 .—

6. памяти. второй группы линий задержки, где происходит обратная, по сравнению с первой группой линий задержки, перестановка полученных дискретных отсчетов. В дальнейшем полученные промежуточные результаты с выходов ячеек 6.2-6. . второй группы линий задержки поступают .на входы многовходового коммутатора следующего блока анализатора спектра или на выход устройства (если данный блок последний ) и описанный

- выше процесс повторяется раз до . окончательного получения искомого массива частотных отсчетов гЮсле выполнения процедуры БПФ.

Введение в анализатор спектра резистивных матриц вычисления частных дискретных преобразований Фурье с постоянными для каждого блока весовыми коэффициентами существенно повышает быстродействие параллельного. анализатора спектра, поскольку

30 вместо традиционных цифровых матричных перемножителей, требующих применения порядка 120 интегральных схем и реализующих одно умножение за время примерно 150 нс.,используются резисторные матрицы, в которых частные ДПФ выполняются за единицы наносекунд (параллельно по модулю t ). Стоимость резисторных матриц примерно в 10-15 раз ниже стои:мости одного матричного перемножителя.

1033978

°

- ВНИИПЙ Эаказ 5619/49 Тираж 710 Подписное

Филиал ППП "Патент", г.Ужгород,ул.Проектная„4