Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ.БЛОКОВ ПО ав. св. № 868763, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены буферный регистр, первый преобразователь кодов, перфоратор, второй блок памяти, считыватель, второй преобразователь кодов,соединенный выходами с вxoдa в блока записи ,входом с выходом Гсчитывателя, первый вход которого подключен, к первому выходу блока управления и-первому входу перфоратора, второй вхрд - к выходу второго блока памяти, соединенного входом с выходом перфоратора, второй вход которого соединен с выходом первого преобразователя кодов , третий вход - с вTopbw выходом счетчика и первым входсм буферного perHCTpS/ подключенного вторыми входами к выходам регистра теста, а выходомк входу первого преобразо- , , вателя кодов. (Л с

„„SU„„1033 994 А

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ЗИ) G 01 R 31/28

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ н вто сномм саидятельстам (54) (57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

ЛОГИЧЕСКИХ, БЛОКОВ по ав. св.

Р 868763, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены буферный регистр, первый преобразователь кодов, перфоратор, второй ".(61) 868763 (21) 3412805/18-21 (22) 25.03i82 (46) 07. 08 83. Бюл. Р 29 (72) Е.И.Николаев и Е.З.Храпко (53) 681=. 519 (088. 8) (56) 1. Авторское свидетельство СССР

:Р 868763, кл, G, 01F 11/04, 1982 (прототип) . блок памяти, считыватель, второй . преобразователь кодов, соединенный выходами с входами блока записи,входомс выходом считывателя, первый вход которого подключен. к первому выходу блока управления и-первому входу перфоратора, второй вхрд - .к выходу второго блока памяти, соединенного входом с выходом перфоратора, второй вход которого соединен с выходом первого преобразователя кодов, третий вход - с вторым выходом счетчика и первым входом буферного регистрЕ, подключенного вторыми . входами к выходам регистра теста, а ,выходом- к входу первого преобразо, вателя кодов е.

1033994

Изобретение относится к контрольм но-измерительной технике и может быть использовано для контроля логических блоков средств ЦВТ.

Наиболее близким к предлагаемому является устройство для контроля логических блоков, содержащее блок управления, блок памяти, соединенм ный входом с первым выходом блока управления, а выходами - с первыми входами блока управления, регистр теста, выходы которого соединены соответственно с первыми входами: элементов сравнения и первыми входам ми элементов коммутации, вторые входы которых соединены с третьими выходами блока управления, третьи— с выводами контролируемого .блока и с вторыми входами соответствующих элементов сравнения, выходы которыя соединены с входами блока управле- 20 ния, генератор импульсов, триггер, счетчик, дешифратор, первый элемент И и по числу входов регистра теста — вторые элементы И, первые входы которых соединены с соот- 25 ветствующими выходами блока записи информации, вторые входы— с соответствующими выходами дешифратора, выходы - с входами регистра теста, первые входы дешиф" ратора подключены к первым выходам счетчика, второй выход которого соединен с третьими входами элементов сравнения и первым входом триггера, второй вход KQTopox соеди- ° нен с первым выходом блока управления, третий вход — с четвертым выхо дом блока управления, а выход — с первым входом элемента И, второй вход которого подключен к выходу re- 4p нератора импульсов, а выход - к; входу счетчика и второму входу дешифратора (1) .

Недостатком известного устройства является низкое быстродействие, обусловленное тем, что наборы контролирующего теста осуществляется на штеккерном наборном поле вручную, при этом допускаются

Ьшибки. Указанные ошибки приводят к зйачительному количеству остановов при контроле по неверным текстам и дополнительным затратам времени на отыскание ошибок в тесте.

Цель изобретения — повышение быстродействия устройства. . 55

Укаэанная цел з достигается тем, что устройство для контроля логических блоков, содержащее блок уйравления, блок памяти, соединенный входом. с первым выходом блока 60 управления а выходами †. с первыми входами блока записи, второй вход которого соединен с. вторым выходом блока управления, регистр теста, выходы которого соединены 65 с первыми входами элементов сравнения и первыми входами элементов коммутации, вторые входы которых соединены с третьими выходами блока управления, третьи - с выводами .контролируемого блока и с вторыми входами соответствукщих:; элементов сравнения., выходы которых соединены с входами блока управления, ver нератор импульсов, триггер, счетчик дешифратор, первый элемент И и по числу входов регистра теста вторые элементы И, первые входы кото" рых соединены с соответствующими ньщодами блока записи информации, вторые входы — с соответствующими выходами дешифратора, выходы — с входами регистра теста, первые входы дешифратора подключены к пер" вым выходам счетчика, второй выход которого соединен с третьими входами элементов сравнения и первым входом триггера, второй вход которого соединен с первым выходом блока управления, третий входс четвертым выходом блока управления, а выход — с йервым входом первого элемента И, второй вход которого подключен к выходу генератора им- пульсов, а выход - ко входу счетчика .и второму входу дешифратора, введены буферный регистр, первый преобразователь кодон, перфоратор, второй блок памяти, считыватель, второй преобразователь кодов, соединенный выходами с входами блока записи, входом — с выходом считывателя, первый вход которого подключен к первому выходу блока управления и первому входу перфоратора, второй вход — к выходу второго i блока памяти, соединенного входом с выходом перфоратора, второй вход которого соединен с выходом первого преобразователя кодов, третий входс вторым выходом счетчика и первым входом буферного регистра, подключенного вторыми входами к выходам

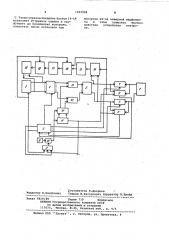

Регистра теста, а выходом - к входу первого преобразователя кодов, На чертеже приведена блок-схема устройства для контроля логического блока. !

Устройство содержит блок 2 управления, первый блок 3 памяти, блок

4 записи, регистр 5 теста, элементы

6 сравнения, элементы 7 коммутации, генератор 8 импульсов, триггер 9, первый элемент 10 И, счетчик 11 дешифратор 12.> вторйе элементы И 13, буферный регистр 14, первый преобразователь 15 кодон,перфоратор 16, второй блок 17 памяти, считыватель

18, второй преобразонатель 19 кодов.

Устройство работает следукхцим образом.

1033994

Контролируемый блок. 1 имеет и вы= водов для подключений при контроле, каждый из которых может быть входом или выходом, Разделение выводов на входы и выходы осуществляют элементы 7, соединяя выходы регистра 5 с входами блока 1 или отключая выходы регистра .,5 от входов блока

1 по сигналам блока 2 управления.

Первый блок 3 памяти, авыполненный обычно в виде перестраиваемого штеккерного или тумблерного наборного поля, содержит тестовые слова, пред» ставляющие собой совокупность 1 и 0, собтветствующие входным наборам и эталонным выходньж реакциям блока 1. Проверка осуществляется путем сравнения на элементах б выходной реакции эталонного .блока, записанной в ;блоке 3 памяти,с реакцией контролируемого блока 1.

Перед йроверкой блок 2 выдает команду, по которой устанавливает триггер 9 в нулевое состояние, и этим запрещает прохождение импульсов с генератора 8 через элемент

10 И на счетчик 11.Эта же команда выбирает .в .блоке 3 первое тестовое слово, включает перфоратор 16 и выключает считыватель 18. Одновременно с этим блок 2 переводит элементы 7 в положения, соответствую.щие входам или выходам блока 1.

По сигналу "Запись блок 2 выводит первое тестовое слово из блока 3 памяти в блок 4.. Информация первого тестового слова с выхода. блока 4 поступает на первые входы элементов

И 13, которые закрыты по вторьм входам сигнала с дешифратора 12.

Затем по сигналу Ввод™ блок

2 устанавливает триггер.9 в единичное состояние, открывая элемент И.10 для прохождения пачки импульсов с генератора 8 на счетный вход счетчика ll и стробирующнй вход дешифратора 12. В результате дешифратор 12 на своих выходах поочередно один за другим выдает импульсные сигналы, которые стробируют элементы И 13, и последовательно разряд Яа разрядом вводит информацию первого теста из блока 4 через элементы И

13 в регистр теста 5, с выходов которого информация поступает на входы контролируемого блока 1 и элементов 6 сравнения. Импульс пере" полнения счетчика 11 устанавливает триггер 9 в нулевое положение, прекращая прохождение импульсов через элемент И 10, и производит анализ результата сравнения по элементам 6.

Этот же сигнал осуществляет .перепись информации из регистра 5 в буферный регистр 14 и перфорацию перфоратором 16 регистра 14, прошедшей предварительно преббразование в первом преобразователе 15 кодов. Закодированная информация первого теста заносится во второй блок 17 памяти .на перфоленту.

В случае, если выходная эталонная информацир регистра 5 совпадает с реакцией блока 1 во всех разрядах, элементы б через блок 2 управления выводят из блока 3 следующее прове10-,рочное слово и т.д., пока блок

1 не будет проверен полностью. При этом с помощью блоков 14-16 на перфоленте записывается полная проверяющая программа 1. При невравнении хотя бы на одном из элементов б блок 2 выдает на блок 4 запрещающий сигнал, останавливая этим проверку. Останов связан либо с неисправностью блока l, которая

2р устраняется, либо требует коррекции программы, записанной в блоке 3

-и повторного ее прогона.

35. -Перед работой по второму циклу контроля блок 2 выдает команду, которая устанавливает триггер 9 в нулевое положение, запрещая прохождение импульсов с генератора 8. Эта

4 же команда, дешифрованная в блока

3 18 и 16, отключает первый блок

3 памяти от магистрали, включает перфоратор 16 и включает считыватель .18. В результате на входах блока 4 записи устанавливается информация о первом тесте, выведенная с перфоленты блока 17 считыватель 18 и преобразованная вторым преобразователем кодов 19. По сигналу Запись блок

2 выводит первое тестовое слово из

5 блока 19 в блок 4 и далее аналогич- i ио тому, как в первом цикле, с той лишь разницей, что информация об очередном тесте .выводится не из первого блока 3 памяти, а из второго — 17; В результате выполнения второго цикла проверки осуществляется контроль перфоленты, выполненной на этапе первого цикла.

Изготовленная и проверенная таким

55 образом перфолента может теперь быть использована для контроля других изфвлий данного типа, причем проверку на устройстве в этом случае можно вести без первого цикла, а только иа втором. бО

После устранения всех ошибок

25;перфоленты заканчивается первый цикл, в результате которого на перфоленте записывается полностью отработаня йая контролирующая, программа. Возмож- ные ошибки, возникавшие в процессе перфорации, будут проконтролированы на втором цикле контроля, который проводится сразу же после окончания первого цикла.

1033994 составитель В. Дворкин

Техред Ж.Кастелевич Корректор-О.Билак

Редактор В.Пилипенко

Эаказ 5619/49 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ПЙП Патент, г. Ужгород, ул, Проектная, 4

Г Таким образом введение блокбв 14-19 позволяет устранить ошибки в перфоленте до проведения контроля, сократить число остановов при контроле из-эа неверной перфоленты и этим повысить быстродействие устройства контроля.