Генератор серий прямоугольных импульсов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК уд) Н 0 3 К 3/64

ОПИСАНИЕ ИЗОБРЕТЕНИЯ .

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3425565/18-21 (22) 25..02. 82 (46) 07..08.83. Бюл. Р 29 (72). В.В.Барашенков, К.К.Князев,,Г.В.Липинский, Ю.T.Ìèíêåâè÷, Л.Г.Теницкий и A.O.Tèìîôååâ

Г53) 621 ° 344 ° 5(088 8) (56) 1. Авторское свидетельство СССР . Р 705650 кл. Н 03 К 3/64, 25.12.79, 2. Авторское свидетельство СССР

В 817993, кл. Н 03 К 3/64, 30.03.81. (.54)(57) ГЕНЕРАТОР СЕРИЙ ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ, содержащий задающий . генератор, блок настройки, двухвходовый элемент И, первый и второй делители частоты, триггер,,выход которого соединен с первым входом элемента И, а входы настройки делителей частоты подключены к выходу блока настройки, отличающийся

:тем, что, с целью расширения функ: цйональных возможностей генератора, в Него введены блок опорных частот, вход которого подключен. к выходу задающего генератора, дополнительный триггер, первый блок цифровой задержки, выход которого соединен с R -входом дополнительного триггера, элемент

ИЛИ, соединенные последовательно вто.рой блок цифровой задержки и дели„„SU„„1034160 A тель частоты с подстройкой фазы, выход которого подключен. к первому входу второго делителя частоты и к второму входу элемента И, выход второго блока цифровой задержки подклю" чен к установочному входу второго делителя частоты и к S --входу триггера, Р -вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом второго делителя частоты, выход элемента И соединен с S-ходом дополнительного триггера и с установочным входом первого блока цифровой .задержки, установочный .вход второго блока цифровой задержки соединен с выходом первого делителя частоты, выходы блока опор- PQ ных частот подключены к входам перво го и второго блоков цифровой задержки, к входу первого делителя частоты, и к входу делителя частоты.с подст- С .ройкой Фазы, установочный выход блока настройки подключен к входам началь- Я

М ной установки первого делителя частоты, обоих блоков цифровой задержки и К второму входу элемента ИЛИ, а выход блока настройки подключен к входам настройки блока опорных частот, обоих блоков цифровой задержки и делителя частоты с подстройкой

Фазы.

1034160

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств для генерирования серий импульсов программируемой длительности и скважности.

Известно устройство для формирования серий импульсов, содержащее задающий генератор, вентили, управляемый триггером счетчик с переменным коэффициентом счета, позволяющее изменять число импульсов в пачке (1).

Недостатком устройства является невозможность регулировки паузы между сериями импульсов.

Наиболее близким по технической 15 сущности к предлагаемому является генератор, который содержит задающий генератор, блок настройки, двухвходовый элемент И, первый и второй делители частоты, триггер, выход кото- 20 рого соединен с первым входом элемента И, а входы настройки делителей частоты подключены к выходу блока настройки. Устройство позволяет регулировать число импульсов в серии Я5 и паузу между сериями $2 j.

Недостатком данного устройства является невозможность регулировки начальной задержки и регулировки периода следования импульсов при со- 30 хранении периода повторения серий, что ограничивает функциональные воз- . можности устройства.

Цель изобретения — расыирение функциональных воэможностей генератора.. 35

Поставленная цель достигается тем, что в генератор, содержащий задающий генератор, блок настройки, двух входовый элемент .И, первый и второй делители частоты, триггер, выход ко- 40 торого соединен с первым входом эле" мента И, а входы настройки делителей частоты подключены к выходу блока настройки, введены блок опорных частот, вход которого подключен к выходу задающего генератора, дополнительный триггер, первый блок цифровой задержки, выход которого соединен с Й-входом дополнительного триггера, элемент ИЛИ, соединенные последовательно второй блок цифровой задержки и делитель частоты с подстройкой фазы, выход которого подключен к первому входу второго делителя частоты и к второму входу элемента И, выход второго блока цифро- 55 вой задержки подключен к установочному входу второго делителя частоты и к 9 -входу триггера, Р -вход которого соединен с выходом элемента ИЛИ, первый вход которого соеди- 60 нен с выходом второго делителя частоты, выход элемента И соединен с -входом дополнительного триггера и с установочным входом первого блока цифровой задержки, установочный 65 вход второго блока цифровой задержки соединен с выходом первого делителя частоты, выходы блока опорных частот подключены к входам первого и второго блоков цифровой задержки, к входу первого делителя частоты и к входу делителя частоты с подстройкой фазы, установочный выход блока настройки подключен к входам начальной установки первого делителя частоты, обоих блоков цифровой задержки и к второму входу элемента ИЛИ, а выход блока настройки подключен к входам настройки блока опорных частот, обоих блоков цифровой задержки и делителя частоты с подстройкой фазы.

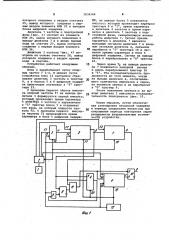

На фиг. 1 изображена схема генератора серий прямоугольных импульсов; на фиг. 2 — схема блока цифровой задержки; на фиг. 3 — схема делителя частоты. с подстройкой фазыу на фиг. 4 - схема делителя частоты; на фиг. 5 - временные диаграммы работы устройства.

Устройство (фиг, 1 ) состоит из генератора 1 задающей частоты, блока 2 опорных частот, .первого 3 и второго 4 делителей частоты, первого 5 и второго 6 блоков цифровой задержки, делителя 7. частоты с подстройкой фазы, элемента ИЛИ 8, триггеров 9 и 10, элемента И 11 и блока

12 настройки, Генератор задающей частоты подключен к входу блока 2 опорной частоты,,выходы которого подключены к одним из входов, делителя 3, блока

5 цифровой задержки, делителя 7, блока 6 цифровой задержки. Установоч-. ный выход блока 12 настройки подключен к .входам 13-15 начальной установки делителя 3 И блоков 5 и 6. Выходы параметров блока 12 подключены соответственно к входам 16-20 делители 3, делителя 4 блоков 5 и 6, делителя 7 и к входу блока 2 опорной частоты. Выход делителя 3 соединен с другим входом блока 5, выход которого соединен с входом делителя:

7, c B -входом дополнительного триггера 9 и с установочным входом делителя 4. Выход делителя 7 соединен с первым входом элемента И 11 и входом делителя 4, выход которого соединен с входом элемента ИЛИ 8, выход которого соединен с К -входом триггера 9, единичный выход которого соединен с вторым входом элемента И 11, выход которого соединен с входом 21 блока 6 и 5-входом триггера 10.

Каждый блок задержки фиг. 2) содержит элемент ИЛИ 22, выход которого соединен с К-входом триггера 23, единичный выход которого соединен с первым входом элемента И 24, выход

1034160 которого соединен с входом счетчика

25, ° "выход которого соединен с первым вхОдом элемента ИЛИ 22 и выходом блока цифровой задержки.

Делитель 7 частоты с подстройкой фазы (фиг. 3) состоит из элемента

ИЛИ 26, выход которого подключен к выходу делителя 7 и к входу приема кода на счетчик 27, выход которого .соединен с первым входом элемента

ИЛИ 2 6 .

Делитель 3 частоты (фиг. 4) по строен на основе счетчика 28, выход которого соединен с входом приема кода в счетчик. . Устройство работает следующим образом ..

Блок 2 вырабатывает сетку опор-. ных частот F 1-4. В момент пуска устройства блок 12 настройки сбрасывает делитель 3 частоты и триггер:

9, а в блоках 5 и 6 цифровой задержки нроиэводит установку в "О" триггера 23.

С приходом .первого сброса импульса опорной частоты Н на выходе делителя 3 форьяруется первый импульс, который производит прием параметра в делитель 3 частоты и переключает в "1" трйггер блока 5 и открывает его вход, на который подается частота Р2. С приходом первого импульса частоты F2 производится прием параметра а блок 5 цифровой задерж 3% на выходе блока 5 появляется импульс;. который производит переброс триггера 9 в "1", прием параметра в делитель 4 частоты и прием параметра в делитель 7 частоты с подстройкой фазы, сннхронизируя начало работы делителя 7. Сигнал приема параметра в делитель 2 является выходным сигналом делителя 7 и входным сигналом делителя 4, сигналом

10 переброса в "1" триггера 10 и сигналом приема параметра в блок 6 цифровой задержки. Сигнал на выходе блока 6 перебрасывает в "0" триггер

10.

15 Через время То на выходе делителя 7 появляется выходной сигнал и вновь перебрасывает триггер 10 в "1". Эта последовательность продолжается до того момента, когда .@ на выходе делителя 4, отсчитывающего количество импульсов в серии, не появится сигнал и не перебросит в "О" триггер 9;

После появления сигнала ц на выходе делителя 3 описанная последовательность повторяется (фиг. 5).

Таким образом, путем обеспечения регулировки начальной задержки и периода следования импульсов при сокращении периода повторения серии расширяются функциональные воэможности устройства.

fg

4Ы У

4МФ

ВНИИПИ . Заказ 5642/58 Тираж 936 Подписное

Филиал ППП "Патент", г.Ужгород, ул. Проектная, 4