Преобразователь кода в частоту

Иллюстрации

Показать всеРеферат

СОЮЗ COBETGHHX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (292 «22

З(52) Н 03 К 13 20

ОПИСАНИЕ ИЗОБРЕТ с р у

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К ABT0PCH05hY СВИДЕТЕЛЬСТВ,К (21) 3426194/18-21 (22) 16.04.82 (46) 07.08.83. Бюл. Р 29 (7 . В,В.Клименко, В.А.Гаманко и С.Л.Сироткин (71) Таганрогский радиотехнический .институт им, В.Д.Калмыкова

"(53) 621.317(088.8) (56) 1. Авторское свидетельство. СССР. Nt 360717, кл. Н 03 К 13/02, 1972.

2. Авторское свидетельство СССР

9 744977., кл. Н 03 К 13/20, 1980 ° (54)(.57) ПРЕОБРАЗОВАТЕЛЬ КОДА В

ЧАСТОТУ содержащий регистр мантиссц» выход которого соединен с информационным входом накапливающего сумматора, выход переполнения которого соединен через инвертор с первым входом первого ключа и непосредственно с первым входом второго ключа, а вторые входы ключей соединены соответственно с .пряжим и инверсным выходами триггера знака мантиссы и регистр порядка, о т л и ч а юшийся тем, что, с целью расиаирения функциональных возможностей устройства, в него -введены дешифратор, генератор и дополнительный на,капливающий сумматор, причем инверсный выход триггера знака порядка соединен с первым входом дешифратора, :к второму входу которого подключен выход регистра порядка, а выход дешифратора соединен с информационным входом дополнительного накапливаю.:щего сумматора, выход переполнения которого соединен с управляющим вхо- Е

Ф дом основного накапливающего сумма- .

:тора, при этом выход генератора соединен с управляющим входом дополнительного накапливающего сумматора.

1034175

Изобретение относится к импульсной технике и может быть использовано для связи вычислительной машины с внешними устройствами, в системах управления и моделирования, а также в измерительных системах.

Известен преобразователь частоты в код, содержащий генератор импульсов эталонной частоты; регистр преобразуемых величин, диодный дешифратор и логическую схему ИЛИ, причем вход счетчиков импульсов эталонной частоты соединен с генерато.ром импульсов эталонной частоты, выходы счетчика импульсов эталонной частоты и регистра преобразуемых 15 величин подключены к входным шинам дешифратора, выходные шины которого соединены с логической схемой ИЛИ, соединенной обратной связью с входом

"Сброс" счетчика импульсов эталонной частоты j1g.

Недостатком указанного преобразователя является невозможность преобразования числа, представленного в форме с плавающей запятой, в час- 25 тоту.

Наиболее близким к предлагаемому является преобразователь частоты в код, содержащий распределитель импульсов, первый и второй выходы 30 которого соединены с первыми входами первого и второго коммутаторов соответственно, к вторым входам которых подключен выход регистра суммы, выход первого коммутатора через по- З5 следовательно соединенные первый инФормационный регистр и третий коммутатор подключен к первому входу комбинационного сумматора, выход второго коммутатора через последовательно соединенные второй информационный регистр и четвертый коммутатор подключен к второму входу комбинационного сумматора, выход котоРого соединен с входом регистра сум 4 мы, третий и четвертый выходы распределителя импульсов подключены к управляющим входам третьего и четвертого коммутаторов, управляющие входы первого и второго синхронизаторов соеущнены с пятым выходом распределителя импульсов, шестой выход которого подключен к управляющим входам третьего и четвертого синхронизаторов, выходы первого и третьего синхронизаторов через пер- 55 вый элемент ИЛИ подключены к третьему входу комбинационного сумматора, к четвертому входу которого через второй элемент ИЛИ подключены выходы второго и четвертого синх- 60 ронизаторов, выход коммутатора записи соединен с управляющим входом информационного регистра и входом .триггера знака, выходы которого подключены к первым входам ключей, вто- 65 рые входы которых соединены с седьмым выходом распределителя импульсов, к первому входу которого подключен прямой выход триггера режима, выход разряда переполнения регистра суммы подключен через инвертор к третьему входу первого ключа и непосредственно к третьему входу второго ключа Р 23 °

Недостаток известного преобразователя состоит в невозможности преобразования числа .в форме с плавающей запятой в частоту.

Цель изобретения — расширение функциональных возможностей, а именно преобразование дополнительного кода числа с плавающей запятой в частоту.

Поставленная цель достигается тем, что в преобразователь кода в частоту, содержащий регистр мантиссы, выход которого соединен с информационным входом накапливающего сумматора, выход переполнения которого соединен через .инвертор с первым входом первого ключа и непосредственно с первым входом второго ключа, а вторые входы ключей соединены соответственно с прямым и инверсным выводами триггера знака мантиссы, и регистр порядка, введены дешифратор, генератор и дополнительный накапливающий сумматор„ причем инверсный выход триггера знака порядка соединен с первым входом дешифратора, к второму входу которого подключен выход регистра порядка, а выход дешифратора соединен с информационным входом дополнительного накапливаю» щего сумматора, выход переполнения которого соединен с управляющим входом основного накапливающего сумматора, при этом выход генератора соединен с управляющим входом дополнительного накапливающего сумматора.

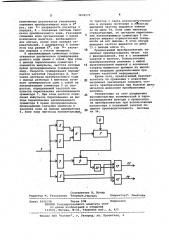

На чертеже приведена структурная схема предлагаемого преобразователя.

Преобразователь содержит входную, шину 1, триггер 2 знака порядка, регистр 3 порядка, регистр 4 мантиссы-, триггер 5 знака мантиссы, дешифратор б, накапливающий сумматор 7, генератор 8, накапливающий сумматор 9, инвертор 10, первый 11 и второй 12 ключи и выходные шины 13 и 14.

Преобразователь работает следующим образом.

Число подлежащее преобразованию,, записывается по шине 1 в триггер 2 знака порядка регистр 3 порядка, регистр 4 мантиссы и триггер 5 знака мантиссы. Сигнал с инверсного выхода триггера 2 знака порядка подается на старший входной разряд дешифратора 6, на младшие разряда которого подаются сигналы со всех выходов регистра 3 порядка. Таким

1034175

Составитель В. Иуляр

Редактор М. Рачкулинец ТехредМ.ГЕргель Корректор Г. Решетник

Заказ 5642/58 Тираж 936 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35., Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 включением достигается увеличение значения преобразующего кода и К"раз, где И = разрядность регистра 3 порядка, К - основание системы счис.ления преобразуемого кода. Указанное смещение кода организовано с целью исключения делителя, необходимого для случая, когда знак порядка от-. рицательный. С дешифратора б снимается код равный К", где М вЂ” значе-ние порядка с учетом смещения.

В накапливающем сумматоре осуществляется циклическое суммирование данного кода самим с собой. При этом с выхода переполнения сумматора 7 снимаются импульсы., частота которых .прямо пропорциональна суммируемому коду. Скорость суммирования определяется частотой генератора 8. Значение мантиссы преобразуемого кода с выхода регистра 4 мантиссы начи- .. нает суммироваться само с собой на накапливающем сумматоре 9 со скоростью, определяемой частотой импульсОв переполнения накапливающего сумматора 7. При этом частота появления импульсов переполнения на выходе. переполнения накапливающего сумматора 9 прямо пропорциональна произведению значения мантиссы и

:значения кода на выходе дешифратора

6. Если знак мантиссы положительный то триггер 5 -знака мантиссы установ- лен в нулевое состояние и импульсы выходной частоты выдаются ключом

12.ио шине 14. Если знак мантиссы отрицательный, то сигналом переполнения накапливающего сумматора 9 является импульс отрицательной полярности на его выходе. В этом случае выходная частота выдается по шине

13 с. выхода ключа 11.

Предлагаемый преобразователь позволяет преобразовыватв число как с фиксированной; так и с плавающей запятой в частоту.- Использование преобразователя возможно с любой

15 вычислительной. машиной и исключает затраты машинного времени на выполнение операции денормалиэации при обмене частотной информацией.

Кроме того, предлагаемый преобразователь по сравнению с известным позволяет значительно повысить точность преобразования при большом динамическом диапазоне преобразуемых величин.

Изобретение за счет расширения функциональных возможностей и перераспределения функции с процессора на преобразователь при использовании процессора с плавающей запятой по- вышает. производительность системы на 5Ъ.