Пороговый элемент (его варианты)

Иллюстрации

Показать всеРеферат

1. Пороговый элекюнт, содержгоций . регистр сдвига, отличают и йС::я тем, что, с целью повышения быстродействия и сокраац ения объёма .оборудования, в него введен регистр пав«{ти, соединенный информационнь вли входами с выходами регистра .сдвига, I входы которого являются входами порогового элемента, а выходы регистра памяти - его выходами. S /Ч /

СООЗ COBETCHMX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3(59 Н 03 К 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРС ПЗЕННЦЙ КОМИТЕТ СССР

ПО ДЕЛАЯ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

21) 3000041/18-21

25) 3233914/18-21 (22) 04 11.80 (46) 07,08.83. Бюл. В 29 (72) О,Н.щузыченко и В.П.Лукоянов .(71) Ленинградский ордена Трудового .Красйого Знамени механический институт

:(533 681 ° 325 ° 65(088.83 (56) 1. Авторское свидетельство СССР

Р 683025, кл. Н 03 К 19/23,17.07.79.

2. НигвФ S.(. 0 lgltal » summation

tNresboid logic getesi.a neu circuit

element. . "РгосеейщвоФ )ЕЕ", vol 1:20, 9 Я., Moveebe r, 1973-, р.:р . 3301-1307. (прототип) . оа ВФэ A

Ф (543 ПОРОГОВЫЙ ЭЛЕМЕНТ (ЕГО ВАРИАНТЫ). (57)1 . Пороговый элемент, содержащйй регистр сдвига, о т л и ч а ю щ и й-с:..я тем, что, с целью поъиаения .быстродействия и сокращения объема

:оборудования, в него введен регистр памяти, соедйненный информационными входамй с выходами регистра сдвига, ;входы которого являются входамн порогового элемента, а выводы регистра памяти - его выходами.

1ОЗ4188

2. Пороговый элемент, содержащий регистр сдвига, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и сокращения; объема оборудования, в него введены регистр памяти и блок контроля обнуления, причем0 первых выходов регистра сдвига, где 0 -порог. . элемента, соединены с информационными входами регистра памяти, а остальные (И -a) выходов - с входами блока контроля обнуления, вход сброса регистра памяти соединен с входом разрешения записи регистра сдвига.

3. Пороговйй элемент по пп. 1 и 2, отличающийся тем, что регистр памяти содержит 0 последовательно соединенных блоков, причем

Изобретение относится к автоматике и. вычислительной технике и может быть использовано вля йостроения .различных устройств переработки дискретной информации.

Известен мажоритарный логический элемент, содержащий преобразователи весов двух входов, состоящие из элементов И и ИЛИ с параллельно соединенными входами, блок формирования порога и выходной .элемент ИЛИ.

Блок формирования порога выполнен двухступенчатым, содержащим два однотипных каскада формирования набора весов первой ступени, взаимодополняющие весовые выходы которых 15 попарно соединены с входами элементов И каскада формирования порога второй ступени Р13.

Недостатком данного устройства являются малые Функциональные воз- )Q можности, Наиболее близким к предлагаемому по технической сущности является пороговый элемент, содержащий генератор, сканирующий мультиплексор,сос- 5 тоящий из регистра сдвига, соединенного выходами с первыми входами элементов И, вторые входы которых соединены с входами порогового зле> мента, а выходы — с входами элемента ИЛЙ. Выходы мультиплексора соединены с входами счетчика, соединенного выходами с входами детектора, выход которого является выходом элемента а 2 ).

Недостатками данного устройства являются сложность технической реализации и малое быстродействие.

Цель изобретения — повышение быстродействия и сокращение объема оборудования. 4О первый вход каждого блока соединен с входом регистра памяти, а второй с вторым выходом предыдущего блока, первый выход каждого блока соединен с выходом регистра, каждый блок состоит из установочного триггера, соединенного прямым входом с выходом первого элемента И, первый вход ко,торого является первым входом блока, а второй соединен с первым входом второго элемента И данного блока и его вторым входом, второй вход второго элемента И соединен с прямым выходом триггера, являющимся первым выходом блока, а выход второго элемента И вЂ” вторым выходом блока, инверсные входы всех триггеров соединены с входом сброса регистра памятй, Для достижения поставленной цели в пороговый элемент, содержащий регистр сдвига, введен регистр памяти, соединенный информационными входами с выходами регистра сдвига, входы которого являются входами порогового элемента, а выходы регистра памятиего выходами.

Кроме того, в пороговый элемент, содержащий регистр сдвига, введены регистр памяти и блок к,нтроля обнуления, причем 0 первых выходов регистра сдвига, где Q - порог элемента, соединены с инфсрмационными входами регистра памяти, а остальные (И - О ) выходов — с входами блока контроля обнуления, вход сброса регистра памяти соединен с входом разрешения записи регистра сдвига.

Регистр. памяти содержит Cf последовательно соединенных блоков, причем первый вход каждого блока соединен с входом регистра памяти, а второйс вторым выходом предыдущего блока, первый выход каждого блока соединен с выходом регистра, каждый блок состоит из установочного триггера, соединенного прямым входом с выходом первого элемента И, первый вход которого является первым входом блока, а второй соединен . с первым входом второго элемента И данного блока и его вторым входом, второй вход второго элемента И соединен с прямым выходом триггера, являющимся первым выходом блока, а выход второго элемента И - вторым выходом блока, инверсные входы всех триггеров соединены с входом сброса регистра памяти. !

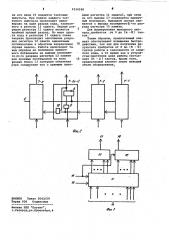

На Фиг. 1 изображена структурная схема предлагаемого элемента пер1.034188

Функционирование предлагаемого элемента в первом варианте происходит следующим образом (фиг. 1 и 2).

В исходном состоянии регистры 1 и 2 сброшены, на их выходах нулевые потенциалы. Входной код подается на входы 3 порогового элемента и записывается в- регистр 1 сдвига. Далее на вход 4 подаются тактовые импульсы.

При подаче каждого тактового импуль1О са происходит сдвиг вправо на один разряд кода, записанного в регистре 1 сдвига. При появлении единичного потенциала в первом разряде регистра 1 сдвига, являющемся крайним

15 .правым разрядом, он записывается в регистр 2 памяти и на его первом выходе появляется единичный потенциал, разрешающий запись единичного потенциала во второй разряд регист2(1 ра 2 памяти. При появлении единичного потенциала на выходе второго разряда регистра 1 сдвига он записывается в регистр 2 памяти и на его втором выходе появляется единичный

25 потенциал, разрешающий запись единич-, ного потенциала в третий разряд регистра 2 памяти. Далее работа происходит аналогичным образом.,Единичный потенциал появляется на, -м выЗо ходе регистра 2 памяти, если на всех предыдущих выходах имеется единичный потенциал и на выходе 1;-го разряда регистра 1 сдвига также имеется еди- иичный потенциал, одновременно раз-, решается запись единичного потенциа-

З5 ла в (Л +1)-й разряд регистра 2 па-; мяти. Таким образом, в процессе

Функционирования сдвиг входного кода в регистре сдвига производится сле- ва направо, а заполнение регистра 2

40 памяти - справа налево.

Через (И -C3) тактов входной сигнал, соответствующий последнему раз- ряду входного кода, появляется на выходе с номером <б. регистра 1 сдви45 га. Сигнал на выходе последнего, ф-го разряда регистра 2 памяти в этот момент и далее соответствует разультату работй устройства. Он является единичным потенциалом, если число единиц во,входном)коде было больше или равно noporyg элемента, и нулевым потенциалом в противном случае.

55 бО

65 вый вариант; на фиг. 2 - схема регистра памятй, на фиг. 3 - структурная схема предлагаемого элемента второй вариант

Предлагаемый элемент (фиг. 1) состоит из регистров 1 и 2 сдвига и памяти. Установочные входы регистра 1 сдвига соединены с информацион ными входами 3 порогового элемента, а его вход сдвига - с входом 4 порогового элемента. Первые 0 выходов регистра 1 сдвига (где Π— nopor) соединены с входами регистра 2 памяти, выходы которого соединены с выходами 5 порогового элемента. Вход б . сброса регистра- соединен с входом порогового элемента.

Регистр.. 2 памяти (фиг. 2) состоит из0 блоков 7-1- 7-„ 4I. Первый вход каждого блока соединен с входом регистра, а второй - с вторым выходом предыдущего блока, первый выход каждого блока является выходом регистра. Каждый блок 7-1-,: 7-О состоит из установочного триггера 8, соединенного прямым. входом с выходом элемента И 9, первый вход которого является первым взводом блока, а второй - соединен с.первым входом элемента И 10. Второй вход элемента И 10 соединен с прямым выходом триггера 8 и первым выходом блока.

Инверсные выходы всех триггеров 8 соединены с входом б сброса регистра: памяти. Предлагаемый элемент во втором варианте (фиг. 3) состоит из регистра 11 сдвига, регистра 12 памяти и блока 13 контроля обнуления. Установочные входы регистра 11 сдвига соединены с информационными входами 14 порогового элемента, имеющего вход 15. Вход сброса регистра 12 памяти соединен с входом разрешения записи регистра-11 сдвига и входом 16 регистра 11. Вход сдвига регистра 11 соединен с входом 15 порогового элемента, выходами которого являются выход 17 блока 13 контроля обнуления и выход 18 последнего разряда регистра 12 памяти. Первые

@, выходов регистра 11 сдвига (первым выходом. является выход крайнего правого разряда регистра сдвига)1 соединены с входами регистра 12 памяти, а остальные (!11 - 60 выходовс входами блока 13 контроля обнуления. Первым разрядом регистра 12 памяти является крайний правый разряд.

Блок 13 контроля обнуления может быть выполнен в виде элемента И с прямыми входами, если он соединен с инверсными выходами регистра 11 сдвига, и в виде элемента И с инверсными входами, если он соединен с прямыми выходами регистра 11 сдвига, Таким образом, для Формирования выходного сигнала требуется (И - 0 ) тактов работы устройства.

Функционирование предлагаемого элемента во втором варианте (фиг.3) происходит следующим образом.

На вход 16 регистра 11 подается импульс запуска, при поступлении которого происходит сброс регистра 12 памяти и запись в регистр 11 сдвига входного кода, поступающего на входы 14 порогового элемента. Далее.

1034188 на его вход 15 подаются тактовые импульсы. При подаче каждого тактового импульса происходит сдвиг вправо на один разряд кода, записанного в регистр 11 сдвига. Первым разрядом регистра 11 сдвига является крайний правый разряд. По мере сдви;га кода в регистре 11 сдвига слева направо происходит заполнение разрядов, регистра 12 памяти единичными потенциалами в обратном направлении справа налево. Работа происходит та ким образом до появления единичного потенциала на выходе последнего;0-ro разряда регистра 12 памяти или нулевых потенциалов на всех входах блока 13 контроля обнуления (при соединении его с прямыми выхоВНИИПИ Заказ 5643/59

Тираж 936 Подписное

Филиал ППП "Патент", г.Ужгород,ул.Проектная,4 дами регистра 11 сдвига)., при этом на его выходе 17 появляется единичный потенциал. Выходной сигнал снимается с выхода последнего4 -ro разряда регистра 12 памяти.

Для формирования выходного сигнала требуется..:от 0 до (4 -Й) тактов.

Таким образом, предлагаемый элемент обеспечивает повышение быстродействия, так как для получения результата требуется от 0 до (Й - 0 ) тактов работы в зависимости от входного кода, в то время как в устрой-: стве-прототипе цикл работы состав15 ляет (И - 2 ) тактов. Кроме того, предлагаемый элемент имеет меньший объем оборудования.