Управляемый махоритарный элемент на комплементарных мдп- транзисторах

Иллюстрации

Показать всеРеферат

УПРАВЛЯЕМЫЙ МАЗКОРИТАРНЫЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ MOT-TPAH-iЭИСТОРАХ , содержащий первую ветвь, включенную Между шиной питания и выходной шиной и состоящую из последовательно включенных первого и второго транзисторов, при этом параллельно первому транэ1нстору (чен. третий, транзистор, вторую ветв, включённую между выходной шиной и общей и состоящую из последовательно включенных четвертого и пятого транзисторов, при этом пятрму транзистору параллельно подключен шестой транзистор, третью ветвь,. состоящую из последовательно включенных транзистордв седьмо гр, восьмого и девятого, параллельно крторсхиу подключен десятый транзистрр , и четвертую , состоящую из последовательно включенных одиннадцатого, двенадцатогоИ т;рит надцатого транзисторов и четырнад цатого транзистора, подключенного па раллельно тринадцатому, причем затворы второго, четвертого, десятого и четырнадцатого транзисторов подключены к п ервой информационной шине, затворы первого, пятрго, девятого , тринадцатого транзисторов 9 к второй информационной шине, затворы восьмого и двенадцатогр - к третьей информсщионнбй шине, затворы третьего и одиннадцатого - к прямому управляющему, входу, а затворы шестого и седьмого - к инверсному утфавляющему входу, р т л и ч а ющ и и с я тем, что, с целью повышения быстрюдействия, истоки девятого и десятого транзисторов подключены к шине питания, тринадцатого и чеоо тьфиадцатого - к общей шине, а 1 стоки седьмого и одиннадцатого - к выходной ишне. со

. СОЮЗ СОВЕТСНИХ

53WI

РЕСПУБЛИН .

МШ Н 03 К 19 23

Ь

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМЪ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОВРЕЧ ЕНИЙ И ОТНРЫТИЙ (21) 3424487/18-21 (22) 15.04лг (46). 07.08.83. Бюл. 9 29 (72).С.Н. Косоусов, В:.A. Максимов и Я.Я. Петричкович (53) 621.374(088.8) (56) Ильюшенко Ю.М. Микромощные цифровые интегральные схеьаа на основе дополняющих ИОН-транзисторных структур. - Обзоры по электронной техни-. ке,, Сер. Микроэлектроника., вып. 5 (202). М., "Электроника", 1970, а; 26, рис.8а.

2. Авторское свидетельство СССР па заявке 9 3322239/18-21, .кл. Н 03 К 19/42, 1981.

{ 54) (57) УПНаЛЯЕМЫй МАжоРИТАРНЫй

ЭЛЕМЕНТ НА КОМПЛЕИЕНТАРНЫХ МДП-ТРАН-.

ЗИСТОРАХ, содержащий первую ветвь, включенную Между шиной питания и выходной шиной.:и состоящую as последовательно .включенных первого ,и второго транзисторов, при этом .параллельно первому транзистору подключен третий.транзистор, вторую ветвь „ включенную между выходной шиной и общей и состоящую иэ последовательно включенных четвертого и пятого транзисторов, при этом пя,SUÄÄ 1 А тому транзистору параллельно подключен-шестой. транзистор, третью ветвь,. состоящую из последовательно включенных транзисторов седьмо-. го, восьмого и девятого, параллельно которому подключен десятый трав» зистор, -и четвертую вепрь, состоящую из последовательно включенных одиннадцатого„ двенадцатого и три-. надцатого транзисторов и четырнад.-цатого транзистора, подключенного параллельно тринадцатому, причем затворы второго, четвертого,.деся- того и четырнадцатого транзисторов подключены к первой информационной шине, затворы первого, пятого, девятого, тринадцатого транзйсторов - Я к второй информационной шине, затво ры восьмого и двенадцатого - к третьей информационной шийе, затвори . третьего и одиннадцатого - к прямому управляющему. входу, а затворы шестого.и седьмого - к инверсному д управляющему входу, о т л и ч а юшийся тем, что, с целью повыше-" ния быстродействия, истоки девятого и десятого транзисторов подключены к шине питания, тринадцатого и четырнадцатого - к общей шине, а стоки седьмого и одиннадцатого - к выходной шине.

1034191

Изобретение относится к вычисли тельной технике и электронике и может быть использовано при построении многоканальных вычислительных систем, в частности для поканального разделения системы, например, в режиме проверки работоспособности каждого канала мажоритарно-резервированной системы.

Известен мажоритарный элемент на комплементарных МДП-транзисторах, содержащий ключевую часть, состоящую из первой ветви, образованной двумя последовательно включенными транзисторами, и второй, включенной параллельно первой и образованной двумя последовательно включен.ными транзисторами, параллельно одному из которых подключен третий транзистор, а также нагрузочную

:часть, симметричную ключевой P1).

Недостаток устройства состоит в том, что его нельзя использовать при построении многоканальных систем, работающих в режимах поканального разделения.

Известен также управляемый мажоритарный элемент на комплементарных

МДП-транзисторах, содержащий первую ветвь,, включенную между шиной питанйл и выходной шиной и состоящую из последовательно включенных первого и второго транзисторов, при этом параллельно первому транзистору подключен третий транзистор, вторую ветвь, включенную между выходной шиной и общей и состоящую из последовательно включенных четвертого и пятого транзистора, параллельно которому подключен шестой транзистор, третью ветвь, состоящую из последовательно включенных транзисторов седьмого, восьмого и денятого, параллельно которому подключен десятый транзистор, и четвертую ветвь, состоящую из последовательно включен ных одиннадцатого, двенадцатого", тринадцатого транзисторов и четырнадцатого транзистора, подключенно» го параллельно тринадцатому, причем затворы второго, четвертого, десятого и четырнадцатого, транзисторов подключены к первой информационной шине, затворы первого, пятого, десятого и тринадцатого транзисторов — к второй информационной шине, затворы восьмого и двенадцатогок третьей информационной шине, затворы третьего и одиннадцатогок прямому управляющему входу, затво,ры шестого и седьмого — к инверсному управляющему входу, стоки девятого, десятого, тринадцатого и четырнадцатого транзисторов - к выходной шине, а истоки седьмого и одиннадцатого — соответственно к шине питания и общей шине $2).

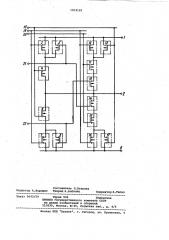

На чертеже представлена электрическая принципиальная схема управляемого мажоритарного элемента на комплементарных МДП-транзисторах, где первая ветвь,. включенная между шиной 1 питания и выходной шиной 2, содержит последовательно включенные первый и второй Р --канальные транзисторы 3 и 4, при этом параллельно транзистору 3 подключен третий » -канальный транзистор 5.

Вторая ветвь содержит последовательно включенные И -канальные чет-. вертый и пятый транзисторы б и 7 и шестой h-канальный транзистор 8, подключенный параллельно пятому транзистору 7, и включена между выНедостатком элемента является низкое быстродействие, обусловленное большой паразитной емкостью выходной шины, образуемой стоками шести

МДП-транзисторов.

Цель изобретения — повышение быстродействия управляемого мажори- тарного элемента..

Для достижения поставленной цели в управляемом мажоритарном элементе на комплементарных МДП-транзисторах, содержащем» первую ветвь, включенную между шиной питания и выходной шиной и состоящую из последовательно включенных первого и второго

35 транзисторов, при этом параллельно первому транзистору подключен третий транзистор, вторую:ветвь, вклю-; ченную выходной шиной и общей и состоящую из последовательно включенных четвертого и пятого транзистора, при этом параллельно пятому транзистору подключен шестой транзистор, третью нетвь, состоящую из последонательно включенных тран«

75 зисторов седьмого, восьмого и девятого, параллельно которому подключен десятый транзистор, и четвертую ветвь, состоящую из последовательно включенных одиннадцатого, двенадцаЗ0 того, тринадцатого транзисторов и четырнадцатого транзистора, подключенного параллельно тринадцатому, причем затворы второго, четвертого, десятого и четырнадцатого транзисторон подключены к первой информационной шине, затворы первого, пятого, девятого, тринадцатого транзисторов — к второй информационной шине, затворы восьмого и двенадцатого — к третьей информацион40 ной шине, затворы третьего и одиннадцатого — к прямому управляющему входу, а затворы шестого и седьмого к инверсному управляющему входу, истоки девятого и десятого транзис45 торов подключены к шине питания, трйнадцатого и четырнадцатого — к общей шине, а стоки седьмого и один1 надцатого — к выходной шине.

1034191 ходной шиной 2 и общей шиной 9.

Третья ветвь содержит последовательно .включенные седьмой, восьмой и девятый Р -канальные транзисторы

10-12. Параллельно транзистору 12 подключен десятый Р -канальный транзистор 13. Истоки транзисторов 12 и 13 подключены к шиве питания 1, сток транзистора 10 — к выходной шиче 2.

Четвертая ветвь содержит последовательно включенные одиннадцатый, двенадцатый, тринадцатый р --канальные транзисторы 14-16 и четырнадцатый. и -канальный транзистор. 17, подключенный параллельно транзистору 16. Истоки транзисторов 16 и 17 подключены.к общей шине 9, а сток .транзистора 14 - к выходной шине 2.

° . Затворы транзисторов 4, 6, 13 и 1.7 подключены к первой информационной шине 18„ затворы транзисторов.

3,7,12 и 16 - к второй информацион. ной шине. 19, затворы транзисторов

11 и 15 — к третьей информационной шине 20, затворы транзисторов 5 . и 14 - к прямому управляющему входу 21, а затворы транзисторов 8 и 10к инверсному, управляющему входу 22..

Управляемый мажоритарный элемент работает следующим образом.

При поступлении логической "1" на прямой управляющий вход 21 и логического "0" на инверсный управляющйй вход 22 элемент выполняет функцию мажоритования. Логический

"0" на первой 18 и второй.19, либо на первой 18 и третьей 20, либо на второй 19 и третьей 20;.либО на всех трех информационных шинах инициирует ° ,заряд выходной шины 2 до уровня логической "1" через открытые МДПтранзисторы соответственно 3,4, либо 10,11,13, либо 10, 11, 12, либо через все МДП-транзисторы с каналами -типа, кроме транзистора 5. . Логическая "1" на первой 18 и второй 19, либо на первой 18 и третьей

20, либо на второй 19 и третьей 20, либо на всех трех информационных шинах инициирует заряд шины 2 элемента до уровня логического "0" через открытые МДП транзисторы со,ответственно 6,7 либо 14, 15, 17, либо через все МДП-транзисторы с каналами . И -типа, кроме транзистора 8. .При поступлении логического "0"

" на прямой 21 и логической "1" на инверсный 22 управляющие входы открываются транзисторы 5 и 8 и закрываются транзисторы 10 и 14, в результате чего выходным сигналом является инверсированный сигнал, <ц поступающий на первую информацион.ную шину 18.

Положительный эффект при использовании предлагаемого элемента .заключается в том, что уменьшение

15 величины паразитной емкости, образуемой стоками транзисторов, подключенных к выходу элемента, обесйечивает возможность построения быстродействующих многоканальных мажо2О ритарно-резервированных устройств..

Время заряда паразитной емкости, на выходе элемента,в общем случае выражено функцией

В wl (=К14) ССор, ЕЖ р+ссм ™4и 31 где К вЂ” коэффициент пропорциональности, 1() - ток заряда выходной емкости элемента;

С t: - удельные емкости диффузионных областей. МДП-транзис ОИ торов с каналами р и И

-типа соответственно, g. y. — ширины стоковых областей

35 " "" МДП-транзисторов с каналами

Р- и И-типа соответственно, подключенных к выходу элемента, Е ур- число стоковых областей

4Q МДП-транзисторов с каналами Ь - и 0=типа соответст" венно, подключенных к выходу элемента.

Выходная емкость известного эле45 мента образована тремя стоками транзисторов с каналами р -типа и тремя стоками транзисторов с каналами

В-типа. У предлагаемого элемента параметры 9 и N равны 2, что обеспечивает со р щение времени заряда выходной емкости на ЗОВ.

1034191

Ю

/У

2д

Составитель Л.Петрова

Редактор A ..Ворович Техред А,Бабинец Корректор А яско

Заказ 5643/59 Тираж 936 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4