Устройство для умножения

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее регистры множимого, множителя и произведения, матрицу блоков умножения и суммирующий блок, причем первые входы блоков умножения каждой строки матрицы соединены с выходами :соответствующих тетрад регистра множимого ,вторые входы блоков умножения ка у1ого столбца матрицы соеди нены с выходами соответствуквдих.тетрад регистра множителя, выходы суммирующего блока соединены со входами регистра произведения, отличающеес я тем, что, с целью сокращения количества оборудования при перемножении двоично-десятичных чисел, сумми- . рующий блок содержит двояч1ные сумма торы, преобразователи двоичнога кода в двоично-десятичный и двоично-десятичный сумматор, причем входы К-го двоичного сумматора (К. 1,.. ,м+№-3; М- число десятичных разрядов , множи мого. И- число десятичных разрядов множителя) соединены с выходами i-х блоков умножения j -х строк матрицы (, ...N;J 1,..., /Л; 1+ j.lt-2), .выходы первого блока умножения первой матрицы, двоичных сумматоров с первого по (М+М-3)-й и N-ro блока умножения строки матрицы соединены со входами преобразователей двоичного кода в двоично-десятичный с первого ito (Н+ЛЛ-1)-й соответственно, выход преобразователя двоичного кода в двоично-десятичный § (р ,..,,; 6- число выходов данного i преобразователя двоичного кода в ДВО-1/Л ично-десятичный, ( ,..., N+ АЛ-1)со- 1,, единен-со вхсГдом ( р + с), -2)-го разряпС, да двоично-десятичного сумматора, I первый выход первого, преобразователя Н двоичного кода в двоично-десятичный и выходы разрядов двоично-десятичного сумматора являются выходами суммирующего блока. сл 3t

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ . РЕСПУБЛИН

3(59 606 Г. 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ1

Ъ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21)- 3321308/18-24 (22) 24.07.81 (46) 15.08.83. Вюл. 9 30 (72) Г.Г; Калиш (53) 681.325(088.8) (56) 1.Патент США 9 3890496, кл. 606F 7/52) опублик. 1975.

2. Авторское свидетельство СССР

Ф729587)кл ° G 06 F 7/52,1977(прототип) ° (54).(57) УСТРОИСТВО ДЛЯ УМНОЖЕНИЯ) содержащее регистры множимого, множителя и произведения, матрицу блоков умножения и суммирукщий блок, причем первые входы блоков умножения каждой строки матрицы соединены с выходами .:соответствующих тетрад регистра множимого,вторые входы блоков умножения каждого столбца матрицы соединены с выходами соответствующих.тетрад регистра множителя, выходы суммирующего

- блока соединены со входами регистра произведения, о т л и ч а ю щ е ес я тем, что, с целью сокращения ко. личества оборудования при перемножении двоично-десятичных чисел, сумми- . рующий блок содержит двоичные сумма. торы, преобразователи двоичного, кода

s двоично-десятичный и двоично-десятичный сумматор, причем входы K --го двоичного сумматора (K.=l)...é+é- 3; й-- число десятичных разрядов ..множимого, й- число десятичных разрядов множителя) соединены с выходами i --x блоков умножения j -х строк матрицы (11)...й; j =1)...) p; . + j =.% -2), .выходы первого блока умножения первой матрицы, двоичных сумматоров с первого по (М+М-3)-й и 8-ro блока умножения М-й строки матрицы соединены со входами преобразователей двоичного кода в двоично-десятичный с.

nepsora по (К+М-1)-й соответственно, p@N выход q-го преобразователя двоичного кода в двоично-десятичный е (p =l,...,Ру Р- число выходов данного преобразователя двоичного кода в дво-) ично-десятичный, ф ®1,... ) й+ М-1) соединен со входом (p + j, -2)-го разря- С да двоично-десятичного сумматора, первый выход первого преобразователя Я двоичного кода в двоично-десятичный и выходы разрядов двоично-жесятично го сумматора являются выходамн суммн. рующего блока.

1035600

Изобретение относится к вычисли.тельной технике и предназначено для использования в универсальных и специализированных цифровых вычислительных машинах.

Известно устройство для умножения двоично-десятичных чисел, содержащее матричные множительные устРойства для выполнения двоичных умножений десятичных разрядов и устройства преобразо-. вания семираэрядных двоичных произве- 1О дений в двухраэрядные двоично-десятичные .произведения (1).

Недостатком данного устройства является последовательная и множитель(ная работа, при которой множимое по-. 15 следовательно умножается на десятичные разряды множителя, и следователь-, но, быстродействие его невелико.

Наиболее близким.является Устройство для умножения,содержащее регистры 20 множимого,множителя и произведения, матрицу блоков умножения и суммирУющий блок, причем первые вхОды блоков умножения каждой строки матрицы соединены с выходами соответствующих групп регист 1 75 ра множимого, вторые входы блоков умно жения каждого столбца матрицы соединены ) с выходами соответствующих тетрад ре- гистра множителя, выходы суммирующего блока соединены со входами регистра 30 произведения, выход 1 -ro блока умно;4" жения -й строки матрицы (1 =1,...,,Й; =1,...,М и — число групп разрядов множимого; М- число групп разрядов множителя) подключены ко входам (1 + j-1)-й и (т +1 )-й групп разря дов суммирующего блока при этом блоки умножения выполнены в виде узлов постоянной памяти (2J .

Недостатком этого устройства является то, что при перемножении двоич- 40 но-десятичных чисел значительно, усложняется выполнение блоков умножения, которые должны осуществлять перемножение однораэрядных десятичных чисел, заданных в двоичном коде. При g5 этом, в частности, возрастает объем памяти используемых узлов постоянной памяти.

Целью изобретения является сокращение количества оборудования при перемножении двоично-десятичных чисел.

Для достижения поставленной цели устройство для умножения, содержит регистры множимого, множителя и произведения, матрицу блоков умножения и суммирующий блок, причем первые входы блоков умножения каждой строки матрицы соединены с выходами соответствующих тетрад регистра множимого, вторые входы блоков умножения каждого60 столбца матрицы соединены с выходами соответствующих тетрад регистра множи теля, вша. " суммирующего блока соедине -, ны со входа. гистра произведения, сум1 мирующий блок.- ержит двоичные сумма- 65 торы, преобразователи двоичного кода в двоично-десятичный и двоично-деся-: тичный сумматор, причем вход K --ro двоичного сумматора (Y=l М +М-3;

К -число десятичных разрядов множимого, М- число десятичных разрядов множителя) соединены с выходами 1-х блоков умножения ) --х строек матрицы ((=1,...,К; =1, . М;1+ = K-2), выходы первого блока умножения первой стройки матрицы, двоичных с мматоров. с первого по (Н + М-3) -й и -го блока умножения М-й строки матрицы соединены со входами преобразователей двоичного кода в двоично-десятичный с первого по (N + М-1)-й соответственно, р-й выход -ro преобразователя двоичного кода в двоично-десятичный (P=

=1,...Я; Р- число выходов данного преобразователя двоичного кода в двоично-десятичный; ф = 1,..., К + М-1) соединен со входом (P+ q, 2)-ro разряда двоично-десятичного сумматора, первый выход первого преобразователя двоичного кода в двоично-десятичный и выхоцы разрядов двоично-десятичного

t сумматора являются выходами суммирующего блока.

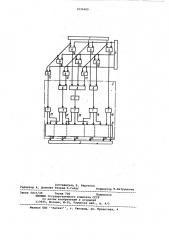

На чертеже представлена функциональная схема устройства для умноже- ния для случая умножения двух трехразрядных десятичных чисел.

Устройство содержит 1 трехразрядный регистр множимого 1, трехразрядный регистр множителя 2, шестиразрядный регистр произведения 3, девять блоков умножения 4, блок суммирования

5, в состав которого входят двоичные сумматоры 6, преобразователи двоичного кода в двоично-десятичный ? и двоично-десятичный сумматор 8. Блоки 4 имеют выходы 9-17, преобразователи 7 имеют выходы 18-22, сумматор 8 имеет выходы 23-28. Блоки умножения 4 могут быть комбинационными или выполнены в виде узлов постоянной памяти. Преобразователи 7 выполнены комбинацион ными.

Работу устройстваможно показать на примере умножения двух-трехраэрядных десятичных чисел

АААхВ В В-СССС

На первой ступени умножения на блоках умножения 4, осуществляющих двоичное умножение, перемножаются между собой десятичные разряды множимого и множителя, поступающие с регистров 1 и 2. Первая ступень в данном примере состотит из девяти блоков умножения 4, на которых образуется девять частичных семиразрядных двоичных произведений

QBp j Ay В, А В, A By.

1035600

На второй ступени в трех разрядах частичные произведения одинакового веса на сумматорах 6 свертываются в однорядовые двоичные формы

A В„ + A Bo i о М 1 0 5

Аа +AЪ +Aq я в +а в„.

На третьей ступени умножения одно рядовые двоичные формы суммчастичных 10 произведений на пяти преобразователях 7 переводятся в двоично-десятичную форму. Иэ-за увеличения числа частичных произведений в трех средних преобразователях 7 число десятичных 15 разрядов на выходе увеличено до трех.

Соседние двоично-десятичные час . тичные произведения получаются с перекрытием между собою не менее чем на один. десятичный разряд. 20

На четвертой ступени умножения суммы частичных произведений в двоично-.,десятичной форме с перекрытиями на многоразрядном двоично-десятичном сумматоре 8 свертываются в оконча" тельное двоично-десятичное произведение, которое запоминается на регистре ,произведения 3. Пусть, пример, перемножаются два трехразрядных числа:

:621х 325= 201825

Ао 1 Во

Таблица 2

Т а б л и ц а 3

В = 2 л

A = 2

Значения (двоично-де-.сятич ные) A =- á

В табл 1 приведены значения частичных произведений, получающиеся в результате перемножения десятичных разрядов сомножителей на блоках умноТаблица140 жения 4.

Эффективность изобретения заключается в том, что в данном устройстве использованы более простые двоичные блоки умножения,что позволяет сокра

45 тить объемиспользуемого оборудования,. в частности, при выполнении этих блоков на узлах постоянной памяти сокращается объем памяти. ! Значения двоичные

Выходы блоков 4 9 10 ll 12 13 14 15 16 17

05 02 10 03 04 30 06 12 18

В результате сложения частичных произведений одинакового веса на двоичных сумматорах 6 образуются соответственно двоичные значения 12, 37, 18, таким образом на входе преобразователей 7 поступают соответственно двоичные значения 05 12, 37,18,18.

В табл 2 приведены значения частичных произведений в результате преобразования их в двоично-десятичную форму на преобразователях 7

Выходы преобразователей 7 18 19 20 21 22

Значения (двоичнодесятичные) 05 012 037 018 18

В табл. 3 приведены окончрлельные значения двоично-десятичных разрядов произведения в результате сложения на двоично-десятичном сумматоре 8

Выходы сумма.тора 8 23 24 25 26 27 28

5 2 8 1 0 2

Составитель В. Береэкин

Редактор А. Долинич Техред И.Гайду Корректор И.Ватрушкина

Заказ 5833/49 Тнрав .706 Подписное

ВЯИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, %-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Уигород, ул. Проектная, 4