Устройство для вычисления обратной величины

Иллюстрации

Показать всеРеферат

„„SU„„1 5603 А

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН эся> G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ I мент И, причем информационный вход устройства соединен с первым входом сумматора и информационным входом первого сдвигателя, выход которого соединен с установочным входом пятого регистра, выход которого соединен с первым информационным входом мультиплексора, выход которого соединен с вторым информационным входом первого сумматора-вычитателя, выход знака сумматора соединен с первым входом первого элемента .ИЛИ, выход которого соединен с управляющим вхо" дом первого сумматора-вычитателя, информационный выход сумматора соединен с входом блока приоритета, сиг нальный выход которого соединен с g первым входом второго элемента ИЛИ, информационный выход блока приоритета соединен с управляющими входами первого и второго сдвигателей и установочным входом четвертого регист- р ра, выход младшего разряда которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с

Эмад нулевым входом триггера запуска, прямой выход которого соединен с управляющим входом мультиплексора и первым входом элемента И, второй вход кото- Р рого соединен с выходом генератора Ж импульсов, а выход-с входом управле- 1, ; ния сдвигом четвертого и пятого ре- фф гист ров, выход т рет ьего ре гист ра соеГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3377162/18-24 (22) 10. 12. 81 (46) 15.08.83. Бюл. N 30 (72) 1.Н. Костяшкин и 10,Н. Романов (71) Рязанский радиотехнический институт (53) 681.325.66(088.8) (56) 1. Карцев М.А, Арифметика цифровых машин. М., "Наука", 1969, с. 496.

?, Оранский А.М, Аппаратные методы в цифровой вычислительной технике", Минск, БГУ, 1977, с. 180, рис. 6,10 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ОБРАТНОЙ ВЕЛИЧИНЫ, содержащее первый, второй, третий и четвертый регистры, первый и второй сумматоры-вычитатепи и О-триггер, причем -информационный вход устройства соединен с установочным входом. первого регистра, выход второго регистра соединен с первым информационным входом первого сумматора"вычитателя, выходы третьего и четвертого регистров соединены, соответственно, с первым и вторым информационными входами второго сумматора-вычитатепя, выход которого соединен с входом третьего регистра, выход первого сумматора-вычитателя соединен с входом второго регистра и входом О-триггера, инверсный выход которого соединен с управляющим входом второго сумматора-вычитателя, отличающееся тем, что, с целью повышения быстродействия, устройство содержит пятый регистр, сумматор, первый и второй сдвигатепи, блок приоритета, мультиплексор, генератор импульсов, триггер запуска, первый и второй элементы ИЛИ и элединен с информационным входом второго сдвигателя, выход которого соединен с вторым информационным входом. муль" типлексора, прямой выход О-триггера соединен с вторым входом nepaoro ýëåмента ИЛИ, управляющий вход устройства соединен с единичным входом триггера запуска.

1035603

Изобретение относится к автоматике и вычислительной технике и предна эна чено для вычисления обратной величины чисел, представленных в двоичной системе счисления с фиксированной запятой, Известно устройство деления, которое содержит регистр частного с цепями сдвига, регистр делителя, регистр частичных остатков с цепями сдвига и обращения кода, сумматора, а также сортветствующее устройство управления, обеспечивающее выработку необходимых управляющих сигналов P1).

Наиболее близким по технической сущности к изобретению является устройство для вычисления образиной величины, содержащее четыре регистра, два сумматора, вычитателя, а также триггер управления сумматорами, причем информационные входы устройства соединены с установочными входами первого регистра, выходы первого и второго регистров соединены соответственно с первым и вторым входами первого сумматора-вычитателя, выход которого соединен с входом первого

pýгистра и входом О-триггера, выход которого соединен с управляющими входами первого и второго сумматоров-вычитателей, выходы третьего и .етвертого регистров соединены, соответственно, с первым и вторым входами второгo сумматора-вычитателя, выход которого соединен с входом четвертого регистра, выходы второго и третьего регистров соединены, соответственно, со своими входами 1 2).

Это устройство реализует операцию вычисления обратной величины

У=1/Х посредством Формирования сум" мы сходящихся приращений

„= + r q .2 """", о где q = +1 - соответствующим образом подобранные операторы; i t>2»...(ï-1).

На каждой итерации оценивается разность z = 1-xyi. Устройство функционирует йо следующему алгоритму;

Х„ „= Х,+q,.Х g «41)

М + 32 (1+1) 1Ф1 1 1 Е) ,ИСАИ Z>>f0

-1,ЕсКч „.„„>

-1» 1- 2 - с, 2-,1 >1 ) с начальными условиями Х =Х Y =1

> о >

7 -1 м

Общим недостатком устройств является независимость длительности итерационного цикла вычисления обрат" ной величины от величины приращения аргумента, что приводит к непроизво" дительным затратам времени, наиболее существенным при незначительных величинах приращения аргумента.

Цель изобретения - повыщение бы1О стродействия устройства для случаев малых приращений аргумента, представляющих 2, где,4 =1,2,3,...,(п-1).

Поставленная цель достигается тем> что в устройство, содержащее первый, 15 второй, третий и четвертый регистры, первый и второй умматоры-вычитатели и D-триггер, причем информационный вход устройства соединен с установочным входом первого регистра, 20 выход второго регистра соединен с первым информационным входом первого сумматора-вычитателя, выходы третьего и чствертого регистров соединень!, соответственно, с первым и вто25 рым информ ационными входами второго сумматора-вычитателя, выход которого соединен с входом третьего регистра, выход первого сумматора-вычитателя соединен с входом второго 0 регистра и входом D-триггера, инверсный выход которого соединен с управJIRtIUHM входом второго сумматора-вычитателя, введены пят>ый регистр, сумматор, первый и второй сдвигатели., блок приоритета, мультиплексор, генератор импульсов, триггер запуска, первый и второй элементы ИЛИ и элемент И, причем информационный вход устройства соединен с первым входом сумматора и информационным входом первого сдвигателя, выход которого соединен с установочным входом пятого регистра, выход которого соединен с первым информационным входом мультиплексора, выход которого соединен с вторым информационным входом первого сумматора-вычитателя, выход знака сумматора соединен с первым входом первого элемента ИЛИ, выход которого соединен с управляющим входом первого сумматора-вычитателя, информационный выход сумматора соединен с входом блока приоритета, сигнальный выход которого соединен с первым входом второго элемента ИЛИ, информа"

55 ционныи выход блока приоритета соединен с управляющими входами первого и второго сдвигателей и установочным входом четвертого регистра, выход

1035603

40 младшего разряда которого соединен с вторым входом второго элемента

ИЛИ, выход которого соединен с нулевым входом триггера запуска, пря мой выход которого соединен с управляющим входом мультиплексора и пер8blM входом элемента И, второй вход которого соединен с выходом генератора импульсов, а выход — со входами управления сдвигом четвертого и пятого регистров, выход третьего регистра соединен с информационным входом второго сдвигателя, выход которого соединен со вторым информационным входом мультиплексора, прямой выход 0-триггера соединен со вторым входом первого элемента ИЛИ, управляющий вход устройства соединен с единичным входом триггера запуска.

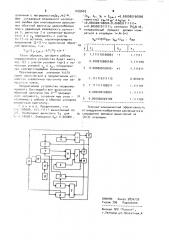

На чертеже представлена блок-схема устройства для вычисления обратной величины, Устройство содержит сумматор 1, сумматоры-вычитатели 2 и 3, регист ры 4-8, сдвигатели 9 и 10, мультиплексор 11> блок приоритета 12, генератор импульсов 13, триггер запуска 14, 0-триггер 15, элемент И 16, элементы ИЛИ 17 и 18.

Блок 12 приоритета вырабатывает сигнал логической единицы на самом старшем информационном выходе блока, в соответствующем разряде которого содержится единица, если же число . равно нулю, единица появляется на сигнальном выходе блока.

Устройство работает следующим образом.

Предположим, что в некоторый j-й момент времени в регистре 4 записа,но число Х, значение обратной величины которого, вычисленное устройством к j-му моменту времени, хранит" ся в регистре 6. На информационный вход устройства поступает новое значение аргумента, из которого в сумматоре 1 образуется разность (3)

Эта разност ь (й Х вЂ”вЂ” 2, где,Д = (j=1,2....,n-1) из сумматора 1 передается (со знаком) для анализа в блок приоритета 12, где определяе ся наиболее старший номер разряда О в коде разности ЬХ1, в котором записана единица, в соответствии с выражением

{ 1 г где г= — оператор выделения стар= 1о шей единицы в коде дХ ; состояние разрядов кода .1 <р

Знак разности определяет работу сумматора-вычислителя в подготовительном такте, в котором определяет" ся начальное значение частичного остатка

210= "j 5-1),(и-1). (Ц

Для -этого предыдущее значение обратной величины у(1) („ g) хранящееся в регистре 6, передается со сдвигом на,1Л разрядов вправо (это соот,и ветствует умножение на 2 ), осуществляемым сдвигателем 10, управляемо-, го блоком приоритета 12, через муль" типлексор 11 на вход сумматора-вычитателя 2. Кроме этого, значение аргу" мента Х записывается в регистр 4 и передается через сдвигатель 9 со сдвигом на,4-3 разрядов вправо в регистр 7, а в регистр 8 записывается единица в М-3-й разряд, что соответ" ствует формирование начальных кон" стант x ° 2 " и 2, где 1=„0-3, соответственно. С приходом управляющего сигнала "Пуск триггер 14 устанавливается в единичное состояние и разрешает прохождение с генератора 13 импульсов через элемент И 16 на сдвиговые входы регистров 7 и 8.: Таким образом, происходит формирование приращений сумматором-вычитателем 3 к ранее вычисленному (хранящемуся в регистре 6) результату у„. „ согласно выражению

И-4

""i, -,-,и,+ " q;-

1=,0-Ъ

Знак первого приращения в j-м цикле определяется знаком z о хранимым в 0-триггере 15, значение которого представляет собой закодированную величину q а мультиплексор 11 подключает ко входу сумматора-вычитателя 2 выход сдвигающего регистра 7.

При ЬХ =0 (во всех разрядах О) значе"

3 ние у равно уже вычисленному 1. у Й значению, в случае, когда

Ъ

x = ? устройство функционирует аналогично 2), отличаясь от него усеченным итерационным циклом, зависящим от величины,й, и начальными условиями y =y у >р, g, z= - д, у.,и 4 . Итерационный процесс протекает до выполнения и-1 итерации, что обеспечивает вычисление обратной

1035603 а (Xz, Х, У1 w lg .. 0.000000100000 известны) z z<<- л х у =0.000000100000-0.000001111111

-0.000001011111; согласно (4)+ =6, итерационный процесс должен качинаться в итерации 1 Р-33

g@ з 1цп2яов у ц у - 1 ф 2

1.111110100001 -1 1.11111

1.1111АО

1.111011 ч 0.000000100101 +1

0,000010

1. 111101

1. 111111

1, 111100

Технико-кономическая эфФективност ь от внедрения изобретения заключается в сокращении времени вычислений на (,О-3) итерации.

1 1 — 3

ВНИИПО Заказ 5834/50

Тираж 706 Подписное

Филиал ППП "Патент" г. Ужгород,ул. Прое ктная,4

Величины с погреаностью/63 / 2 ".

Для устранения возможного накопления ошибки при многократном вычисле нии обратной величины целесообразно иметь удвоенную разрядность регистpB j регистра 7 и сумматора вычита теля 3 и z„ определять с учетом (и= 1)-го остатка, характеризующего

Выполнение (J -1)- го Вычисления обратНОй ВЕЛИЧИНЫ, Т . Е .

t0

- „:О= j-1И 1

Таким оора зон, ал гдрит м работы предлагаемого устройства будет иметь зид (2) с учетом условия 1=а-3 и науслови ) и о 9 определя е

О

:-":ых соответствующими значениями, Первоначальное значение У=1/Х ноже.: Вычисляться в предлагаемом устрой;." Ве =-"";ÿàëàãèèío прототипу или за- 20

S 1:111111100011

Предлагаемое устройство позволяет

lовысить быстродействие вычисления обратной величины при 2 приращен ÿ>" аргумента coxpBHRH при этом

-..озможность работы в обычных условиях

àнапогично прототипу. р и и е р. Предположим, что

- 0,100000, У1.11111 вычисленный по

Чеобходийо Вычислить У Для 36

- .;,- l,, 00001. Определим X =- 0,000001.