Устройство для реализации микропрограммных автоматов

Иллюстрации

Показать всеРеферат

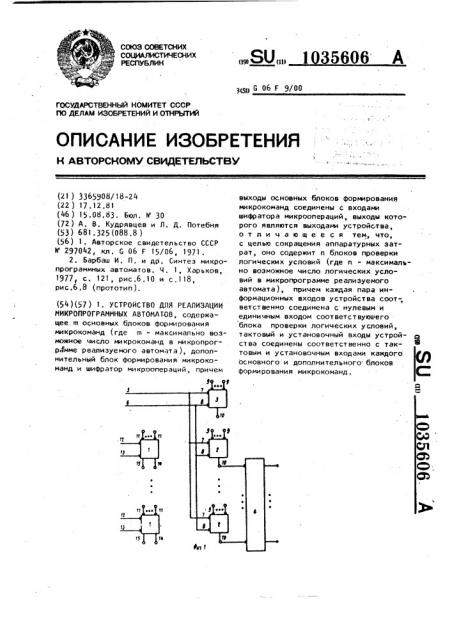

1. УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ МИКРОПРОГРАММНЫХ АВТОМАТОВ, содержащее m основных блоков формирования микрокоманд (где m - максимально возможное число микрокоманд в микропрогpdMMe реализуемого автомата), дополнительный блок формирования микрокоманд и шифратор микроопераций, причем выходы основных блоков формирования микрокоманд соединены с входами шифратора микроопераций, выходы которого являются выходами устройс-тва, отличающееся тем, что, с целью сокращения аппаратурных затрат , оно содержит п блоков проверки логических условий (где п - максимально возможное число логических условий в микропрограмме реализуемого автомата), причем каждая пара информационных входов устройства соот-, ветственно соединена с нулевым и единичным входом соответствующего блока проверки логических условий, тактовый и установочный входы устройства соединены соответственно с так (Л товым и установочным входами каждого основного и дополнительногоблоков формирования микрокоманд. 1

СОЮЗ СОВЕТСНИХ

СОЦ 1АЛИСТИЧЕСНИХ

РЕСПЬБЛИН

„с 06 Р 9/юю

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

OCVRAPCTBEHHblA HOMHTET CCCP

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3365908/ 18-24 (22 ) 17.12.81 (46 ) i g .08 . 83 . Ьюл . V 30 (72 ) А. В. Кудрявцев и Л. Д. Потебня (53) 681.325(088,8) (56) 1. Авторское свидетельство СССР

11 297042, кл. G 06 F 15/06, 1971.

2. Барбаш И. П. и др . Синтез микропрограммных автоматов ° 4. 1, Харьков, 1977, с, 121, рис.6.10 и с.118, рис.6 ° 8 (прототип). (54)(57 ) 1, УСТРОЙСТВО ДНЯ РЕАЛИЗАЦИИ

МИКРОПРОГРАММНЫХ АВТОМАТОВ, содержащее rn основных блоков формирования микрокоманд (где m - максимально возможное число микрокоманд в микропрограмме реализуемого автомата ), дополнительный блок формирования микрокоманд и шифратор микроопераций, причем

„„SU„„1035606 А выходы основных блоков формирования микрокоманд соединены с входами шифратора микроопераций., выходы которого являются выходами устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит и блоков проверки логических условий (где и - максимально возможное число логических условий в микропрограмме реализуемого автомата), причем каждая пара информационных входов устройства соот-, ветственно соединена с нулевым и единичным входом соответствуюшего блока проверки логических условий, тактовый и установочный входы устройства соединены соответственно с так- Е товым и установочным входами каждого основного и дополнительного блоков формирования микрокоманд .

1035606

2, Устройство по и. 1, о т л ич " ю щ е е с я тем, что основной блок формирования микрокоманд содержит элемент ИЛИ и D-триггер, причем управляющие входы блока соединены через элемент ИЛИ с D-входом

D-триггера, выход которого является вьходом блока„ тактовый вход которого соединен с синхронизирующим входом D-триггера, а установочный - c, нулевым входом D-триггера.

3.,Устройство по и. 1, о т л ич а ю щ е е с я тем, что дополнительный олок формирования микропрограмм содержит элемент ИЛИ и

D-триггер, причем управляющие входы блока соединены через элемент ИЛИ с

0-входом D-триггера, выход которого

Изобретение относится к автомати, е и вычислительной технике, в част.ости к устройствам управления и конт" роля„ и может быть использовано как для моделирования микропрограмм, опи- 5 сывающих процесс функционирования управляющих автоматов, так и для управления исполнительными устройствами объектов управления по ".àäàííîé микропрограмме, 1Î

Известно устройство для реализации коне:;ных автоматов на вычислительной среде, содержащее вычислительную среду., автомат настро".êè,,дешифраторы, триггеры,,элементы И t 1).

Недостатками этого устройства являются сложность схемы и большой объем оборудования, Наиболее близким техническим решением к изобретению является микропрограммный автомат, содержащий группу микропрограммных модулей, выходы которых через шифратор микроопераций соединены с выходами автомата, Настройку автомата на заданную микропрограмму осуществляют путем соответствующей коммутации входов выходов микропрограммных модулей, "1ля =-.òîãî выполняют следующее: выделяют на граф-схеме реализуемой мик- 30 рог.рограммы стандартные подграфы, предс- азляющие собой последовательное соединение операторной и логичеявляется выходом блока, тактовый вход которого соединен с синхронизирующим входом О-триггера, а установочный вход - с единичным входом D-триггера.

4, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок проверки логических условий содержит элемент ИЛИ, первый и второй элементы И, причем управляющие входы блока через элемент ИЛИ соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с нулевым и с единичным входами блока соответственно, выходы первого и второго элементов И являются нулевым и единичным выходами блока соответственно. ской вершины; доопределяют до стандартного подграфа оставшиеся операторные вершины (кроме начальной ) введением тождественно-истинных логических вершин; доопределяют до стандартного подграфа оставшиеся логические вершины введением фиктивных операторных вершин; сопоставляют с каждым стандартным подграфом соответствующий микропрограммный модуль; сопоставляют с каждым стандартным подграфом соответствующие информационные входы автомата, а для подграфов, содержащих тождественно-истинные логические вершины, предусматривают специальный вход для нейтрализации неиспользуемого нулевого выхода соответствующего микропрограммного модуля; сопоставляют с каждым стандартным подграфом уставоночные входы соответствующего микропрограммного моI дуля, указав для них номера тех микро программных модулей, выходные сигналы которых должны быть использованы для возвращения данного микропрограммного модуля в исходное состояние; произвс дят соединение входов и выходов используемых микропрограммных модулей в соответствии с топологией полученной структурно-реализуемой граф-схемой микропрограммы P2).

Необходимость преобразования исходной граф-схемы в структурно-реа606 Я

3 1035 лизуемую Форму затрудняет реализацию конкретного автомата, что является недостатком. Теоретически, имея

m + 1 микропрограммных модулей можно реализовать автомат, граф-схема мик-5 ропрограммы которого содержит m операТорных и m логических вершин при условии что после каждой операторной вершины следует логическая вершина °

Однако для реальных микропрограмм 10 данное условие не выполнимо, в связи с чем на практике требуется проводитЪ доопределение части вершин граф-схемы до стандартных подграФов, Пусть для. решаемого класса задач требуется доопределить не более

r операторных и не более q логических вершин. В данном случае при наличии

m + 1 модулей могут быть реализованы микропрограммы, содержащие не более 20

m-q микрокоманд, и не более и-r проверок логических условий. При этом за счет искусственного введения в микропрограмму q фиктивных операторов и r тождественно-истинных логических 2 условий в схеме автомата избыточно и спол ьзуются 2ф элементов ИЛИ, 2 элементов И и q триггеров, что также

v является недостатком.

Цель изобретения - сокращение апЗО паратурных затрат .

Поставленная цель достигается тем, что устройство для реализации микропрограммных автоматов, содержащее m основных блоков формирования микрокоманд (где m .— максимально возмож35 ное число микро команд в ми кропрограмме реализуемого автомата ), дополнительный блок формирования микрокоманд и шифратор микроопераций, причем выходы основных блоков формирования 0 микрокоманд соединены с входами шифратора микроопераций, выходы которого я вля ются выхода ми у ст р ой ст в а, содер" . жит и блоков проверки логических ус/

45 ловии (где n — максимально возможное число логических условий в микропрограмме реализуемого автомата ), причем каждая пара информационных входов устройства соответственно соединена с нулевым и единичным входом

50 соответствующего блока проверки логических условий, тактовый и установочный входы у строй ства соединены соответственно с тактовым и установочным входами каждого основного и дополнительного блоков формирования микрокоманд, а также тем, что основной блок формирования микрокоманд содержит элемент ИЛИ и О-триггер, причем управляющие входы блока соединены через элемент ИЛИ с 0-входом

0-триггера, выход которого является выходом блока, тактовый вход которого соединен с синхронизирующим входом

0-триггера, а установочный - с нулевым входом 0-триггера; а также тем, что дополнительный блок формирования микрокоманд содержит элемент ИЛИ и

D-триггер, причем управляющие входы блока соединены через элемент ИЛИ с

D-входом 0-триггера, выход которого является выходом блока, тактовый вход которого соединен с синхронизирующим входом D-триггера, а установочный вход - с единичным входом 0-триггера, а также тем, что блок проверки .логических условий содержит элемент ИЛИ, первый и второй элементы И, причем управляющие входы блока через элемент

ИЛИ соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с нулевым и с единичным входами блока соответственно, выход первого и второго элементов И являются нулевым и единичным выходами блока соответственно.

На фиг. 1 приведена структурная схема устройства; на фиг. 2,3, 4 приведены функциональные схемы блока проверки логических условий, основного и дополнительного блоков формирования микрокоманд соответственна; на Фиг.5граф-схема микропрограммы; на фиг,6ее реализация с использованием блоков формирования микрокоманд и проверки логических условий, Устройство содержит блоки 1 проверки логических условий, основные блоки 2 формирования микрокоманд, дополнительный блок 3 формирования микрокоманд, шифратор 4 микроопераций, тактовый вход 5 устройстЬа, установочный вход 6 устройства. На структурной схеме также изображено: тактовый вход 7 блоков 2,3, установочный вход 8 блоков 2,3, управляющие входы 9 и выход 10 блоков

2,3, управляющие входы 11 блока единичный и нулевой входы 12 и 1 3, а также единичный и нулевой выходы 14и 15 блока 1 соответственно. Нулевой

13 и единичный 12 входы блоков 1 являются информационными входами устройства, а выходы шифратора 4 являются выходами устройства.

103$60L

Ф

Б "Ок 1содерж,и- элемен ИЛИ 1á, .--:.pBûé и второй элементы И I8 соот32 1СTВЕННО .

Блоки 2 и 3 содержат элемент ИЛИ 19, 0-<риГГер 20. .У

:" 2 фиГ " oбозH2iIPно - А I -R Ч э = p2TOpi- ая вершкна (cooTветcт ну1, -й ми!<рОкоманде /; p. "J я лОги -:ес::- 2 BppwèHà {соот ветству т 1-и/ логиi; 0 -,;- .;,. к о !иу у сл О ни ю ми к p Q 11 р О Г 13 2 м мы

1-12 фи!-, 6 пунктиром показаны межбп! . ; —,ые;.оедлне- к -", соответствующие в /Г»...; IicниведpHHQÉ на ф .Гг., 5 граф-схе-!

<. м, И1!фОомэц j<3 .!Ные, тактОБые и JicT2

1Б

, 0 о -!нь!е входы олокон опущены.

Ь:, . 1 Г!редн-.-.значен для моделиро-.

«2HI ° t3 лОГИ !ескОй зершины Гp2<13 cxBHbf

МИ

1 1! моде-!1,р,". т:.входящие г,>. -, згг-,

;-,и-:; ы; . Нулевой выходы 14 и 15 мо-. л<-!1!1=у;=- исходящие из нее дуги соо; не, c: «BHHO пр .. выполнении и при не

:,!П -." Н- - ЛОГИ -!Е ..КОГО "СЛОЕЛЯ, -,.",;.,:-;:å-.. oãо н д21-ной вершине Граф."1 . .! . o go K 11P i« f1 id 22 H 2 ч е н ф Я .—;: и.! —,

-,-аф -схе-,,ы мк кропрогр амь!ы . !ои

;, !Оанляющие входы 9 блока 2

:!;рую«т заходящие в опер аторнуlO д„!1., 2 исходяща", из нее :,Одели f«;to-: OB Dif„,

2. ИСХОД!ЯЩая И Начал ЬНОИ НЕР

Оаф — "хемы мОделируе тся Вы

Ополнительногo блока 3, . е н,.oнc -- н""ю вершину граф;.х -: .;!., Оц л" póþò<. =, у пзанляюцими

Х01:= "! ДОПОЛНИ !.ЕЛЬНОГ O 6130K2 3 .!

1:..ч, ii3 i 3Р МИ КРООПЕР2ЦИЙ СЛУ— ппеоораэоаани ; сигнала с

-!,:;<Од.- ; ocH„:âíîãî блока 2 в соно< 30 э CHÃ! 2t ОВ У OtP2B;"IЕНИЯ МИ К

ВОО".BP 2 - l :, :ИМИ . СООТН Ет CT БУЮЩУЮ НЫПОЛ

=. Ой -, данном такте работы уст ройс-!— .:.д ми кпо:-:QM2HI3p Шифратор g может бэ! —:: ныГ!Оп-Ieн на k мнсгQBxoaoBIlx

r,0

И 0!/ Гне 1< — мак .мчаль но

:":;н "е -!Гисло микроопераций н мкк30к,м= ..-,.",:, форм!:,ронание cocтана микpoooo,,;-.:.,",-й никрокоманды осущест нляГуjе! Соединени!я к-:-:жного входа 10

<30-; 003 4 с входами СООтнетстную н,,-n.- t

Устройство работает следующим образом„ !

ПО э аданной граф-схеме ми кропрограммы (например, фиг.5 ) реализуемого микропрограммного автомата определяют необходимое количество блоков

2 и 1, которое равно числу соответствующих нершин на граф-схеме, Выбp2I-ные блоки нумеруют к соединяют между ссбой в соответствии с топологией исходной граф-схемы микропрограммы (фиг,6 ), Производят необходимые соединения в схеме шиФратора 4, по =л!е чего, подачей кмпульса начальной установки на вход 6 устройства устанавливают все триГгеры 20 основных олоков 2 н нулевое, а триггер

20 доголнительного блока 3 в едини 1ное состояние . Устройство начинаеТ функционировать н момент подачи на вход g госледонательности тактовых импульсон. При этом устройство рабстает аналогично кольцевому регистру сдвига,ячейками которого являют;:я задействованные блоки 2 и 3.

Последовательность продвижения "едини!1ь!" из б ока 3 по ячейкам "регистра Определяются характером блоч! .1ы:< соединений и текущим состоянием нходон 12 и 13 блоков l . E сли устIooH c T Bo используют для моделирования микропрограмм, то сигналы на его нформационные входы 12 и 13 поступают с органов управления, имитирующих выполнение или невыполнение проверяемых в ходе отработки микропрограммы соответствующих логикpcf

ИЛИ 16 данного блока этот сигнал будет приложен к первым входам элементов И 17, 18 того же блока, Если логическое условие Р, проверяемое данным блоком, не выполнено, в этом случае на втором входе элемента И 17 рассматриваемого блока 1 присутствует сигнал логической единицы, что приводит к появлению единичного сиг1О нала на нулевом выходе 15 . Через соответствующий соединительный проводник этот сигнал приложен к одному из управляющих входов 9 блока 2, моделирующего операторную вершину А и далее через элемент ИЛИ 19 этого блокак 0-входу соответствующего триггера 20.

В момент появления на входе 5 устройства очередного тактового импульса данный триггер переходит в единичное состояние, а предыдущий возвращается в нулевое состояние . Таким образом прекращается выполнение микрокоманды А, а сигналом с выхода 10 сработавшего блока 2 в шифраторе 4 сформируется микрокоманда А . Если же логическое условие Р, в момент его проверки окажется выполненным, то очередным тактовым импульсом в единичное состояние будет переведен триггер

20 дополнительного блока 3. Срабатывание этого триггера прекращает по-; дачу тактовых импульсов на вход 5, что вызывает останов устройства (генератор тактовых импульсов и цепи управ- 3S ления на фиг. 1 не показаны ).Для повторного запуска устройства необходимо в нов ь включи т ь генератор тактовых импульсов.

Введение в устройство блоков позволяет реализовать конкретный микропрограммный автомат непосредственно по исходной граф-схеме микропрограммы, минуя этап преобразования ее в структурно-реализуемую форму, Зто упрощает структуру межблочных соединений и процедуру, реализации автомата в целом.

Аппаратурные затраты на изготовление предложенных одного блока 1 и одного блока 2 равны аппаратурным затратам на изготовление известного блока. Поэтому при использовании в предложенном устройстве одинакового числа этих блоков (n=m ) суммарные аппа ратурные затраты на его изготовление меньше по сравнению с известным устройством на два элемента И, входящих в состав его (пн-1)-ro блока, модулирующего конечную вершину граф-схемы.

Зто достигается за счет отсутствия подобных элементов в дополнительном блоке 3, выполняющем в предложенном устройстве аналогичную функцию.

При num эффект от использования изобретения, выражающийся в сокращении аппаратурных затрат, пропорционален абсолютной величине разности m-n u зависит от класса решаемых с его помощью задач.

Применение изобретения позволяет упростить процедуру реализации микропрограммного автомата и сокра-. тить объем оборудования устройства.

1035606

ВНИИПИ Заказ 5834/50 Тираж 706 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4