Многоканальное приоритетное устройство для подключения абонентов к общей магистрали

Иллюстрации

Показать всеРеферат

МНОГОКАНАЛЬНОЕ ПРИОРИТЕТНОЕ УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ АБОНЕНТОВ К ОБЩЕЙ МАГИСТРАЛИ, содержащее в каждом канале регистр, первую группу элементов И, триггер, причем каждый прямой разрядный выход регистра канала соединен с первым входом соответствующего элемента И первой группы своего канала, выходы элементов И первой группы каждого канала соединены с соответствующей группой выходов устройства, первый ёход триггера каждого канала соединен с соответствующим запросным входом устройства , выход триггера каждого канала соединен со вторыми входами Элементов И первой группы своего канала , вход регистра канала соединен с соответствующим кодовым входом устройства , отличающееся тем, что, с целью сокращения оборудования и повышения быстродействие устройства , в каждый канал устройства введены вторая-группа элементов И, группа элементов задержки, элемент ИЛИ, причем каждый инверсный разрйдный выход регистра канала соединен с первым входом соответствующего элемента И второй группы своего канала , вторые входы элементов И второй группы каждого канала подключены к соответствующей группе входов устройства , а третьи входы через соответствующее количество элементов задержек группы - к соответствующему запросному входу устройства, выходы элементов И второй группы каждого канала подключены к соответствующим входам элемента ИЛИ, выход которого соединен со вторым входом триггера своего канала. оо сд О5 о «ч

СОЮЗ СОВЕТСКИХ

РЕСПУБЛИК

6. 06 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТЭЕККЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3386040/18-24 (22) 25,01.82 (чб) 15.08.83. (72) Ю.Ф, Тихонов, М.Г. Мальцев и В.И. Коснырев (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

М 476566, кл. 6 06 F 9/46, 1975.

2. Авторское свидетельство СССР

М 731438, кл. 6 06 F 9/46, 1980 (прототип) . (54)(57) МНОГОКАНАЛЬНОЕ ПРИОРИТЕТНОЕ

УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ АБОНЕНТОВ

К ОбЩЕЙ МАГИСТРАЛИ, содержащее в каждом канале регистр, первую группу элементов И, триггер, причем каждый прямой разрядный выход регистра канала соединен с первым входом соответствующего элемента И первой группы своего канала, выходы элементов

И первой группы каждого канала соединены с соответствующей группой выходов устройства> первый йход триггера каждого канала соединен с соответствующим запросным входом устройства, выход триггера каждого канаÄÄSUÄÄ 1035607 А ла соединен со вторыми входами элементов И первой группы своего канала, вход регистра канала соединен с соответствующим кодовым входом устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования и повышения быстродействив устройства, в каждый канал устройства введены вторая группа элементов И, группа элементов задержки, элемент

ИЛИ, причем каждый инверсный разрядный выход регистра канала соединен с первым входом соответствующего элемента И второй группы своего канала, вторые входы элементов И второй группы каждого канала подключены к соответствующей группе входов устройства, а третьи входы через соот" ветствующее количество элементов задержек группы - к соответствующему запросному входу устройства, выходы элементов И второй группы каждого канала подключены к соответствующим входам элемента ИЛИ, выход которого соединен со вторым входом триггера своего канала.

>035607

Изобретение относится к вычислительной технике, в частности к приоритетным устройствам, и мо>нет быть использовано в системах, управляющих доступом к некоторому общему ресур"

Су, Известно многоканальное устройство для подключения абонентов к общей магистрали, содержащее в каждом канале генератор импульсов, триггеры разрешения, запроса и памяти запроса и элементы И (1).

Недостаток устройства - большой объем оборудования, Наиболее близким к изобретению по технической сущности является многоканальное устройство для подключения абонентов к общей магистрали, содержащее в каждом канале регистр, первую группу элементов И, блок управления, два дешифратора> два ком" мутатора и сумматор, при этом блок управления содержит триггер и счетчик, причем первый> второй входы триггера соединены соответственно с

: =.рвым и третьим входами блока управления, а первый, второй входы и разряднь1е выходы счетчика соединены соответственно со вторым входом блока управления, с выходом триггера и с группой выходов блока управления, каждый разрядный выход регистра канала соединен с первым входом соот" ветствующего элемента И канала, выходы первой группы элементов И канала соединены с соответствующей груп" пой выходов устройства, первый вход блока управления канала соединен с соответствующим запросным входом уст" ройства, вторые входы блоков управле" ния каналов соединены с тактовым входом устройства, а вход регистра канала соединен с соответствующим кодоBblM входом устройства, группа выходов блока управления канала соединена с выходами дешифраторов канала, группы выходов первого и второго дешифрато" ров канала соединены с группами управляющих входов соответственно первого и второго коммутаторов канала, информационные входы первого коммутатора канала соединены с соответствующей группой входов устройства, информационные входы второго коммутатора канала соединены с разрядными выходами регистра„ выходы коммутаторов канала через сумматор канала соединены с третьим входом блока

55 управления канала, выход которогс

1 соединен со вторыми входами первой группы элементов И канала Г 23.

Однако устройству присущи недостаточное быстродействие и аппаратурная избыточность.

Цель изобретения - сокращение оборудования и повышение .быстродействия.

Поставленная цель достигается тем, что в многоканальное устройство для подключения абонентов к общей магистрали, содержащее в каждом канала регистр, первую группу элементов И, триггер, причем каждый прямой разрядный выход регистра канала соединен с первым входом соответствующего элемента И первой группы своего канала> выходы элементов И первой группы каждого канала соединены с соответствующей группой выходов устройства, первый вход триггера каждого канала соединен с соответствующим запросным входом устройства, выход триггера каждого канала соединен со вторыми входами элементов И первой группы своего канала, вход регистра канала соединен с соответствующим кодовым входом устройства в каждом канале, введены вторая группа элементов И, группа элементов задержки, элемент

ИЛИ, причем каждый и >версный разрядный выход регистра канала соединен с первым входом соответствующего элемента И второй группы своего канала, вторые входы элементов И второй группы каждого канала подключены к соответствующей группе входов устройства, а третьи входы через соответствующее количество элементов задержек группы - к соответствующему запросному входу устройства, выходы элементов И второй группы каждого канала подключены к соответствующим входам элемента ИЛИ, выход которого соединен со вторым входом триггера своего канала.

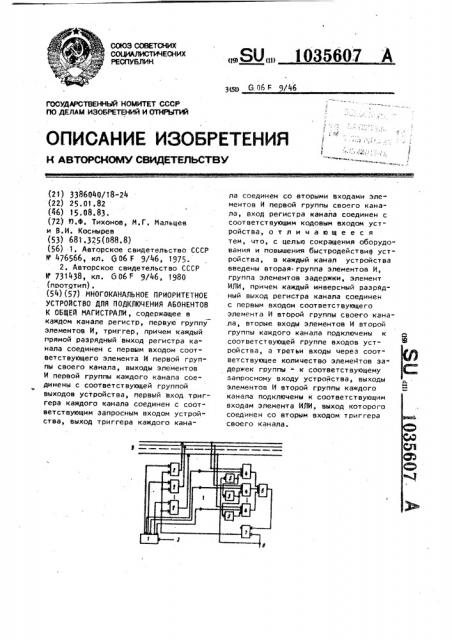

На чертеже приведена структурная схема одного канала устройства.

Канал устройства содержит регистр

1, первую группу элементов И 2, кодовый вход 3 устройства группу элементов И 4„ группу элементов задержки 5, элемент ИЛИ б, триггер 7, запросный вход 8 устройства, общая магистраль 9.

Устройство работает следующим образом.

Э 1035607

В регистр 1 перед поступлением запроса записывают адрес данного канала, соответствующий критерию его приоритета и представляющий собой двоич ное число, после чего адресную шину 5 общей магистрали 10 подключают к первым входам элементов И второй группы элементов И 4 и к выходам элементов И первой группы элементов

И 2. Требование на приоритетное обслуживание через вход 8 устанавливает триггер 7 в состояние "1", которым разрешается работа элементов И

2, и поступает на соответствующий элемент 5.

На общую магистраль 9 из регистра

1 через элементы И 2 выставляется адрес данного канала в виде двоично"

ro кода. Поскольку требования на обслуживание может возникнуть одновре- 20 менно в нескольких каналах, на магистрали 9 устанавливается результирующее число "Проводного ИЛИ", которое поступает на первые входы элЕментов И 4. На вторые входы этих 25 элементов поступает адрес данного канала в обратном коде. К этому времени на третий вход первого элемента

И 4 поступает сигнал с выхода соответствующего элемента, Остальные эле- 30 менты И 4 закрыты сигналом "0" с выхода соответствующих элементов 5, подаваемым на третьи входы этих элементов И 4. На первом элементе И 4 происходит анализ первого (старшего) разряда регистра и старшего разряда общей магистрали 9. Результат анализа, получаемый на выходе первого элемента И 4, равный "!", свидеФльствует о том, что на общей ма- 4р гистрали 9 существует более высокий адрес другого канала. Этот сигнал, пройдя через элемент ИЛИ 6, устанавливае, триггер 7 в состояние "0", сигнал с выхода триггера 7 закрывает 45 элементы И первой группы элементов

И 2, чем снимает адрес данного канала с общей магистрали 9. сли результат анализа равен "0", триггер 7 остается в состоянии "1", адрес данного канала остается в общей магистрали 9 и выполняется анализ следующего разряда адреса данного канала, записанного в регистре l, и следующего разряда в общей магистрес.

ВНИИПИ Заказ 5834/50 рапи 9, на втором элементе И 4, на третий вход которого к этому моменту приходит сигнал с выхода соответствующей линии задержки 5, и так шаг за шагом.

Число шагов обработки во всех слу" чаях одно и то же и равно разрядности общей магистрали 9. По окон" чании обработки гарантировано подключение к общей магистрали только одного канала, имеющего наивысший адПример. Пусть в регистр 1 saписан адрес в двоичном коде 110. По1

15 слав сигнал запроса, подаем этот код на общую магистраль 9. Пусть одновременно с кодом туда поступает адрес другого канала, к примеру 011, на общей магистрали 9 образуется код, равный "Проводному ИЛИ", а именно 111.

На первый элемент И 4 поступают следующие сигналы: на первый вход"1" с "Проводного ИЛИ", на второй вход - "0" с выхода соответствующего инверсного выхода регистра 1, на третий вход - "1" с выхода соответствующего элемента 5.

На выходе первого элемента И 4 находится "0", т.е. сигнал, который оставит адрес данного канала в общей магистрали 9. При приходе сигнала с выхода соответствующего элемента 5 на третий вход второго элемента N 4 приступают к рассмотрению следующего разряда регистра 1 и разряда общей магистрали 9.

Аналогично на выходе первого эле" мента И 4 канала с адресом 011 будет сигнал, равный "1", который устанавливает триггер 7 в "0" состояние, и сигнал "0" с его выхода закрывает элементы И 2, чем снимает адрес 011 канала с общей магистрали

10. K моменту рассмотрения второго разряда регистра 1 канала с адресом

110 на "Проводном ИЛИ" будет код 110.

Таким образом, к общей магистрали,подключается канал с адресом 110, так как он имеет наивысший на данный момент приоритет.

Применение изобретения позволяет сократить объем оборудования устройства путем замены сложных элементов . прототипа на простые логические элементы (И, ИЛИ).

Тираж 706 Подписное филиал ППП "Патент", г, Ужгород, ул. Проектная, 4