Формирователь записи-считывания для запоминающих устройств

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ ЗАПИСИСЧИТЫВАНИЯ ПЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ, содержащий два ключа, выполненных на Mfln-ipaHSHCTopax, вход первого ключа подключен к обшей шине, отличающийся тем, что, с целью повышения быстродействия считывания и уменьшения потребляемой МОЕШОсти , он содержит элемент памяти с тремя состояниями, информационный вкод которого связан с выходами ключей и яв юется выходом формирователя, первый уьравлякяций вход подсоединен к шине разрешения считывания, а второй - к шине разрешения записи-стирания, равляющие вкоды первого и второго ключей подключены соответственно к инверсному и прямому ВЫ}содам элемента памяти Q тремя состояниями , а вход второго ключа подключен к шине записи. 00 ел О) со со

-СОЮЗ СОВЕТСКИХ

-СФюиьнии

РЕСПУБЛИК,.SU„„1035639

9др 611 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ "- ; н лвтоесиовю саидетельстау

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ. (21) 3398667/18-24 (22) 16.02.82 (46) 15.08.83. Бюл. ¹ 30 (72) В-. М. Некрасов и А. М. Прокопенко..

{53), 681;327.6 (088.8) (56) 1. Патент США № 3649848, кл. 307-251, опублик. 1972.

2. Патент США % 3719932-, кл. 340-173, опублик. 1973.

: 3. Авторское свидетельство СССР № 765873, In. 611 C 7/00, 1980 (прототип) .

1. Сидоренко В. П., и др. Особенности и перспективы раэработки и применения .репрограммируемык ПЗУ на основе ф

МДП-структур. Библиотечка Проблемы . интегральной электроники, облество

° Знание+, УССР, Киев1: 1981 (54) (57) ФОРМИРОВАТЕЛЬ ЗАПИСИСЧИТЫВАНИЯ ПЛЯ ЗАПОМИНАЮШИХ

УСТРОЙСТВ, содеркащий два ключа, ща- . полненных иа MQll-транзисторах, щсод первого ключа подключен к общей шине, - отличающийся тем, что,с целью повышения быстродействия считывания и уменьшения потребляемой мощности, он содержит элемент памяти с тремя состояниями, информационный жод которого свиэан с выходами ключей и является выходом формирователя, первый управляющий вход подсоединен к шине раэреаюния считывания, а второй - к шине раэре-

: шения эаписи-стирания, улравлякклие жо.ды первого и второго ключей подключены а соответственно к инверсному и прямому выходам элемента памяти q тремя состояниями, а вход sroporo ключа подключен к шине записи.

1 1035

Изобретение относится к области электронной и вичислительной техники и пред -, нпэначено для использования в интегральных полупосгоянных (репрограммируэмых) запоминакецих устройствах. 5

Известны формирователи записи-считывания, используемые в качестве буферных схем между выходами дешифратора строки и шинами строк накопителя, обеспечивающие формирование уровней напряжения, необуто- 1о дймьтх для работы ячейки памяти в режимах записи, стирания, считывания, содержащее МДП-резисторы и ключи со схемами управления, выполненные на МДП-транзисторах I 1 J и f2(. т5

Недостаток таких устройств состоит в том, что они снижают быстродействие

ППЗУ в режиме считывания, так как расположены между дешифратором и строкой матрицы накопителя И поэтому являются 20 дополнительным звеном задержки между дешифрагором и шиной строки накопителя, Известен формирователь зайиси-считыва» ния для запоминающих устройств содержа щий два МДП-резис гора, коммутируккций

МЯ i-транзистор, управляквций МДП-транзистор, транзистор считывания, словарнуто шину, шину считывания, шину смещения, первую шину управления, вторую шину управления, шину записи, выход устройства Г33.

Недостатком извес тного формирователя является сравнительно низкое быстродействие ППЗУ в режиме считывания, обусловленное тем, что формирователь . записи-считывания расположен меж,ду выходами дешифратора строки и шинами строк накопителя и поэтому asляется дополнительным звеном задержки. между дешифратором H шиной строки на» 40 котпггеля.

Кроме того, недостатком извес тньк. формирователей является то, что они содержат МДП-резистор, через который 45 в ППЗУ в режиме записи подается напряжение записи на выбраннуто шину строки матрицы накопителя, при этом в осталь ньтх невыбранных формирователях записисчитьтвания шина строки матрицы накопи- 50 геля и МДП-резистор подключается через ключ к шине плюс 5В (или обшей ши: не), и общий суммарный ток, протвкактций через МДП-резисторы, достигает сравнительно большой величины,что обусловлйва- 55 . вт большую мощность, потребляемую

ППЗУ от внешнего источника напряжения записи.

639 2

Цель изобретения — повышен. гродействия. считывания и уменьше", гребляемой мощности.

Поставленная цель достигается тем, что в формирователь записи-считывания для запоминающих устройств, содержащий

/ два ключа, выполненных. íà MjlTI-транзис-, торах, вход первого ключа подключен к общей шине, введен элемент памяти с гремя состояниями, информационный вход ко-. торого связан с выходами ключей и является выходом формирователя, первый управлятоший вход — подсоединен к шине разрешения считывания, а второй — к .шине разрешения зштиси стирания, управЛякацие входы первого и второго ключей подключены соответственно к инверсному и прямому выходам элемента памяти с тремя состояниями, а вход второго ключа подключен к шине записи.

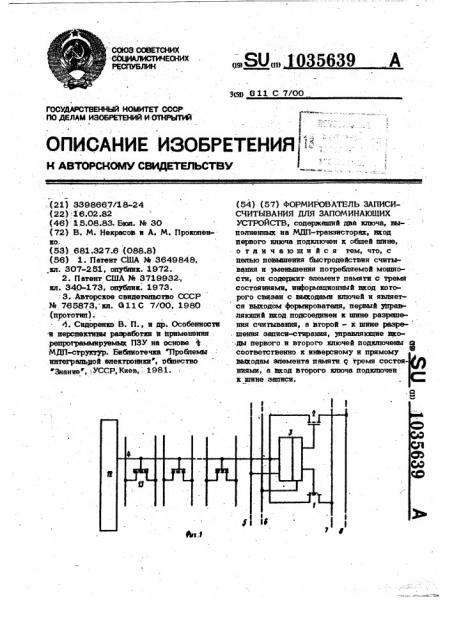

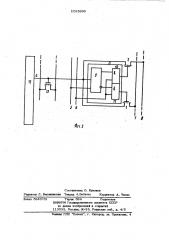

На фиг. 1 представлена функциональная электрическая схема формирователя записи-считывания; на фиг, 2 — вариант формирователя, в котором элемент памяти выполнен на логических элементах.

Формирователь записи-считывания содержит первый ключ, выполненный на

МДП-транзисторе 1, второй ключ, выполненный на МДП-транзисторе 2, элемент памяти 3 с тремя состояниями,,выход фор- с мирователя 4, первую управляющую шину 5, вторую управляккцуто шину 7, шину записи 8, триггер 9, двухвходовые ,злементы И 10 и 11, дешифратор строки

12, запоминающий элемент 13 матрицы накопителя.

Формирователь обеспечивает работу накопителя попупостоянного запоминаккцего устройства в следук1цих режимах: запись, стирание, считывание.

В режимах хранения и считывания запоминающий элемент (триггер 9) элемента памяти с тремя состояниями 3 может находиться в произвольном состоянии.

Формирователь работает следуютцим обP8901vt е

Режим хранения, На первую управляющую шину 5 разрешения считывания и на вторую управляющую шину 6 разрешения записи-стирания подается нулевой уровень напряжения, При этом уровень логического нуля на первой управляющей шине 5 запрещает запись информации в запоминающий элемент элемента памяти 3 с тремя состояниями, а на второй управляющей шине 6 обеспечивает формирование одинакового нулевого уровня напряжения на пря5639 4 ствует невыбрвнной шине строки матрицы накопителя, открывается ключ 1, через который выход формирователя подключае ся к общей шине 7.

Таким образом, в режиме записи в элемент памяти 3 предварительно записывается логическое состояние на вьиоде дешнфратора, затем дешифратор отключается и не оказывает влияние на выход формирователя, а формирователь записисчитывании формирует на выходе 4 напряжение в соответствин с состоянием .элемента памяти.

Режим стирания осуществляется точао так же, как и режим записи, только. с цомошью дополнительного коммутатора (внешнего) шина 8 подкпючается к обшей шине, а шина 7 — к внешнему источнику записи.

На фиг. 2 приведен вариант исполнения формирователи записи — считывания, в котором третье состояние (нулевое напряжение на обоих выходах) элемента памяти 3 формйруется с помошью логических элементов

И 10 н 11, когда на вторую управляющую шнну подается уровень логического нуля.

Предложенный формирователь записисчитывания для накопителя полупостоянного запоминающего устройства по сравнению с известными устройствами (4) повьццает быстродействие считывания ППЗУ не менее, чем в 1,25 раза, так как он не является промежуточным структурным элементом, включенным между дешифратором и шиной строки матрицы накопителя; уменьшается потребляемая мощность в режиме эапнси от-источника напряжения записи в 10 раз за счет осуществления коммутацйн aiba строки матрнцы накопителя ключами as МДП-транзисторах вмес то МДП- резисторов.

Кроме того, формирователь позволяет разработать микросхему ППЗУ с одннм источником питания, в которой напряжение записи формируется встроенным автономным преобразователем напряжения.

Формирователь записи-считывания может быть использован в ППЗУ, изготовляемой по любой технологии MLlTI-сгруатуре

3 103 мом н инверсном выходак элемента памяти 3, которые запирают ключи 1 и 2.

Режим считывания. Ключи 1 и 2 поддерживаются в закрытом состоянии аналогично режиму хранения, Таким образом, фор- мирователь записи-вчитывания не оказывает.влияния на работу своей. строки матрицы накопителя. Прн считывании поступакзцнй уровень логической единицы с выхода дешифратора 12 возбуждает эапоми- i(} нающее элементы 13 строки матрицы накопителя, осуществляя прн этом считывание информации подобно обычным полупостоянным запоминакзцим устройствам.

Режнм запнсн. Выбор формнрова теля зап си-считывания осуществляется дешифратором 12. Уровень логической единицы илн нуля с выхода дешнфратора 12 через шину 4 формирователя поступает, как и в режиме считываний, на информационный 20 вход элемента памяти 3 с тремя состояниями. Одновременно (нлн с.пронзвольной задержкой) с окончанием установления требуемого логического уровня as выходе дешнфратора-на первую управляю- 25 щую шину 5 подается снгнал с уровнем логической единицы и элемент памяти 3 устанавливается в состояние, соответствующее логическому уровню напряжения на выхсще дешнфратора.

Затем на управляющую шину 5 подается нулевой уровень напряжения н элемент памяти- 3 формирует новое состояние.

После этого дешифратор отключают илн (прй налнчни дополнительной зашиты выходного каскада дешнфратора от повышей ных напряжений) дешифратор оставляют включенным, а на вторую управляющую шину 6 подают напряжение уровня логической единицы. При этом на выходах элемента 3 формируются напряжения, со- 4О о тветствукнцие состоянию запоминающего элемента (трнггерной схемы) элемента памяти, которые подаются на управлякг щие ироды ключей 1 и 2.

Прн единичном состоянии элемента па-4 мяти 3, что.соответствует выбранной шине строки матрицы накопителя, дкиифратором 12 открывается ключ 2 и через него выход 4 формирователя подключаез ся к шине записи 8, а при нулевом состоянни элемента памяти 3, что соответ1 035639

Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва,:Ж-35, Рауысхая наб., д. 4/8

Заказ 5840/51

Фижпш ППП Патент", г. Ужгород, уп. Проектная, 4

Составитель О. Кулаков

Редактор Л. Весеиовская Техред A.Бабинеп Корректор А. Тяско