Устройство для деления аналоговых сигналов

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ АНАЛОГОВЫХ СИГНАЛОВ, содержащее первый и второй интеграторы, блок сравнения и источник опорного напряжения, выход первого интегратора соединен с ,первым входом блока сравнения,выход второго интегратора является выходом устройства,о тличающееся тем,что,с целью повышения точности-, работы,в него введены сумматор/инве| тор , первый, второй и третий переклюfff . nt6чатели , причем вход и выход инвертора соединены соответственно с первьад и вторым входами первого переключате ля , первый вход сумматора является первым входом устройства, вторым входом которого является вход инвертора, выход первого переключателя соединен с вторым входом сумматора, инвертирующий и неинвертирующий выхода которого подключены соответственно к перво:му и второму входам второго переключателя , выход которого соединен с входом первого интегратора, второй вход блока сравнения подключен к выходу третьего переключателя, первый и второй входы которого соединены соответственно с выходом источника опорного напряжения и с шиной нуле (Л вого потенциала, выход блока сравнения подключен к входу второго интегратора и к управляющим входам первого , второго и третьего переключате- « лей.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУЬЛИК (5g 006 6 7/161 "

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,К СВИДЕТЕЛЬСТВУ чатели, причем вход и выход инвертора соединены соответственно с первым и вторым входами первого переключате ля, первый вход сумматора является первым входом устройства, вторым входом которого является вход инвертора, выход первого переключателя соединен с вторым входом сумматора, ннвертирукнций и неинвертирующий выходы которого подключены соответственно к перво:му„и второму входам второго переключателя, выход которого соединен с входом первого интегратора, второй вход блока сравнения подключен к выходу третьего переключателя, первый и второй входы которого соединены соответственно с выходом источника I опорного напряжения и с шиной нулевого потенциала, выход блока сравнения подключен к входу второго интегратора и к управляющим входам первого, второго и третьего переключателей.

Я

Ъю

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

А0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3351419/18-24 (22) 30.10.81. (46) 23.08.83. Бюл. Р 31 (72) A.Ô.Ãðèøíîâ, A.Н.Гуляев И.Г.Дорух (53) 681.335(088.8) (56) 1. Авторское свидетельство СССР

9 456276, кл. G06G 7/16, 1973.

2. Авторское свья етельство СССР

У 798879, кЛ. 8064 7/.161, 1979 (прототип). (54)(57) 1. УСТРОЙСТВО,ЦЛЯ ДЕЛЕНИЯ

АНАЛОГОВЫХ СИГНАЛОВ, ссдержацее первый и второй интеграторы, блок сравне. ния и источник опорного напряжения, выход первого интегратора соединен с ,первым входом блока сравнения, выход второго интегратора является выходом устройства,о т л и ч а ю ш е е с я тем,что,с целью повышения точности. работы,в него введены сумматор,инвест. тор, первый, второй и третий переклюSV» 10 A .

1037278

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Известно устройство для деления аналоговых сигналов, содержащее -. 5 интеграторы, н ль-орган, источник опорного напряжения, ключи Pl), Это устройство характеризуется низкой точностью работы.

Наиболее близким по технической 10 сущности к предложенному является устройство для деления аналоговых сигналов, содержащее первый и второй интеграторы, нуль-орган, источник опорного напряжения f 2), 15

Недостатком известного устройства является низкая точность.

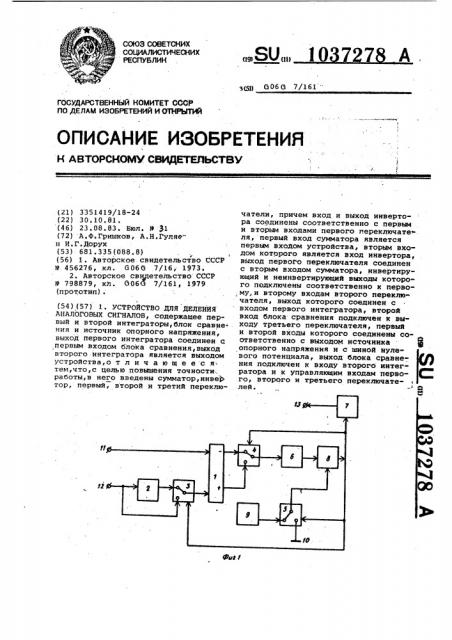

Целью изобретения является повышение точности работы. цель достигается тем, что н устрой- 0 ство для деления аналоговых сигналов, содержащее первый и второй ин" теграторы, блок сравнения и источник опорного напряжения, выход первого ии-4 тегратора соединен с первым входом блока сравнения, ныход второго интег-. ратора являешься выходом устройства, введены сумматор, инвертор, первый, второй и третий переключатели, причем вход и выход инвертора соедине" ны соответственно с первым и вторым входами первого переключателя, первый вход сумматора является первым входом устройства, вторым входом которого является вход инвертора, вы« ход первого переключателя соединен с вторым входом сумматора, инвертиру. ющий и неинвертирующий выходы которого подключены соответственно к перво. му и второму входам второго переклю.чателя,выход которого соединен с вхо-40 дом первого интегратора, второй вход блока сравнения подключен к выходу третьего переключателя, первый и второй входы которого соединены соответственно с выходом источника 45 опорного напряжения и с шиной нулевого потенциала, выход блока сравнения подключен к входу второго интегратора и к управляющим входам первого, второго и третьего переключателей (На фиг.1 дана функциональная схема предложенного устройства для деления аналоговых сигналов, ча фнг.2 — временные диаграммы, поясня» ющие его работу..

Устройство содержит сумматор 1, инвертор 2, первый 3, второй 4 и третий 5 переключатели, первый б и второй 7 интеграторы, блок 8 сравие ния, источник 9 опорного напряжения шину 10.нулевого потенциала, первый 60

)1 и ьторой 12 входы и выход 13.

Устройство для деления аналоговых сигналов работает следующим образом.

Пусть на первом входе ll действу" ет сигнал Х<(4), пропорциональный делимому, а на -втором входе 12 — сиг-, нал Xg(4), пропорциональный делителю.

При этом первый 3, второй 4 и третий 5 переключатели находятся в положении, изображенном на фиг.1, и йа входе первого интегратора 6 дейстнует сигнал

Ч„=-?. Х И) -м (+) 1

На выходе первого интегратора

„формируется линейно нарастающее нап .

;ряжение (фиг.2, а). При достижений этим напряжением уровня величины опорного напряжения источник 9 опор-ного напряжения (момент времени на фиг.2, а) блок 8 сравнения вырабатывает импульс, по которому срабатывают первый 3, второй 4 и третий 5 переключателя и перебрасываются в состояние, противоположное изображенному на фиг.1.

При этом на первый интегратор 6 поступает сигнал

Ч „= t . ()+ x H) 3

На его выходе Формируется линейно убывающее напряжение (Фиг.2, а). При ,достижении этим напряжением величины нулевого уровня (момент времени + на фиг.2, а) блок 8 сравнения вырабатывает импульс, по которому первый 3, второй 4 и третий 5 переключатели ноэвращаются в исходное состояние...

Далее сигнал на ныходе перного интег; ратора б нарастает и цикл повторяет- ся.

Таким образом, на выходе блока

8 сравнения вырабатывается периодическая последовательность импульсов (Фиг.2, б), которая усредняется с помощью второго интегратора 7. На выходе второго интегратора 7 Формируется сигнал (фиг.2, б), величина которого равна (3)

I где К - коэффициент передачи второФ го интегратора 7.

Т.е. на выходе 13 Формируется сигнал, пропорциональный частному от деления двух сигналов, действующих на первом 11 и втором 1,2 входах устройства.

По сравнению с известным .устройством предложенное устройство для деления аналоговых сигналов обладает новым качеством - более высокой точностью работы, полученной за счет того, что Формирование периодической импульсной последовательности производится одним и тем же интегратором.

1037278

Ф б

Составитель О.Отраднов

Редактор О.Половка Техред g.Тепер . Корректор A.Ôåðåíö

« @ а

Заказ 6013/52 . Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Х-35, Раушская наб., д.4/5

Филиал ППН Патент, г.ужгород, ул.Проектн я,4