Преобразователь перемещения в параллельный код

Иллюстрации

Показать всеРеферат

1 .ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ В ПАРАЛЛЕЛЬНЫЙ КОД, содержащий кодовый элемент , чувствительные элементы , расположенные по V-методу, выходы чувствительных элементов соединены с входами преобразования кода, отличающийся тем, что,с . целью повышения достоверности выходного кода преобразователя, в него введены регистр и формирователь запрещающего импульса, выход которого соединен с управляющим входом регистра , выходы преобразователя кода соединены с информационными входами регистра , при этом первый выход преобразователя кода соединен с первым управляющим входом формирователя запрещающего импульса, второй управляющий вход которого подключен к источнику опроса. О :л С«9 О со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

f1% (Н) -q g G 08 С 9/06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 1"=:

Н АВ ГОРСКОМУ СВИДЕТЕЛЬСТВУ

0 j tt Zt 14

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГГИЙ (21) 3426174/18-24 (22) 20,04. 82 (46) 23,08.83; Бюл. N 31 (72) В. Д. Лебедев, Б. Е. Морщихин и В. А. Стрелов (53) 68I.325(088.8) (56) 1.Меськин И.ВМотоэлектрические преобразователи угловой величины в цифровой код. Судпромгиз, 1962, с.913.

2. Авторское свидетельство СССР и 622138, кл. G 08 С 9/00, 1977 (прототип), : (54) (57) 1.ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ В ПАРАЛЛЕЛЬНЫЙ КОД, содержащий кодовый элемент, чувствительные элементы, расположенные по Ч-методу, выходы чувствительных элементов соединены с входами преобразования кода, отличающийся тем, что,с целью повышения достоверности выходного кода преобразователя, в него . введены регистр и формирователь sanрещающего импульса, выход которого соединен с управляющим входом регистра, выходы преобразователя кода соединены с информационными входами регистра, при этом первый выход преобразователя кода соединен с первым управляющим входом формирователя запре- щающего импульса, второй управляющий вход которого подключен к источнику опроса.

10373

2. Преобразователь по п.1, о тл и ч а ю шийся тем, что формирователь запрещающего сигнала содержит элементы НЕ, И, И-НЕ, ИЛИ-НЕ и элемент задержки, выход которого соединен с первым входом первого эле мента И-НЕ и через первый элемент

HE - с первым входом второго элемента И-НЕ, выход второго элемента И-НЕ соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента

И, выход элемента И соединен с вы09 ходом формирователя запрещающего импульса, первый управляющий вход которого подключен к второму входу второго элемента И-НЕ и входам элементов задержки и второго элемента

НЕ, выход второго элемента НЕ соединен с вторым входом первого элемента И-НЕ, выход которого соединен с вторым входом элемента ИЛИ-НЕ, второй вход элемента И соединен с вторым управляющим входом формирователя запрещающего импульса.

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровыми вычислительными устройствами, 5

Известен преобразователь перемещения в параллельный код, содержащий кодовый элемент, связанный с обьекточ перемещения, неподвижно укрепленные чувствительные элементы и преобразо; t0 вател кодов (I) .

Недост ком данного преобразователя является недостаточно высокая достояерность соответствия считываемого кода угловому положению вала вслед-15 ствие сравнительно большого времени преобразования двоично-сдвинутого кода в арифметический.

Наиболее близким к изобретению по технической сущности является преоб- 20 разователь перемещения в параллельный код, содержащий и-разрядный кодовый элемент, чувствительный элемент для первого разряда и по два чувствительных элемента на каждый последующий 25 разряд кодового элемента, Выходы чувствительных элементов всех разрядов подключены к входам преобразователя кода j2) .

Недостатком известного преобразователя является недостаточно высокая достоверность выходного кода, так как возможна ситуация считывания ложного кода во время переходных процессов преобразования двоично-сдвинутого кода в арифче иче:кии.

Целью изобретения является повышение достоверности выходного кода.

Поставленная цель достигается тем, что в преобразователь перемещения в параллельный код, содержащий кодовый элемент, чувствительные элементы, расположенные по V -методу, выходы чувствительных элементов соединены с входами преобразования кода, введены регистр и формирователь запрещающего импульса, выход которого соединен с управляющим входом регистра, выходы преобразователя кода соединены с информационными входами регистра, при этом первый выход преобразователя кода соединен с первым управляющим входом формирователя запрещающего импульса, второй управляющий вход которого подключен к источнику опроса. формирователь запрещающего сигнала содержит элементы НЕ, И, И-НЕ, ИЛИНЕ и элемент задержки, выход которого соединен с первым входом первого элемента И-НЕ и через первый элемент НЕ - с первым входом второго элемента И-НЕ, выход второго элемента

И-НЕ соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И, выход элемента И соединен с выходом формирователя запрещающего импульса, первый управляющий вход которого подключен к второму входу второго элемента И-НЕ и входам элементов,задержки и второго элемента HF, выход второго элемента HE соеди ен с . вторым

9 4 что t - задержки, вызванные временем перехода чувствительного элемента из состояния логического нуля в состояние логической единицы или из логической единицы в логический ноль. Формирователь 4 запрещающего сигнала с момента любого изменения состояния кода первого разряда формирует импульс запрета записи в регистр 12, длительность которого должна быть больше времени преобразования t . Импульс запрета формируется как при изменении состояния кода первого кода первого разряда из

"0" в "1", так и из "1" в "0".В первом случае импульс запрета записи формируется элементом И-НЕ 8 (фиг.3 д) из сигнала кода первого разряда непосредственно (фиг. 3 .а) и сигнала кода первого разряда, задержанного элементом 5 задержки (фиг.3 в) и проинвертированного элементом НЕ 6. Во втором случае импульс запрета записи формируется элементом И-НЕ 9 из задержанного элементом 5 задержки сигнала кода первого разряда и проинвертированного инвертором 7 сигнала кода первого разряда (фиг.3 б). Импульсы запрета записи (фиг.3 д и е) суммируются элементом ИЛИ-НЕ 10 (фиг.3 ж) и поступают на первый вход элемента И 11, запрещая поступление импульсов с выходов преобразователя 3 кода в регистр 12. Длительность импульсов запрета будет определяться элементом 5 задержки, поэтому ее следует выбирать чуть большей времени преобразования t> . В результате запись в регистр может произойти только после окончания преобразования двоично-сдвинутого кода в арифметический и запись ложных значений кода, ;появляющихся в переходные режимы пос-! ле изменения кода на выходах чувствительных элементов, будет исключена."

Ошибка преобразования при этом не будет превышать единицы младшего разряда.

Экономический эффект от использования предлагаемого преобр азователя определяется его техническими преимуществами,, 20

3 103730 входом первого элемента И-НЕ, выход которого соединен с вторым входом элемента ИЛИ-НЕ, второй вход элемента

И соединен с вторым управляющим вхо дом Формирователя запрещающего импыльса.

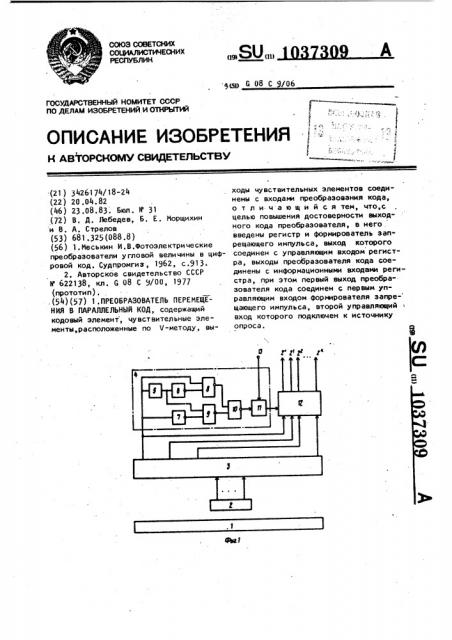

На фиг. 1 представлена структурная схема преобразования перемещения в параллельный код; на фиг. 2 - эпюры переходных процессов, возника- 10 ющих на выходе преобразователя кода при смене кода 0111 на 1000; на фиг. 3 - диаграммы работы элементов формирователя запрещающего импульса, 15

Преобразователь содержит кодовый элемент 1,чувствительные элементы 2, расположенные по V -методу считывания, преобразователь 3 кода, формирователь 4 запрещающего импульса, включающий элемент 5 задержки, элементы HE 6 и 7, элемен — И-НЕ 8 и 9, элемент ИЛИ-НЕ 10 и элемент И 11, регистр 12 и источник 13 опроса, Преобразователь работает следую- 25 щим образом.

При произвольном положении кодового элемента 1 чувствительные элементы 2 считывают информацию, которая преобразуется в цифровую форму и поступает на входы преобразователя

3 кода. Для записи выходного кода преобразователя во внешнее устройство используется формирователь 4 запрещающего импульса и регистр 13.

На фиг, 2 для примера показан процесс изменения четырехразрядного кода 0111 на код 1000 . Эпюры на фиг.2 (а,б,в и г) соответствуют изменениям кода первого, второго, третьего и четвертого разрядов на выходах преобразователя 3 кода. При V-методе считывания преобразователь 3 кода работае1 таким образом, что каждый последующий разряд начинает преобразование после окончания работы предыдущего. Поэтому при изменении кода будет иметь место задержка преобразования кода длительностью t l,.

Например, время преобразования кода

011l в код l000 будет соответствоватьь t = 4t >р, если условно счит ат ь, 1037309

1037309

ВНИИПИ Заказ 6016/53 Тираж 618 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4