Резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

37343 A ()9) (И) 3(я) G 11 С 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

l1O ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3446282/18-24 (22) 31.05.82 (46) 23.08.83. Бюл. 1(31 (72) Б.Н,Игнатов, В.А.Кривего, 0.H.Ìåæåâoâ и Ю.В.Шуленин (53) 681,327(088 8) (56) 1. Савченко IO.T. Цифровые устройства, нечувствительные к неисправностям элементов. И., "Советское радио", 1977, с. 26-31 рис.2,4.

2. Авторское свидетельство СССР

1 585549,кл.6 11 С 29/90,1977 (прототип). (54)(57) 1... .РЕЗЕРВИРОВАННОЕ ЗАПОИИ"

НАЮЩЕЕ УСТРОЙСТВО, содержащее основ-. ные блоки памяти и мажоритарный блок, выход которого соединен с входами регенерации основных блоков памяти, о т л и ч а ю щ е- е с я тем, что, с целью повышения надежности устройства, в него введены вычислитель контрольной суммы, блок переключе" ния каналов, дополнительные блоки памяти и элементы 2 И-ИЛИ, первые и вторые входы которых подключены соответственно к выходам основных и дополнительных блоков памяти, выходы " к входам мажоритарного блока, а третьи и четвертые входы - соответственно к первому и к второму выходам блока переключения каналов, третий и четвертый выходы которого соединены соответственно с первыми управляющими входами основных и до.полнительных блоков памяти, а первый вход подключен к вторым управляющим входам основных и дополнительных блоков памяти,и является входом обращения устройства, причем входы регенерац. и дополнительных блоков памяти соединены с выходом мажоритар" j ( ного блока и в ходами в ы числит еля контрольной суммы, выход которого подключен к второму входу блока переключения каналов, а управляющий вход является входом сигнала последнего адреса устройства.

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что блок переключения каналов содержит регистр, первый триггер, элемент ИЛИ, элемент И и генератор временных сигналов, выход которого подключен к первому входу элемента ИЛИ, выход которого соединен с установочным входом регистра и счетным входом первого триггера, выходы которого подключе- а ны соответственно к первым входам первого и второго элементов И, вторые входы которых соединены с выходом регистра и первым входом третьего элемента И, выход которого подключен к второму входу элемента ИЛИ, а второй вход соединен со счетным входом регистра и является первым входом блока, вторым входом которого является третий вход третьего элемента И; выходами блока с первого по четвертый являются соответ- ственно первый и второй выходы первого триггера и выходы первого и вто- ВФЛА рого элементов И.

3.. Устройство по и. 1-2, о т л и- ч а ю щ е е с я тем, что вычислитель контрольной суммы содержит второй триггер, элемент И-НЕ и сумматор.по модулю два, входы которого являются входами вычислителя, а выходы соединены с входами элемента И-HE выход которого подключен к первому входу второго триггера, второй вход и выход которого являются соответственно управляющим входом и выходом вычислителя .

1 1037

Изобретение относится к вычислительной технике и можег быть использовано в цифровых управляющих системах и комплексах, к которым предьявляются высокие требования к их надежности и безотказной работе в течение длительного срока эксплуатации.

Известно резервированное запоми,нающее устройство, которое содержит три идентичных канала, выходы кото- 10 рых через мажоритарный блок подключены к исполнительным органам 1.1 ).

Недостатком этого устройства является снижение надежности при длительном сроке эксплуатации. 15

Наиболее близким техническим решением к изобретению является резервированное запоминающее устройство, содержащее блоки памяти, выходы которых через мажоритарный блок подклю" чены к входам регенерации блоков памяти P2).

Недостатками известного устройства являются недостаточное время непрерывной работы, возможность частичной или полной потери информации при выходе из строя элементов или при возникновении однократного сбоя в в узлах регенерации информации блоков памяти, особенно при работе в тяжелых условиях эксплуатации,, резких изменениях климатических условий, условиях повышенйых помех, что снижает надежность устройства.

Дель изобретения - повышение на35 дежности резервированного запоминающего устройства, Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее ос- 40 новные блоки памяти и мажоритарный блок,„выход которого соединен с входами регенерации основных блоков памяти, введены вычислитель контрольной суммы, блок переключения каналов, дополнительные блоки памяти и элементы 2И-ИЛИ, первые и вторые входы которых подключены соответственно к выходам основных и дополнительных блоков памяти, выходык входам мажоритарного блока, а третьи и четвертые входы - соответственно к первому и второму выхо-.. дам блока переключения каналов, третий и четвертый выходы которого соединены соответственно с первыми управляющими входами основных и дополнительных блоков памяти, q первый вход подключен к вторым управляющим

343 с входам основных и дополнительных блоков памяти и является входом обращения устройства, причем входы регенерации дополнительных блоков памяти соединены с выходом мажоритарного блока и входами вычислителя контрольной суммы, выход которого подключен к в.торому входу блока переключения каналов, а управляющий вход, является входом сигнала последнего адреса устройства.

Кроме того, блок переключения каналов содержит регистр, первый триггер, элемент ИЛИ, элементы И и генератор временных сигналов, выход которого подключен к, первому входу элемента ИЛИ, выход которого соединен с установочным входом регистра и счетным входом первого триггера, выходы которого подключены соответственно к первым входам первого и второго элементов И, вторые входы которых соединены с выходом регистра и первым входом третьего элемента И, выход которого подключен к второму входу элемента ИЛИ, а второй вход соединен со счетным входом регистра и является первым. входом блока, вторым входом которого является третий вход третьего элемента И, выходами блока с первого по четвертый являются соответственно первый и второй выходы первого триггера и выходы первого и второго элементов И

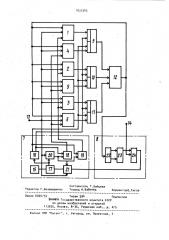

При этом вычислитель контрольной суммы содержит второй триггер, элемент И-НЕ и сумматор по модулю два, входы которого являются входами вычислителя, а выходы соединены с входами элемента И-НЕ, выход которого подключен к первому входу второго триггера, второй вход и выход которого являются соответственно управляющим входом и выходом вычислителя, На чертеже представлена функциональная схема предлагаемого устройства..

Резервированное запоминающее устройство содержит основные 1-3 и дополнительные 4-6 блоки памяти, блок

7 переключения каналов, вычислитель Г контрольной суммы, первый 9, второй 10 и третий 11 элементы

2И-ИЛИ и мажоритарный блок 12, вход 13 обращения и вход 14 сигнала последнего адреса. блок переключения каналов содержит генератор 15 временных сиг налов, первый триггер 16, элемент

ИЛИ 17, первый 18 и второй 19 эле менты И, регистр 20 и третий элемен

И 21. Вычислитель контрольной суммы содержит сумма1ор 22 по модулю два, элемент И-НЕ 23 и второй триггер 24.

Устройство выполнено на стандартных элементах типа 1601РР26.

Устройство работает следующим образом.

В исходном состоянии в блоки 1-6 10 по всем адресам записывается идентичная информация. По последнему адресу записывается контрольное число. Триггеры 16 и 24 и регистр 20 находятся в положении "0". По первому сигналу 15

"Обращение" на входе 13, поступающему на управляющие входы блоков 1-6, информация из блоков 1-3 памяти через элементы 2И-ИЛИ 9-11 и блок 12 поступает на вход сумматора 22, в ко-20 тором накапливается, и на информационные входы блоков 1-6.

При этом на первые управляющие, входы блоков, 1-6 с выходов элементов

И 18 и 19 поступает сигнал "0", за- 25. прещающий регенерацию информации.

В случае если информация, считанная,из блоков 1-3 памяти, правильная, на выходах сумматора 22 будут единичные сигналы высокого уровня, ЗО которые через элемент И-НЕ 23, инвертируясь, поступают на первый вход триггера 24, на второй вход 14 которого поступает сигнал последнего адреса. Таким образом, если инфор35 мация, полученная с блоков 1-3 правильная, по последнему адресу подверждается состояние "0" триггера 24, сигнал "0" которого запрещает прохождение второго сигнала "Обращение" с входа 13 через элементы И 21 и

ИЛИ 17 на вход триггера 16. Второй сигнал "Обращение" переключает регистр 20 в положение "Два", при котором сигнал с его выхода через элемент И 18 поступает на первые управляющие входы блоков 4-6, разрешая в них регенерацию информации сигналами из блоков 1-3 памяти.

В случае, если информация, полученная с выходов блоков 1-3 неправильная, на выходах сумматора 22 по окончании опроса зафиксируется число, не соответствующее "1" во всех разрядах.

Сигнал последнего адреса 14 переключает триггер 24 в состояние "1".

Второй сигнал "Обращение" с входа

13 устанавливает регистр 20 в состоя343 4 ние "0" и через элементы И 21 и

ИЛИ 17 переключает триггер 16 в протиааположное состояние. При этом информация с . выхо„ов блоков 4-6 поступает в вычислитель 8, Если информация правильная, следующий сигнал

".Обращение" переключает регистр 20 в состояние "Два", причем сигнал с его выхода через элемент И 18 разрешает перезапись (регенерацию) информации из блоков 4-6 в блоки 1-3, т.е. вычислитель 8, зафиксировав ошибку в информации в блоках 1-3,с помощью блока 7 производит корректировку информации в этих блоках. Сигнал с выхода генератора 15 (период которого выбирается исходя из условий эксплуатации и должен быть меньше времени, гарантирующего сохранность информации в блоках 1-6) через элемент ИЛИ 17 поступает на вход триггера 16 и установочный вход регистра 20, переключает триггер 16, который поочеред-. но разрешает регенерацию информации из блоков 1-3 в блоки 4-6 и обратно.

Таким образом, построение резервированного запоминающего устройства по данной структуре при первом обращении позволяет проконтролировать выходную информацию, по второму обращению осуществить - перезапись 1 регенерировать) информацию в резервные блоки памяти, в случае выхода из cTpoR узлов регенерации или какого-либо сбоя, и произвести запрет регенерации и переключение каналов блоков памяти, Это позволяет исключить потерю информации, увеличить время непрерывной работы и повысить надежность резервированного запоминающего устройства.

Время непрерывной работы без потери информации увеличивается до времени гарантированного ресурса работы накопительного элемента (10000 ч) так как в каждом блоке памяти происходит обновление информации через время, равное периоду регенерации, задаваемому генератором 15, и при периоде регенерации до 100 ч время сохранности информации в блоках 1-6 будет соответствовать времени максимальной наработки 10 ч (т,е. ресурсу работы накопительного элемента) при количестве циклов перезаписи информации, не превышающем заданное в ТУ на накопительный элемент.

Технико-экономическое преимущество предлагаемого устройства заключается а его более высокой надежности по сравнению с известным.

l037343

Составитель Т.Зайцева

Техред А.Бабинец

Редактор Г.Безвершенко

Коррек торО.Тигор

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 с

Заказ 6020/55 Тираж 594 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5