Оперативное запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

ОПЕРАТОВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее основной адрео ный накопитель, дешифраторы, усйпитепи, бпок сравнения, блок управления,блок ввода и вывода информации, счетчик импульсов , генератор сигнадюв, формирователи сигйалов и элементы ИЛИ, причем выходр первого дешифратора подклкчень к входам первого усилителя, выходы котор(го соединены с одними из входов ос но ного адресного накопителя, другие входы и выходы которого подключены соответственно к адресным выходам и одним из адресных входов второго усилителя, другие адресные вхошл которотю соединены с выходами второго , упра&ляюшие входы дешифраторов и усилителей подключены к выходам блока управления, первые выходы первого и второго формирователей сигналов соедннены соответс вен1ю с первыми входами первого и второго элементов ИЛИ, выходы которых подключены соответственно к первым и вто ,рым вхсч7Я1м блока ввода и вывода внфор мации, первый выход которого соединен с первым входом блока сравнения, второй вход которого подключен квторому выходу первого формирователя сигналов, а третий вход - к второму выходу вгорого формирователя сигналов, третий выход которого соединен с первым входом первого формирователя сигналов, второй вход которого подключен к первомувыходу генератора сигналов, второй выход которого соединен с первым входом счетчика импульсов, второй вход которого и первый вход генератора сигналов объедиие.ны и являются установочным входом устройства, первым и вторым управляющими входами которого являются вторые входы первого i и второго элементов И, а информационным входом устройства является третий вход W блока .ввода и вывода информации, отличающееся тем, что, с целью Повышения надежности устройства, в него. введены ассоциативный накопитель, допогм нитепьный адресный накопитель, коммутаторы , третий усилитель, сдвиговый регистр, третий и четвертый элементы ИЛИ, причем одни из выходов первого коммутатора соединены с входами первого дешифСА: ратора, а другие - с входами второго дешифратора и входами ассоци-. DO ативного накопителя, управляющий вход которого подключен к первому выходу ;О блока сравнения, а выходы - к входам второго коммутатора, выходы которого соединены с одними из адресных входов третьего усшитетш, другие адресные входы и адресные выходы которогр подключены к выходам и одним из входов дополнительного адресного накопителя,. другие входы которого соединены с выходами первого усилителя, входы треть;его элемента ИЛИ подключены соответст

1ОЗ7за9 венчаю к выходам считывания второго и третьего усилителей, входы записи которых и выход третьего элемента ИЛИ соединены соответственно с вторым выходом и четвертым входом блока ввода ! и вывода информации, третий выход генератора сигналов подключен к входу второго формирователя сигналов, а второй вход - к выходу четвертого элемента

ИЛИ, первый вход которого соединен с выходом сдвигового регистра, первый и

Изобретение относится к вычислитель ной технике, в частности .к запоминающим устройствам, и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении.

Известно оперативное запоминающее устройство с автономным контролем, ко. торое содержит накопитель, адресные и разрядные формирователи, дешифраторы, тактовый генератор, генератор тестовых последовательностей и схему сравнения(1).

Недостатками этого устройства являются большие аппаратурные затраты и низкая эффективность контроля, 15

Наиболее близким техническим решением к изобретению является оперативное запоминающее устройство с автономным контролем, содержащее накопитель, дешиф- . раторы, усилители, блок управления, блок щ ввода и вывода, счетчик, генератор, блок сравнения, "формирователи импульсов и элементы ИЛИ. Выходы первого дешифра тора подключены к входам первого ycuwrens, выходы которого соединены с входами накопителя, другие входы которого соединены с выходами второго усилителя, входы которого подключены к выходам второго дешифратора, управляющий вход которого соединен с первым выходом .блока управления, другие выходы которого подключены соответственно к управляющим входам первого дешифратора, первого и второго усилителя. Первмй вход блока ввода и вывода соединен с выходом первого элемента ИЛИ, второй вход соединен с выходом второго элемен та ИЛИ, а выход подключен к первому входу блока сравнения, второй вход ,ко горого соединен с первым выходом пер второй входы которого подключены соответственно к первому входу генератора сигналов и второму выходу блока сравнения, третий выход которого и второй вход четвертого элемента ИЛИ соединены соответственно с третьим входом и одним из выходов счетчика импульсов, другие выходы которого подключены к одним из входов первого коммутатора, другие входы которого являются адресными входами устройства.

horo формирователя импульсов, второй выход которого соединен с вторым входом первого элемента ИЛИ, первый вход которого является первым внешним входом устройства. Третий вход блока сравнения подключен к третьему выходу второго формирователя импульсов, первый выход которого соединен с вторым входом второго элемента ИЛИ, первый вход которого является вторым внешним. входом устройства. Третий вход блока сравнения подключен к третьему выходу второго формирователя импульсов, первый выход которого подключен к второму входу второго элемента ИЛИ, первый вход которого является вторым внешним входом устройства. Второй выход второго формирователя импульсов подключен к первому входу первого формирователя импул сов, второй вход которого соединен с вторым выходом генератора, второй выход которого соединен с первым входом счетчика, а первый вход соединен с вторым входом счетчика и третьим внешним входом устройства (2) .

Недостатком известного устройства является низкая эффективность контроля, обусловленная отбраковкой микросхем после выявления первого же неисправного элемента памяти, что снижает надежность устройства.

Цепь изобретения - повышение надежности устройства.

Поставленная цепь достигается тем, что в оперативное запоминающее устройство с автономным контролем, содержащее основной адресный накопитель, дешифраторы, усилители, блок сравнения, блок управления, блок ввода и вывода иь

1 03 "(349 4 формации, счетчик импупьсов, генератор

1 сигнапов формирователи сигнапов и эпе ., ) менты ИЛИ, причем выхоцы первого дешифратора подключены к входам первого усипителя, выходы которого соединены с одними иэ входов основного адресного накопитепя, другие входы и выходы которого подключены соответственно к адресным выходам и одним из адресных входов второго. усипителя, другие адресные входы 10 . которого соединены с выходами второго дешифратора, управляюшие входы дешифра= торов и усилитепей подкпючен к выходам блока управления, первые выходы первого и второго формирователей сигналов соеди-1 иены соответственно с первыми входами первого и второго элементов ИЛИ, выходы которых подключены соответственно к первым и вторым входам блока ввода и вывода информации, первый выход которо- о го соединен с первым входом блока суаа нения, второй вход которого подкпючен к второму выходу первого формирователя сигнапов, а третий вход - к второму выходу второго формироватепя сигналов, 5 третий выход которого соединен с первым входом первого формирователя сигналов, второй вход которого подкпючен к первому выходу генератора сигнапов, второй выход которого соединен с первым вхоцом счетчика импульсов, второй вход которого и первый вход генератора сигналов объединены и являются установочным входом устройства, первым и вторым управпяюшими входами которого явпяются вторые входы первого и второго эпементов И, а

35 информационным входом устройства является третий. вход бпока ввода и вывода информации, введены ассоциативный накопитель допопнительный адресный накопиЭ

40 тень, коммутаторы, третий усилитель, сдвиговый регистр, третий и четвертый элементы ИЛИ, причем одни иэ выходов первого коммутатора соединены с входами первого дешифратора, а другие выхо45 ды — с входами второго дешифратора и входами ассоциативного накопителя, управпяюший вход которого подключен к первому выходу блока сравнения, а выходы-. к входам второго коммутатора, выходы которого соединены с одними иэ адресных 5О входов третьего усилителя, другие адресные входы и адресные выходы которого подкпючены к выходам и одним иэ входов дополнительного адресного накопителя, другие входы которого соединены SS с выходами первого усипителя, входы третьего элемента ИЛИ подключены со ответственно к выходам считывания второго и третьего усшштелей, входы записи которых и выход третьего элемента ИЛИ соединены соответственно с вторым выхо-. дом и четвертым входом бпока ввода и вывода информации, третий выход генератора сигнапов подкпючен к вхрцу второго формироватепя сигналов, а второй входк выходу четвертого элемента ИЛИ, первый вход которого соединен с выходом сдвигового регистра, первый и второй входы которого подключены соответственно к первому вхоцу генератора сигналов и к второму выхоцу бпока сравнения, третий выход которого и второй вход четвертого эпемента ИЛИ соединены соответственно с третьим входом и одним из выходов счетчика импупьсов, другие выходы которого подключены к одним иэ входов первого коммутатора, другие входы которого являются адресными входами устройства.

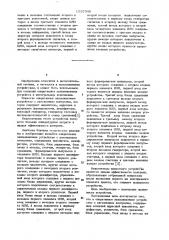

На чертеже .приведена функциональная схема предпагаемого устройства.

Устройство содержит первый дешифратор 1, первый усипитепь 2, основной адресный накопитель 3, бпок 4 управнения, второй усилитель 5, второй дешифратор

6, первый коммутатор 7, допопнительный адресный накопитепь 8, третий усипитепь

9, первый эцемент ИЛИ 10, второй коммутатор 11, ассоциативный накопнтепь

12, блок 13 ввода и вывода информации, счетчик 14 импульсов, второй 15 и третий 16 элементы ИЛИ, сдвиговый регистр.

l7, блок 18 сравнения, первый 19 и второй 20 формирователи сигналов, генератор 21 сигналов и четвертый эпемент

ИЛИ 22.

Устройство работает следующим образом.

Внешним сигналом "Автоном, посту- паюшим на установочный вход устройства, устанавпиваются в начальное состояние счетчик 14, регистр 17 и запускается генератор 21, Счетчик 14 и формирователи 19 и 20, управляемые выходными сигналами генератора 21, обеспечивают работу устройства в режиме проверки работоспособности ячеек памяти накопите» ля 3, причем счетчик 14 обеспечивает последоватепьный перебор ячеек памяти при тестировании, формироватепь 19 вырабатывает внутренние сигналы Запись

/считывание» а формироватепь 20 вырабатывает внутренние сигналы. Элементы

ИЛИ 15 и 16, а также коммутатор 7 управляют поступпением на дешифраторы

1 и 6 и блок 13 сигнапов либо с внеш1 037349 них, входов устройства, либо с выходов внутре нних бпоков.

Выбор функционального теста, реапиэуемого на основе перечиспеннык бпоков, определяется в первую очередь особен- 5 ностями технологического процесса, а также емкостью накопителей, мощностными и временными параметрами устройства.

Пусть в качестйе функционапьного тео1 та выбран тест "Последовательная запись-"0 считывание". В ходе тестирования считываемая информация поступает из бпока

1 3 в блок 18, где она сравнивается с истинной информацией. Если бпок 18 вырабатывает сигнап совпадения, то по 15 приходу следующего сигнала с выхода генератора 21 счетчик 14 формирует адрес спедующего эпемента памяти накопителя 3, Если считываемая информация вэ совпадает с истинной, бпок 18 выра- . 20 батывает сигнал Ошибка, поступающий на регистр 17, счетчик 14 и накопитель

12. Этим сигналом производится запись адреса неисправного элемента памяти накопителя 3 в строку ассоциативных элементов памяти накопителя 12, которому соответствует эпемент памяти накопителя 8. Адрес очередного проверяемого эпемента памяти поступает как на входы дешифраторов 1 и 6, так и на входы на- 30 копитепя 12, где сравнивается одновременно со всеми хранимыми адресами неисправных элементов памяти. При сов падении адресов коммутатор 11 выбирает соответствующий резервный элемеит па мяти из накопителя 8 дня считывания или записи.

Дпя проверки работоспособности элементов памяти накопителя -8 сигнал: Ошибка" блокирует счетчик 14 на вре- 40 мя, необходимое дпя зациси и считывания из соответствующего эпемента памяти накопИтеля 8 погических сигнапов l u

0 . Если элемент памяти накопителя 8 окаэапся также неисправным, после его замены иа следующий элемент памяти накопителя 8 по крайней мере две строки накопителя 12 будут хранить одинаковый адрес из которых коммутатор 11 выбирает ту,. в которую адрес записан позднее, Останов генератора 21, т.е. окончание проверки, происходит пибо по сигналу с выхода счетчика 14, поступающего на второй вход эпемента ИЛИ 22 и означающего завершение выполнения теста, либо по сигнану с выхода регистра 17, означающего превышение числа обнаруженных неисправны х эпементов памяти накопитепя 3 над чиспом эпементов памяти накопителя 8, что означает отбраковку микросхемы памяти в накопителе 3.

В режиме внешних обращений, т. е. поспе окончания внутреннего тестирования, совпадение внешнего адреса с адресом, хранимым в накопитепе 12, означает автоматическую замену неисправного элемента памяти накопитепя 3 на исправный эпемент памяти из накопителя 8.

Внутреннее тестирование может начинат ся при подкпючении питания к устройству (без внешнего сигнала Автоном ), дпя чего установочный вход устройства допжен быть подклеен к шине питания.

Таким образом, отбраковка микросхемы памяти в контролируемом накопитепе выпопняется при обнаружении опредепенного (бопее чем одного) числа неисправных элементов памяти в ней, за счет чего повышается надежность устройства.

Технико-экономическое преимущество предпоженного устройства эакпючается в его бопее высокой надежности по сравн нию с известным

1 037349

ВНИИПИ Заказ 6020/55. Тираж 594 Поиписное

Филиал ППП Патент, г . Ужгорол, ул. Проектная, 4