Дешифратор на @ входов с контролем

Иллюстрации

Показать всеРеферат

ДЕШИФРАТОР НА П ВХОДОВ С КОНТРОЛЕМ, содержащий 2 дешифрирующих ячеек, каждая из которых содержит эпе мент И, причем выкоды эпементов И всех дешифрирующих ячеек являются первой группой выходов дешифратора , каждый 1-й( 1,2,...,п) информационнь й вход дешифратора соединен с соответствующими входами эпементов И 2 /2дешифрирующих ячеек, причем первый информационный вход дешифратора соединен с соответствующими входами эпементов И четной (нечетной) группы из дешифрирующих ячеек, второй информационный вход дешифратора соединен с соответствующими входами эпементов И двух четных (нечетных.) групп дешифрирующих ячеек, п -и информационный вход дешифратора соединен с соответствующими входами элементов И четных (нечетных) дешифрирующих ячеек, отличающийся тем, что, с целью повышения быстродействия контропя, в дешифратор введены Ъ сумматоров по модулю два, () и () дешифрирующие ячейки, а каждая из ()-х -...J дешифрирующих ячеек дополнительно сендержит элемент ИЛИ, п входов которого соединены с соответствующими входами элемента И этой же дешифрирующей ячейки , выкоды элементов И н ИЛИ 2 дешифрирующих ячеек соединены с соответствующими входами

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧ ЕСНИХ

РЕСПУБЛИК а «»с»

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3376754/1 8«24 (22) 04.01.82 (46) 30.08.83. Бюп. № 32 (72) А. П. Горяшко и И.Л. Сигапов (53) 681.3 (088.8) (56) 1. Авторское свицетепьство СССР № 408310, кп. G 06 F 11/10, 1972.

2. Авторское свицетепьство СССР

¹ 873235, кл. 6 06 F 5/02, С 06 F 11/26, 1979 (прототип), (54)(57) ДЕШИФРАТОР НА и ВХОДОВ

С КОНТРОЛЕМ, содержащий 2 дешифрируюших ячеек, каждая из которых содержит элемент И, причем выходы эпементов И всех дешифрирующих ячеек являются первой группой выходов дешифратора, каждый i-,é (=1, 2,..., и ) информационный вход дешифратора соединен с соответствуюшими входами эпементов И п!

2 2цешифрируюших ячеек, причем первый информационный вход дешифратора соединен с соответствуюшими входами эпементов И четной (нечетной) группы иэ

2" /2 цешифрирующих ячеек, второй информационный вход дешифратора соединен с соответствующими входами эпементов И двух четных (нечетных) групп из 2 /2 дешифрируюших ячеек, и -й информационный вход дешифратора соединен с соответствуюшими входами элементов И четных (нечетных) дешифрирующих ячеек, о тл и ч а ю ш и и с и тем, что, с целью повышения быстродействия контропя, в дешифратор введены и сумматоров по модулю цва, (2 +1) и (2" + 2) дешифрируюшие ячейки, а каждая из (2 +2)-х

„.SU„„1038934 А дц .5 06 F 5/02; 5 06 F 11/26 дешифрируюших ячеек допопнитепьно содержит элемент ИЛИ, и входов которого соединены с соответствуюшими входами элемента И этой же дешифрируюшей ячейи ки, вь1ходы элементов И и ИЛИ 2 дешифрируюших ячеек соединены с соответи ствуюшими вхоцами (2 +1 )-й дешифрирующей ячейки, выходы которой являются второй группой выходов цешифратора, управляющий вход которого соединен с первыми входами и сумматоров по моцупю два, второй вход каждого иэ и сумматоров по модулю два соединен с соответствуюшим j -м информационным входом дешифратора, выход каждого иэ сумматоров по модупю два соединен с д соответствуюшим входом (2 +2)-й це шифрируюшей ячейки и с соответствуюшими входами элементов И2"/2 дешифрируюших ячеек, причем выход сумматора по С модупю два, соединенного с первым информационным входом дешифратора, сое- 2 динен с соответствуюшими входами элементов И нечетной (четной) группы иэ

2"/2 цешифрирующих ячеек, выход сумматора по модулю два, соединенного с вторым информационным входом дешифратора, соединен с соответствующими входами эпементов И нечетных (четных) групп иэ

2"Ндешифрирующих ячеек, выход сумма- 4 тора по модупю два, соединенного с и -м информационным входом дешифратора, со динен с соответствуюшими входами эпементов И нечетных (четных) дешифрирующих ячеек, выходы (2 +2)-й цешифрируи ющей ячейки явпяются третьей группой выходов дешифратора.

1 1ÎÝÝ

Изобретение относится к автоматике и вычиспитепьной технике и моиоэт быть испопьзовано при построении узпов дискретных устройств, входящих в состав бпоков память и процессоров.

Известен дешифратор с контролем, содержащий элементы И, ИЛИ, НЕ, регистр, выходы которого соединены с входами дешифратора и триггера четности, группы выходов дешифратора соединены соответственно с входами первой группы эпементов ИЛИ, одноименные выходьt каждой группы выходов дешифратора соединены соответственно с в-одами второй грутпы апементов ИЛИ (1 1

Недостаток данного цешифратора в том, что количество аппаратуры контропл дешифратора быстро нарастает с увепичением числа его выходов.

Наиболее бпизким к предпагаемому по технической сущности явплется цешифратор,„содержащий группу эпементов ИЛИ и две группы цешифрирующих ячеек, каждая из которых содержит четыре элемента И., два эпемента НЕ, два информационны" и два управдяющих входа, причем первые информационные входы дешифрирующих ячеек второй групты объединены и явпяют сл первым информационным входом дешифратора, вторые информационные входы

30 дешифрируюших ячеек второй группы объецинень и являются вторым информационным входом цешифра тора, управпяющие входы каждой из дешифрирующих ячеек второй группы подкпючены к выходам соответствующей пары элементов ИЛИ, первые входы всех элементов ИЛИ обьецинены и явпяются третьим управпяющим входом дешифратора, выходы каждой цешифрирующей ячейки второй грушь явпяютсл группой выходов дешифратора, управпяющие входы каждой дешифрирующей ячейки первой группы объединены и явпяютсл соответственно первым и вторым управпяющими входами дешифратора, информационные входы дешифрирующих 45 ячеек первой грунты являются группой информационных входов дешифратора, каждый -й вход К-й дешифрирующей ячейки первой группы:оецинен с вторыми входами Р-х элем нтов ИЛИ группы 50

Р =16(к-1 }+4(-1) +, гце Р 1-4, к 1-2, 1 = 1-4 I 23.

Недостатками известного цешифратора явплютсл аюжность его структуры и относительно низкое быстродействие конт- 5 ропя, требующего увеличения чиспа тестовых проверок с ростом числа выходов дешифратора.

934 2 цепь изобретения - повышение быстродействия контропя.

Поставленная цепь достигается тем, что в цешифратор на и входов с контролем, содержащий 2 дешифрирукеиих ячеек, каждая из которых содержит элемент И, причем выходы эпементов И всех дешифрирующих ячеек явпяются первой группой выходов цешифратора, каждый i-й (1 1, 2,..., ) информационный вход дешифратора соецинен с соответствующими входами эцементов И 2 "/2 дешифрирующих ячеек, причем первый информационный вход цешифратора соединен с соответствующими входами элементов И четной (нечетной) группы из 2 (2цешифрирующих ячеек, второй информационный вход дешифратора соединен с соответствующими входами эпементов И двух четных (нечетных) групп из 2 /Ф цешифрирующих ячеек, и -й и формационный вход дешифратора соединен с соответствующими входами эпементов

И чегнь х (нечетных) дешифрирующих ячеек, введены и сумматоров по модулю два, (2 +1) и (2 "+2) цешифрирующив ячейки а каждая из (2 +2)-х дешифрирующих ячеек допопнитепьно содержит эпемент ИЛИ, и вхоцов которого соединены с соответствующими входами эпемента И этой же дешифрирующей ячейки, выходы элементов И и ИЛИ 2 цешифрирующих

h ячеек соединены с соответствующими входами (2" +1)-й цешифрирующей ячейки, выходы которой явпяются второй груттой выходов дешифратора, управпяющий вход которого соединен с первыми входами сумматоров по модупю два, второй вход каждого из сумматоров по модупю два соединен с соответствующим 1 -м информационным вхоцом дешифратора, выхоц каждого нз е сумматоров по моцупю цва соединен с соответствующим входом (2 +2)-й дешифрирующей ячейки и с соответствующими входами эпементов И дешифрирующих ячеек, причем выход сумматора по модупю два, соециненного с первым информационным входом дешифра. тора, соединен с соответствующими входами элементов И нечетной (четной) группы

>и из 2 дешифрирующих ячеек, выход сумматора по модупю цва, соединенного с вторым информационным входом дешифратора, соединен с соответствующими входами элементов И нечетных (четных) групп и из Ф дешифрирующик ячеек, выход сумh7 матора по модулю цва, соециненного с

П -м информационным входом цешифратора, соединен с соответствующими входами

3 1038934

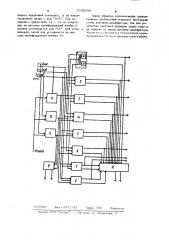

4 элементов И нечетных (четных) дещчфри- В рабочем режиме на управляющий рующих ячеек, выходы (2 +2)-й дешиф» вход подается единичный потенциал. При рирующей ячейки являются третьей груп- этом каждый из сумматоров 11 - 13 пой выходов дешифратора. по модулю два будет реализовывать функНа чертеже представлена блок-схема 5 цию инверсии входного информационного одного из вариантов дешифратора íà > сигнала. Логическая функция, реализуемая входов с контролем дешифратора на три сумматорами по модулю два, имеет вид входа.

3-Сх +СХ (1)

Схема содержит дешифрирующие ячейки 1

1-10, сумматоры 11-13 по модулю 0 где м - выходное значение сигнала сумдва, элемент И 14 и элемент ИЛИ 15. матора;

Дешифратор имеет три информационных с - входной управляющий сигнал; и один управляющий входы. Выходы эле- х - входной информационный сигнал. ментов И дешифрирующих ячеек 1-8 При с =1, 1 = х.. составляют группу информационных выхо»- В зависимости от значения приходядов дешифратора, а выходы дешифрирующих щего кода на выходе одной иэ дешифрируячеек 9 и 10 — две группы выходов для ющих ячеек 1-8 появится выходной сигрезультатов контроля работы дешифратора. нал. Состояние выходов дешифратора в

Дешифратор работает следующим обба- зависимости от входного кода характеризом. зуется таблицей истинности.

0 0 0 1 О 0 0 0 0 0 0

1 0 0 0 1 0 0 0 0 0 0

0 1 0 0 0 1 0 0 0 0 0

1 1 0 0 0 0 1 0 0 0 0

0 О 1 0 0 0 0 1 0 0 0

1 0 1 0 0 0 0 0 1 0 0

0 1 1 0 0 0 0 0 0 1 0

1 1 1 0 0 0 0 0 0 0 1

При контроле решается задача обнару- 40 жения любых кратных неисправностей типа константа ноль и константа единица . Константные неисправности являются моделями физических неисправностей типа обрыв и короткое замыкание. 45

В режиме контроля на управляющий вход дешифратора подается нулевой по»тенциал. Сумматоры 11 - 13 при этом выполняют функцию передачи соответствующего входного информационного сигна- 50 ла (см. уравнение 1). На первый, второй и третий информационные входы дешифратора подается первый тестовый набор:

"111". На входах дешифрирующих ячеек

1 «8 при этом появятся единичные по- 55 тенциалы, что, в свою очередь, приведет к появлению на втором и третьем выходах дешифратора кода 11 .

После проверки дешифратора первым тестовым набором необходимо подать на его информационные входы вторую тестовую комбинацию 000 . При этом в случае исправного дешифратора на всех выходах элементов И 14 и ИЛИ 15 дешифрирующих ячеек 1-8, а также на втором и третьем выходах дешифратора должен установиться код 00".

Первая и вторая тестовые комбинации обеспечивают проверку дешифрирующих ячеек 1-10 и информационных входов сумматоров 11-13, а также проверку утэравляющего входа дешифратора на обрыв и на отсутствие на нем единичного потенциала. Для проверки управляющего вхо да на отсутствие замыкания его на корпус используется третий тестовый набор, для чего необходимо на управляющий вход

Таким образом, испо1пзование редпагаемого изобретения повышает быстродействие контроля дешифратора, так как количество тестовых проверок равно трем и

5 не зависит от числа выходов дешифратора.

Кроме того,упрошается оборудование,выра-, батываю нее тесты,и сокращается е я объем.

1038934 подать единичный потенциал, а на информационные входы - код 900 . При коправных сумма орах 11 — 1 Э по модулю два на выходах дешифрирукппей ячейки 9 допжен установить=я код "11 . При атом неважно, какой код установится на выходе дешифрируюяей ячейки 10.

Б!1И ИПИ Заказ 6231 /55 Тираж 706 Подписное ц илиал ППП "Патент,;. Ужгород, ул. Проектная, 4