Преобразователь двоичного кода во временной интервал

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗЬВАТЕЛЬ ДВОИЧНОГО КОДА ВО ВРЕМЕННОЙ ИНТЕРВАЛ, содер- j жащий. триггер, генератор тактовых ; импульсов и счетчик,о т л и ч а ю-А ttt и и Ся тем, что, с целью повытения надежности, в него введены кодирующий блок на двухпоэиционных коммутаторах и регистр сдвига,- выход которого через триггер подключен к входу генератора Тактовых импульсов , выход которого соединен с входом счетчика и с первыми входами нечетных двухпоэиционных комму .таторов кодирующего блока, первые входычетных двухпоэиционных коммутаторов кодирующего блока соединены с выходом, первого ра:эряда счетчика и с предпоследнего разряда регистра сдвига, вход последнего разряда которого соединен с вторым входом первого двухпозиционного коьо утатора кодирующего блока, причем выходы двухпоаиционных коммутаторов кодирующего блока подключены к остальным входам разрядов регистра сдвига а вторые входы двухпозициоиньк коно утаторов кодирующего блока соединены с разрядными выхода (Л ми счетчика.

„„ () „„1039028.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3 5 > Н 03 К 13/20, Н 03 К 13/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A8TOPGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) (22) 23.12.81 (46) 30е08 ° 83. Бюл. Р 32 (72) В.Д.Лукьянов и С.П.Иванов (53) 621.317(088.8) (56) 1. Авторское свидетельство СССР

Ю 567204, Н 03 К 1 3/02, 1,977.

2. Авторское свидетельство СССР

9.363207, кл. Н. 03 К 13/20, 1973. (54)(57) ПРЕОБРАЗЬВАТЕЛЬ ДВОИЧНОГО

КОДА ВО ВРЕИЕННОН ИНТЕРВАЛ, содержак ий триггер, генератор тактовых . ймпульсови счетчик,о т л и ч а ю- шийся тем, что, с целью повы- шения надежности, в него введены кодирующий блок на двухпоэиционных коммутаторах и регистр сдвига; выход которого через триггер подключен к входу генератора тактовых им« пульсов, выход которого соединен с входом счетчика и с первыми входами нечетных двухпоэиционных комму,таторов кодирующего блока, первые входы- четных двухпоэиционных коммутаторов кодирующего блока соединены с выходом. первого разряда счетчика и с вхоцом предпоследнего разряда регистра сдвига, вход последнего разряда которого соединен с вторым входом первого двухпозиционного коммутатора кодирующего блока, причем выходы двухпоэиционных коммутаторов кодирующего блока подключены к остальным входам разрядов регистра сдвига, а вторые входы двухпозиционных коммутаторов кодирующего 3 блока соединены с разрядными выходами счетчика.

1039028

Изобретение относится к импульсной технике и может быть использовано в устройствах, преимущественно на феррит-транзисторных ячейках, обеспечивающих программное управление.

Известны преобразователи кода во временной интервал, содержащие генератор импульсон эталонной частоты, счетчик импульсов, кодирукицее устройство, схему совпадения и другие элементы !1 3.

Однако нестабильность положения заднего фронта счетного импульса приводит к увеличению погрешности преобразования.

Наиболее близким по технической сущности к предлагаемому является преобразователь, содержащий генератор импульсов, счетчик импульсон, кодирующее устройство, блок совпадения, делитель частоты, блок управления, лемент задержки, элементы И. Временной интервал задается кодом, который вводят подключением соответствующих разрядов дноичного счетчика к блоку совпадения (2 ).

Недостатками известного устройства являются ошибка преобразования,. которая возникает вследствие задержки сигналов в счетчике, и рассогласования во времени сигналов на входе элемента И, поступающих от блока совпадения и генератора импульсов.

Цель изобретения — повышение надежности работы. преобразователя.

Поставленная цель достигается тем что в преобразователь двоичного кода но нременной интервал, содержащий триггер, генератор тактовых иипульсон и счетчик, введены кодирующий блок на двухпозиционных коммутаторах и регистр сдвига, выход которого через триггер подключен к входу генерагора тактовых импульсов, выход которого соединен с входом счетчика и с первыми нхоцами нечетных двухпоэиционных коммутаторов кодирующего блока, первые входы четных двухпозиционных коммутаторов кодирующего блока соединены с выходом первого разряда счетчика и с нходом предпоследнего разряда регистра сдвига, вход последнего разряда которого соединен с вторым входом первого днухпозиционного коммутатора кодирующего блока, причем выходы двухпозиционных коммутаторов кодирующего блока подключены к остальным входам разрядов регистра сдвига, а вторые входы днухпозиционных коммутаторов кодирующего блока соединены с разрядными выходами счетчика.

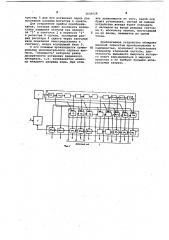

На фиг. 1 приведена блок-схема преобразователя двоичного кода во временной интервал; на фиг. 2 график работы.

Преобразователь содержит генератор 1 импульсов, счетчик 2 на феррит-транзисторных ячейках двоичного счета Т21-Т2й, кодирующий

5 блок 3 на двухпозиционных коммутаторах, регистр 4 сдвига на ферритовых ячейках, триггер 5, входная шина б, шина 7 двоичного кода.

Устройство работает следующим образом.

В исходном состоянии все разряды счетчика 2 и регистра 4 сдвига, за исключением первой ячейки, находятся в состоянии "0", в первую ячейку записана "1". 35 Состояние коммутаторов кодирующего блока 3 соответствует поданным на их входы кодовым сигналом, посту.пающим по шине 7. Момент подачи сигнала на шину б триггера 5 совпадает с началом преобразования. При этом генератор 1 импульсов начинает вырабатывать импульсы тактовой частоты.

- Во время работы счетчика 2 на выходах его разрядов образуются такто25 вые импульсы с периодами, кратными

2 веЛМчине:--- и сдвинутые по фазе " о между сЬбой на время, равное длительности импульса на выходе разряда счетчика 2.

На коммутаторы кодирующего блока 3 поступают тактовые сигналы с разрядов счетчика 2, участвующих в дешифрации кода, и вспомогатель ные тактовые сигналы с младших разрядон счетчика 2.

F До окончания формирования интервала -„- > т.е. до момента выхода

О сигнала сс старшего разряда счет40 чика 2, все разряды регистра 4 сдвига„ кроме первого, опрашиваются по тактовым нходам на считывание "1".

Изменение состояния регистра сдвига 4 .при этом не происходит. В момент

45 выхода сигнала на пеРвый разРяд регистра 4 сдвига происходит пере.нос ."1" иэ первого разряда во второй разряд регистра „4.„ через интервал 2 происходит

Fo

50 считывание "1" с второго и запись ее в третий разряд регистра 4 сдвига, фиксируя тем самым момент сложения днух интервалов 2 и 2 о Fo

55 Перенос "1" из третьего в пятый разряд регистра 4 сдвига производит-, ся сигналами вспомогательных тактовых частот F и Я во время формиF

2 й-4 рования интервала — . В момент

Fp окончания укаэанного интервала на выходе пятого регистра 4 сдвига появляется сигнал, соответствующий трем, слагаемым в преобразованном ко- . де 10011. Палее сигнал поступает на и 3 1() 39028

ЯУеаФгмюа кИ

Рвв.1 триггер 5 для его остановки через два последних разряда регистра 4 сдвига.

Для устранения ошибки преобразФвания, которая может возникать вследствие задержки сигнала при переносе "1" в счетчике 2 и переносе "1" в регистре 4 сдвига, последний разряд регистра 4 сдвига через тактовый вход подключен непосредственно к счетчику, минуя кодирующий блок 3.

С его помощью производится суммирование дополнительного отрезка времени, "весомость" которого равна дискретности установки временного интервала, т.е. зквивалентно единице младшего разряда кода. При этом вне зависимости от того, какой код будет установлен, сигнал на.выходе ,устройства всегда будет совпадать с сигналом на входе, разряда счетчика 2, поскольку сигнал, поступающий

5 на их входы, снимается из одной точки.

Предлагаемое устройство обладает высокой точностью преобразования и

1О надежностью, позволяет испольэовать генератор эталонной частоты, длительность выходного импульса которого может варьироваться в широких пределах и не требует больших аппаратурных затрат<

1039028

ВНИИПИ Заказ б241/59 Тираж 936 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектйая,4