Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накрпитель , информационные выходы которого подключены к одним информацисшным входам блока сравнения и являются информа 1(ионными вькодами устройства, выход 6iKvка сравнения является управлякпцим выходом устройства, адресные входы на ксшителя подключены к выходам пер вой и -второй группы счетчика, тактобый вход которого подключен к первому управляющему входу накопителя и являет ся первым управляющим входом устрейст&а, информационные входы накопителя подключены к выходам элементов ИЛИ, одни . . ВХОДЫ которых подключены к выходам первых элементов И, другие - к выходам вторых элементов И, одни входы которых являются {Щформаиионными входами уст ройства, другие подключены к выходу элемента НЕ, вход котс рогчэ подключен к одним входам первых элементов И и является вторьш упрсшляющим входом устрс ства, отлича.ющееся тем, что, с целью ловышення точности контроля , оно содержит коммутаторы и элемент ЗАПРЕТ, выход которого подключен к второму управляющему входу накопителя, первый вход элемента ЗАПРЕТ является третьим управляющим входом устройсотза, с S второй вход элемента ЗАПРЕТ подключен к соответствукицему выходу счетчика, (Л информационные входы коммутатора подклочены к соответствующим выходам первой группы счетчика, управляющие входы коммутаторов подключены к выходам второй группы счетчика, выходы коммутаторов подключе к Д1Щ11М входам блока сравнения, управяякшшй вход которого 4 О подключен к второму входу элемента ЗАПРЕТ. сл 1C О)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1040526 A (р 6 11 С 29/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

У

1 рд- р„, дд

ОПИСАНИЕ ИЗОБРЕТЕНИЯ/ ": : . ; ;, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3399266/18-24 (22) 22. 02Я2 (46) 07,09.83. Бюл. № 33 (72) О. В. Летнев и Ю. С. Шакарьянц (53) 681,327.6 (088.8) (56) 1. Авторское свидетельство СССР, № 750570, кл. Q 11 С 29/00, 1978, 2. Заявка Японии ¹ 54-41176, кл. С, 11 С 29/00, 1980 (прототип).(54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С САМОКОНТРОЛЕМ, содержащее нако-питель, информационные выходы которого подключены к одним информационным aio-. дам блока сравнения и являются информа ционными выходами устройства, выход -бло ка сравнения является управляющим вы- ходом устройства, адресные входы на; копите ля подключены к выходам пер вой и — второй группы счетчика, такто- . вый вход которого подключен к первому управляющему входу накопителя и является первым управляющим входом устрейотва, информационные входы накопителя подклю- . чены к выходам элементов ИЛИ, одни входы которых подключены к выходам первых элементов И, другие - к выходам вторых элементов И, одни входы которых являются информационными входами уст» ройства, другие подключены к выходу элемента НЕ, вход которого. подключен к одним входам первых элементов И и является вторыми управляющим входом устройства, о т л и ч а.ю щ е е с я тем, что, с цешао повышения точности контроля, оно содержит коммутаторы и .элемент ЗАПРЕТ, выход которого подключен к второму управляющему входу накопителя, первый вход элемента ЗАПРЕТ является третьим управляющим входом устройства, второй вход элемента ЗАПРЕТ подключен ф к соответствукицему выходу счетчика, еФОРмдднаддне адорф доммутатодд дод- (/) ключены к соответствукмцим выходам первой группы счетчика, управляющие axogaa коммутаторов подключены к выходам второй группы счетчика, выходы коммутато- ров подключены к другим входам блока ь ы сравнения, управлякяций вход которого подииочен к второму входу элемента

ЗАПРЕТ.

Сл

1 Щ4

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Известно устройство для контроля оперативной памяти, содержащее блок формирования тестовых последовательностей, . блок управления, адресный блок, блок подключения матриц, блок п-чати, блок обнаружения неисправностей, регистры, блок местного управления, схему срав- щ нения, элементы И и элемент HE 1 3.

Недостатком устройства является сложность, обусловленная применением формирователей тестовых последовательностей, требующих большого обьема оборудования.

Наиболее близкой к предлагаемой по технической сущности является система для проверки запоминающего устройства, содержащая счетчик, первую и вторую группы элементов И, элемент НЕ, группу элементов ИпИ, блок сравнения. К системе подключается проверяемый блок памя. ти. В этой системе источниками тестовой информации, записываемой в блок памяти, являются младшие разряды счет чика, выходы которого являются адресными входами блока памяти (2 1.

Однако такая система характеризуется невысокой достоверностью контроля, по-. скольку динамические качества адресного кода формирования теста слишком ограни« чены из-за различной скорости смены информации в разных разрядах блока памяти.

Бель изобретения — повышение точнос35 ти контроля.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель, ин40 формационные выходы которого подключены к одним информационным входам блока сравнения и являются информационными выходами устройства, выход блока сравнения является управляюшим выходом устройства, адресные входы накопителя

45 подключены к выходам первой и второй группы счетчика, тактовый вход которого подключен к первому управляющему входу накопителя и является первым управляющим входом устройства, информационные входы накопителя подключены к выходам элементов ИЛИ, одни входы кото. рых подключены к выходам первых элементов И, другие — к выходам вторых элементов И, одни входы которых являют 55 ся информационными входами устройства,, другие подключены к выходу элемента

НЕ, вход которого подключен к одним

0526 э входам первых- элементов И и является . вторым управляющим входом устройства, дополнительно содержит коммутаторы и элемент ЗАПРЕТ, выход которого под» ключен к второму управляющему входу накопителя, первый вход элемента ЗАПРЕТ является третьим управляющим входом устройства, второй вход элемента ЗАПРЕТ подключен к соответствующему выходу счетчика, информационные входы коммутатора подключены к соответствующим выходам первой группы счетчика, управляющие входы коммутаторов подкл чены к выходам второй группы счетчика, выходы коммутаторов подключены к другим входам блока сравнения, управляющий вход которого подключен к второму входу элемента

ЗАПРЕТ.

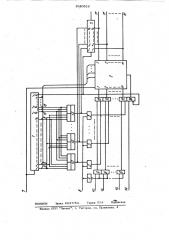

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит счетчик 1, служащий для задания кодов адресов проверяемого блока 2 памяти, блок 3 сравнения, элемент НЕ 4, первую группу элементов И 5, вторую группу элементов

И 6, управляющий вход 7 (вход синхронизации) устройства, управляющий вход

8 устройства, vn младших разрядов 9 счетчика 1, информационные входы 10 устройства, информационные выходы 11 устройства, группу элементов ИЛИ 12, коммутаторы 13, управляющий вход 14 (" Запись-считывание") устройства, 9 старших разрядов 15 счетчика, элемент ЗАПРЕТ 16.

Вход 8 и первая 5 и вторая 6 группы элементов И устройства предназначены для подключения к информационным входам блока 2 памяти либо младших п разрядов счетчика 1 (через коммутаторы 13), либо входных шин 10 устройства при работе от внешнего источника тестовой . последовательности.

Устройство работает следующим образом.

На входе 8 устройства устанавливаеч ся высокий уровень сигнала. Счетчик 1 обнуляется (цепи обнуления условно не показаны). На выходах 15 счетчика 1 присутствуют низкие уровни сигналов. Инфор— мационные входы коммутаторов 13 подключены к m младшим разрядам счетчика 1 таким образом, что выход каждого из rn разрядов счетчика 1 скоммутирован с выходом только одного (любого) коммутатора.

По входной шине 7 поступают импульсы синхронизации, при этом через элемент ЗАПРЕ Т 16 Разрешено прохождение

3 10405 импульсов записи на вход блока 2 памяти.

Теиущс.е значение кодов счетчика 1 по-ступает на адресные входы блока 2 па-. мяти, а на его информационные входы поступает текущее значение кодов млад ших rn разрядов счетчика 1 через «ом- мутаторы 13, открытую группу элементов И 6 и группу элементов ИЛИ 12.

Происходит рабочий цикл записи информании в блок 2 памяти. Через 2 адреса fo происходит изменение кода на выходах

15 счетчика 1 и к «аждому информацнойному входу блока 2 памяти коммутаторы

13 подключают другие разряды счетчика

1. Таким образом, в каждый разряд бао» g ка 2 памяти в различных шакалах (дтямтельностью 2 периодов синхрочастоты) записывается информация с различных младших разрядов счетчика 1, чем достигается выравнивание скорости смены иМ 2О формации в разных разрядах блока 2 памяти, т. е. динамические качества про» верки улучшаются. Через 2 . адреса s

0 весь блок 2 памяти записывается тесто

26 4 вая информация. Сигнал с выхода (n + 1) разряда счетчика 1 поступает на управляющий вход элемента ЗАПРЕТ и запре щает прохождение импульсов:записи на блок 2 памяти. Одновременно разрешается работа блока 3 сравнения. В следующем цикле происходит считывание ин формации из блока 2 памяти и сравнение с с записанной в режиме записи информацией. В случае несовпадения записанной и считываемой информации по каким-либо адресам появляется сигнал «Не равно" на выходе устройства. Количество у равляющнх шнн коммутаторов Р=00я т) р

:где m - количество информационйых шин.

Для 16-разрядных блоков памяти могут быть применены коммутаторы 16х1 с четырьмя управляющими входами.

Таким образом, введение в предлагае- . мое устройство элемента ЗАПРЕТ и коммутаторов позволяет существенно повысить достоверноазь контроля за счет выравнивания скорости смены информации в раз; ных разрядах проверяемого блока памяти.

104052 6

-Фмк

ВНИИПИ Заказ 6937/54 Тираж 594 Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4