Двенадцатиканальный распределитель уровней

Иллюстрации

Показать всеРеферат

ДВЕНАДЦАТИКА АЛЬНЫЙ РАСПРЕДЕЛИТЕЛЬ УРОВНЕЙ, содержащий четыре Р -триггера, С-входы которых соединены с тактовой шиной, три двух хрдовых элемента И-НЕ и один инвертор . отличающийся тем, что с целью его упрощения, в него введены двенадцать двухвходовых элементов и и три двухвходовых элемента ИЛИ, причем единичный выход первого В -триггера соединен с первыми входами первого, второго, третьего и четвертого элементов И, а нулевой выход - с вторым входом седьмого И первьлм входом восьмого, девятого и десятого элементов И, единичный выход второго D -триггера соединен с вторыми входами четвертого, пятого и шестого элементов И и первым входом седьмого элемента И, а нулевой,вы-. ход - с вторыми входами первого, де сятого , одиннадцатого и двенадцато ;ГО элементов и, единичный вь1ход третьего D -триггера соединен с вто рыми входами второго и. восьмого элементов И, а нулевой выход - с пер . выми входами пятого и одиннадцатого элементов И, единичный выход четвертого DI -триггера соединен с вторыми входами третьего и девятого элементов И, а нулевой - с первыми входами шестого и двенадцатого элементов И, D-ВХОД первого D -триггера соединен с выходом первого элемента ИЛИ, входы которого подключены к выходам второго и пятого элементов И соот-. ветственно, D -вход второго В.1 -триггера соединен с выходом второго элемента ИЛИ, входы которого подключены к выходам пятого и восьмого элеменсл тов И соответственно, JD -вход третьего D.-триггера соединен с выходом первого элемента И-НЕ, первый вход которого подключен к второму входу второго элемента И-НЕ и нулевому ВЫХОДУ четвертого D.J.-триггера, а второй вход соединен с выходом третьего элемента И-НЕ, первый вход Которого подключен череэ инвертор к выходу второго элемента И-НЕ, первый вход которого соединен с единичным выходом третьего D -триггера, а Од второй вход третьего элемента И-НЕ соединен сD-входом четвертого D триггер .а и выходом третьего элемен00 jTa ИЛИ входы которого подключены к выходам четвертого и десятого элементов И соответственно, выходы всех, (Элементов И подключены к выходной шине.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Э(51) Н 04 (, 13 14.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ .,К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3432603/18-21 (22) 29.04.82 (46) 07.09.83 . Бюл. Р 33 (72) Ю.М. Голембиовский и A.Ô., Резчиков (71) Саратовский ордена Трудового

Красного Знамени политехнический ин; .ститут (53) 621.382(088.8)

Г (56) l. Авторское свидетельство СССР

9 402152 . кл. Н 03 К 17/62, 1972.:

2.. Авторское свидетельство СССР по заявке 9 2896633/18-21, кл. Н 04 (13/14., 1980 (прототип) ° (54)(57) .ДВЕНАДЦАТИКА1ЬЛЬНЫЙ РАСПРЕ

ДЕЛИТЕЛЬ УРОВНЕЙ, содержащий четыре .3)<-триггера, С-входы которых соединены с тактовой шиной, три двухцходовых элемента И-НЕ и один инвертор,.. отличающийся тем, что с целью его упрощения, в него введены двенадцать двухвходовых элемен - тов И и три двухвходовых элемента -

ИЛИ, причем единичный выход первоГо

3 -триггера соединен с первыми вхо- . дами первого, второго, третьего и " четвертого элементов И, а нулевой выход — c вторым входом седьмого И первым входом восьмого, девятого и десятого элементов И, единичный выхОд второго D< -триггера соединен с вторыми входами четвертого, пятого и шестого элементов И и первым входом седьмого элг ента И, а нулевой,вы ход — с вторыми входами первого, де,сятого, одиннадцатого и двенадцато::

„„Su„„1040618 A го элементов И, единичный вЫход третьего 0< -триггера соединен с вторыми входами второго и. восьмого элементов И, а нулевой выход — с Первыми входами пятого и одиннадцатого элементов И, единичный выход четвертого D -триггера соединен с вторыми входами третьего и девятого элемен- тов И, а нулевой - c первыми входами шестого и двенадцатого элементов И,, Q-вход первого Э -триггера. соединен с выходом первого элемента ИЛИ, входы которого подключены к выходам второго и пятого элементов И соот-. ветственно, 7) -вход второго )3 -триггера соединен с выходом второго элемента ИЛИ, входы которого подкЛючены э

Р к выходам пятого и восьмого элементов И соответственно, Э -вход третьего )) -триггера соединен с выходом первого элемента И-НЕ, первый вход которого подключен к второму входу второго элемента И-НЕ и нулевому выходу четвертого D -триггера, а второй вход соединей с выходом третьего элемента И-НЕ, первый. вход Кото-. рого подключен череэ инвертор к выходу второго элемента И-НЕ, первый вход которого соединен с единичным выходом третьего D -триггера, а

1 второй вход третьего элемента И-НЕ соединен с 9 -входом четвертого D

C. триггера и выходом третьего элемен та ИЛИ, входы которого подключены к выходам четвертого и десятого .элементов И соответственно, выходы всех., элементов И подключены к выходной шине.

1040618

Изобретение относится к автомати.— ке, вычислительной технике, к промышленной электронике, в частности к управлению сложными .трехфазными тиристорными мостовыми преобразователями частоты.

Известен распределитель импульсов, позволяющий получать серию перекры- . вающихся импульсов с произвольным с,двигом (1 3.

Однако.при построении распредели- 10 теля сигналов, имеющих продолжительность Л/2 и сдвинутых один относи тельно другого на 7/б укаэанная схема оказывается слишком расточительной.по аппаратурным затратам. )5

Наиболее близким к предлагаемому является двенадцатиканальный распределитель уровней, содержащий четыре

D -триггера, С входы которых соединены с тактовой шиной, а единичные и нулевые выходы .подключены ко входам дешифратора, выходы которого соединены с выходными шинами. Закон переключения триггеров задается группой логических ячеек И-НЕ, сое25

: диняющих выходы триггеров с соответствующими входами (2 3.

К недостаткам известного устройства относится ограниченность функциональных возможностей. Так,. для, тех применений, где требуется продолжительность импульсов У/2 с сохранением сдвига между ними н 1/12 периода, необходимо к выходным шинам прототипа подключать дополнительную логическую схему, осуществляющую преобразование длительности импульсов с 7//6 до Ti/2.

Цель изобретения — упрощение устройства.

Укаэанная цель достигается тем, 40 что н двенадцатиканальном распреде-. лителе уровней, содержащем четыре

3 -триггера, С-входы которых соединены с тактовой шиной,. один иннертор и три двухнходовых элемента

И-НЕ, введены двенадцать двухнходовых элементов И и три двухвходовых элемента .ИЛИ, причем единичный выход первого )Э -триггера соединен с первыми входами первого, второго, третьего и четвертого элементов, И,а нулевой выход — с вторым входом седьмого и перным входом восьмого, девятого и десятого элементов И, единичный выход второго D<-триггера соединен со вторым входами четнерто- 55 го, пятого и шестого элементов И и первым входом седьмого элемента И, а нулевой выход — со вторыми входами первого, десятого, одиннадцатого и двенадцатого элементов И, единичнйй 60 выход третьего D - òðèããåðà соединен с вторыми входами второго и,восьмого элементов И, а нулевой выход — с первыми входами пятого и одиннадцатого элементов И, единичный выход четвертого ) -триггера соединен с вторыми

1 входами третьего и девятого элементов И, а нуленой - с первыми входами шестого и двенадцатого элементов

И, D -вход первого 3 -триггера соединен с выходом первого элемента ИЛИ, входы которого подключены к выходам второго н пятого элементов И соответственно, Э -вход второго 3) -триггера соединен с выходом второго .элемента ИЛИ, входы которого подключены к выходам. пятого и восьмого элементов И соответственно, D -вхоц третьего Р -триггера соединен с выходом первого элемента И-НЕ, первый вход которого подключен ко второму входу второго элемента И-НЕ и нулевому выходу четвертого D -триггера, а второй вход соединен с выходом третьего элемента И-НЕ, первый вход которого подключен через иннертор к выходу второго элемента И-НЕ, первый вход которого соединен с единичным выходом третьего D -триггера, а второй вход третьего. элемента И-НЕ соединен с D -входом четвертого

D -триггера и выходом третьего эле1 мента ИЛИ, входы, которого подключены к выходам четнертого и десятого элементов И соответственно, выходы всех элементон И подключены к выходной шине.

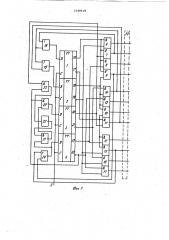

На фиг.l представлена функциональная схема двенадцатиканального распределителя уровней; на фиг.2 — .временные диаграммы его работы.

Двенадцатиканальный распределитель (фиг.1) содержит Р -триггеры

1, 2, 3 и 4, С-входы которых соединены с тактовой шиной 5, единичный выход D -триггера 1 соединен с первы1 ми входами элементов б, 7, 8 и 9 И, а нулевой выход подключен ко второму входу элемента 10 И и первыми входами элемейтон 11,12 и 13 И,единичйый выход D -триггера 2 соединен с вторыми входами элементов 9, 14 и 15 И и первым входом элемента

10 И, нулевой выход 3 -триггера 1 соединен с первыми входами элементов

ll — 13, нулевой выход D<-триггера 2 подключен ко вторым входам элементов

И б, 13, 16 и 17, единичный выход

)) -триггера 3 соединен с вторыми вхо1 дами элементов И 7 и 11, а нулевой выход подключен к первым входам элементов И 14 и 16, единичный выход

D -триггера 4 соединен с вторыми входами элементов И 8 и 12, а нулевой выход подключеи к первым входам элементов И 15 и 17, D -нход J) -триггера 1 соединен с выходом элемента

18 ИЛИ, входы которого подключены к выходам элементов И 7 и 14 соответственно, D - вход D -триггера2 соединен с выходом элемента 19 ИЛИ, входы которого подключены к выходам (элементов И 14 и 11 соответственно, 1040618

;р-вход 9 -триггера 3 соединен.-..с вмt ходом элемента 20 И-НЕ, входы которого подключены к выходу элемента

21 И-НЕ и нулевому выходу D -тригге- ра 4 соответственно, первый вход элемента 21 И-HE соединен через иивертор 22 с выходом элемента И-.НЕ 23 входы которого подключены к единичному выходу D -триггера 3 и нулево1 му выходу D<-триггера 4 соответственно, а второй вход элемента 21 И-НЕ . 10 соединен с D -входом D+-триггера 4 и выходом элемента 24 ЙЛИ, входы которого подключены к выходам. элементов 9 и 13 И соответственно., выходы элементов 6-17 И соединены соответственно с выходными шинами 25.

Распределитель .работает следующим образом,.

Пусть в начальный момент времени

Р -триггеры 1-4 находились в ну-. левом " состоянии, т.е. на их единичных. выходах 26 — 33 существовал уровень логического нуля.

Логические элементы И обеспечивают в этом .случае наличие сигналов в двенадцатом, первом и втором разрядах - выходных шинах 25. С исчезновением первого тактового импульса переключится в единичное состояние

D -триггер 4, так как íà его входе 30

l присутствовал сигнал логической единицы. При этом пропадает сигнал в двенадцатом разряде — выходной шине 25 и появляется в третьем разряде — выходной шине 25. Далее переключается в единиыное состояние

9 -триггер 3, что вызывает исчезновение сигнала в первом разряде шине 25 и появление в-четвертом разряде — шине 25 и т.д., Рассмотренный процесс продолжается так, что в каждый тактовый момент времени происходит переключение только одного D+-триггера 1,2,,3 и

4, а на.выходных шинах 25 формируются сигналы продолжительностью У/2 с сдвигом один относительно другого

5/6.

Надежность функционирования предлагаемого устройства такая же, как и прототипа, что обеспечивается самовосстановлением режима при сбоях.

Если в результате сбоя распределитель попадает в одно из неиспользуемых состояний, то вторым после сбоя тактовым сигналом восстанавливается его нормальное функционирование.

Таким образом, предлагаемый двенадцатиканальный распределитель уровней, обладая одинаковой с прототипом надежностью и фазовыми сдвигами между выходными сигналами, обеспечивает дополнительно получение большей, чем в прототипе, продолжительности выходных сигналов, равной

Л/2, что расширяет функциональные возможности распределителя.

Таким образом, предлагаемый двенадцатиканальный распределитель уровней обладает большими функциональными возможностями и меньшей сложностью по сравнению с прототипом.

1040618

10406 18

Составитель И. Парфенов

Редактор В. Пилипенко ТехредИ,Надь КорректорА. Тяско

Заказ 6949/59

Тираж -67.7 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4