Устройство поиска псевдослучайных последовательностей

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ .ПОСЛЕДО ВАТЕЛЬ НОСТЕЙ, СОДвржащее по ВХОДУ последовательно соединенные фильтр нижних частот, перемножитель и блок подтверждения сйнхро низма, последовательно соединенные блбк поэлементного приема, первый регистр сдвига и сумматор совпадений г к другим входам которого подключены . выходы второго регистра сдвига, последовательно соединенные генервтор тактовых импульсов и делитель частоты , выход которого подсоединен к первому входу переключателя и к первому входу блока, поэлементного приема, к второму входу которого подключен выход фильтра нижних частот, а также генератор псевдослучайных последовательностей (ПСП), внход которого подсоединен к первому входу второго регистра сдвига и второму входу перемножителя , и пороговый блок, о т личающееся т&ц, что, с целью повышения помехозащищенности Поиска , в него введены последовател| но соединенные адресный счетчик, счет-чик циклов, триггер обнаружения, одновибратор и дополнительный делитель частоты, последовательно соединенные блок вентилей, арифметический сумматор и оперативный запоминающий блок, а также элемент ИЛИ, выход которого подсоединен к второму входу переключателя , третий вход которого объединен с входом одновибратора, а выход подсоединен к второму входу второго регистра сдвига и второму входу дополнительного делителя частоты, выход которого подсоединен к входу генератора ПСП, при этом дополнитепь .ный выход генератора тактовых импульсов подсоединен к соответствующему входу оперативного запоминающего бло « ка, к Дополнительньм входам которого подключены соответствующие выходы адресного счетчика, первый вход коС торого объединен с вторым входом счетчика циклов и вторы входом триг гера сэбнаружения и подключен к выходу блока подтверждения синхронизма, второй вход которого подключен к выо ходу триггера обнаружения, третий вход которого подключен к выходу по4; рогового блока, вход которого объеND динен с выходами оперативного запоми шающего блока и входом блока вентилей , к другому входу которого подсое ;о о динен второй выход счетчика циклов, при этом выход генератора тактовых импульсов Подсоединен к второму входу адресного счетчика и первому вхо ПУ элемента ИЛИ, к второму входу которого подключен выход делителя частоты .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕаЪБЛИН (1Ю (1И

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

fl0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3346889/18-09 (22) 05.10.81 (46) 15 09.83. Вюл. Р 34 (72) Н.И.Коэленко, F).Â,Ëåâ÷åíêñ и А.P.Попов (53) 621.394.662.2(088.8 ) (56) 1. Авторское свидетельство СССР

Р 613512, кл. H 04 L 7/02, 1976.

2. Авторское свидетельство СССР

Р 347941, кл. Н 04 L 7/02, 1970 (прототип) .

I (54)(57) УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ .ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащее по входу последовательно соединенные фильтр нижних частот, переМножитель н блок подтверждения синхро- ниэма, последовательно соединенные блбк поэлементного приема, первый регистр сдвига и сумматор совпадений, . к другим входам которого подключений выходы второго регистра сдвига, последовательно соединенные генеретор тактовых импульсов и делитель частоты, выход которого подсоединен к первому входу переключателя и к первому входу блока поэлементного приема, к второму входу которого подключен выход фильтра нижних частот, а также генератор псевдослучайных последова- . тельностей (ПСп), выход которого подсоединен к первому входу второгорегистра сдвига и второму входу перемножителя, и пороговый блок, о т -: л и ч а ю щ е е с я тем, что, с .целью повыщения помехоэащйщенности приска, в него введены последовательно соединенные адресный счетчик, счет-.$151) Н 04 Ь 7 02 /. Н 04 L .7/04 чик циклов, триггер обнаружения, одновибратор и дополнительный делитель частоты, последовательно соединенные блок вентилей, арифметический сумматор и оперативный эапоминакиций блок, а также элемент ИЛИ, выход которого подсоединен к второму входу .переключателя, третий вход которого объединен с входом одновибратора, а выход подсоединен к второму входу второго регистра сдвига и второму входу дополнительного делителя частоты, выход которого подсоединен к входу генератора ПСП, при этом дополнитель.ный выход генератора тактовых импульcos подсоединен к соответствующему входу оперативного запоминающего бло-I ка, к дополнительным входам которого подключены соответствующие выходы адресного счетчика, первый вход ко.торого объединен с вторым входом счетчика циклов и вторым входом триггера обнаружения и подключен к выхо- Я ду блока подтверждения синхроннэма, второй вход которого подключен к выходу триггера обнаружения, третий вход которого подключен к выходу порогового блока, вход которого объединен с выходами оперативного эапомн

pataqего блока и входом блока вентилей, к другому входу которого подсоединен второй выход счетчика циклов, при этом выход генератора тактовых импульсов подсоединен к второму входу адресного счетчика и первому входу элемента ИЛИ, к второму входу которого подключен выход делителя частоты.

1042199

Изобретение относится к радиотехнике и может использоваться в системах связи с шумоподобными фазоманипулированными сигналами.

Известно устройcTBo для синхронизации шумонодобных сигналов, содержащее объединенные по одному из Вхо- дов два перемножитвля, к другим входам которых подключены соответствующие выходы генератора опорног напряжения, а также сумматор, два интег- !О ратора, два преобразователя цифрааналог, два преобразователя аналогцифра, модулятор сигналов, коммутатор, пороговый блок, два регистра сдвига, Й накопителей, И +2 дополни- 15 тельных сумматоров, при этом выход каждого перемножителя через последовательно соединенные соответствующие интегратор, преобразователь аналогцифра, регистр сдвига и один из дополнительных сумматоров, к другому входу которого подсоединен вход регистра сдвига, подключен к одному из входов модуляторов сигналов, выходы которого через другие N дополнительных сумматоров подключены к другому входу соответствукщих дополнительных сумматоров и к соответствующим входам коммутатора, каждый выход которого через преобразователь цифра-аналог подключен к входу соответствующего квадратора, кроме того, выход сумматора подключен к входу порогового блока (1) .

Данное устройство обладает высокой помехозащищенностью, но относительно большим временем поиска сигналов.

Наиболее близким к изобретению является устройство синхронизации с п-последовательностью, содержащее последовательно соединенные фильтр ниж-40 них частот, перемножитель, блок-подтверждения синхронизма, переключатель генератор псевдослучайных последовательностей (ПСП), первый регистр сдвига, сумматор совпадений и порого-45 вый блок, выход которого подключен к второму входу блока подтверждения синхронизма, последовательно соединенные генератор тактовой частоты и делитель частоты, выход которого под- 50 ключен к второму входу переключателя, к третьему входу которого подсоединен выход генератора тактовых импульсов, при этом выход делителя частоты через последовательно соединенные блок поэлементного приема и второй регистр сдвига подсоединен к другим входам сумматора совпадений, а выход генератора ПСП подключен к второму входу перемножителя (2) .

Это устройство синхронизации с д -последовательностью обладает небольшим временем поиска, однако помехозащищенность его сравнительно низк

Цель изобретения — повышение поме- хоэащищенности поиска. 65

Для достижения цели в устройство поиска псевдослучайных последовательностей, содержащее по входу последовательно соединенные фильтр нижних частот, перемножитель и блок подтверждения синхроннзма, последовательно соединенные блок поэлементного приема, первый регистр сдвига и сумматор совпадений, к другим входам которого подключены выходы второго регистра сдвига, последовательно соединенные генератор тактовых импульсов и делитель частоты, выход которого подсоединен к первому входу переключателя и к первому входу блока поэлементного приема, к второму входу которого подключен выход,,фильтра нижних частот, а также генератор ПСП, выход которого подсоединен к первому входу второго регистра сдвига и второму входу перемножителя, н пороговый блок, введены последовательно соединенные адресный счетчик, счетчик циклов, триггер обнаружения, одновибра-. тор и дополнительный делитель часто ты, последовательно соединенные блок вентилей, арифметический сумматор н оперативный запоминающий блок, а также элемент ИЛИ, выход которого подсоединен к второму входу переключателя, третий вход которого объединен с входом одновибратора, а выход подсоединен к второму входу второго регистра сдвига и второму входу дополнительного делителя частоты, выход которого подсоединен к входу генератора ПСП, при этом дополнительный выход генератора тактовых импульсов подсоединен к соответствующему входу оперативного запоминающего блока, к дополнитеЛЬным входам которого подключены

r соответствующие выходы адресного счетчика, первый вход которого объединен с вторым. входом счетчика циклов и вторим входом триггера обнаружения и подключен к выходу блока подтверждения синхронизма, второй вход которого подключен к выходу триггера обнаружения, третий вход которого подключен к выходу порогового блока, вход которого объединен с выходами оперативного запоминакицего блока и входом блока вентилей, к другому входу которого подсоединен второй выход счетчика циклов, при этом выход генератора тактовых импульсов подсоединен к второму входу адресного счетчика и первому входу элемента ИЛИ, к второму входу которого подключен выход делителя частоты.

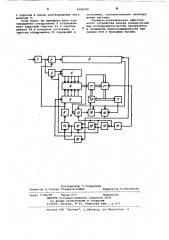

На чертеже представлена структурно-электрическая схема устройства поиска псевдослучайных последовательностей.

Устройство поиска псевдослучайных последовательностей содержит фильтр нижних частот (ФНЧ) 1, перемножитель

2, блок поэлементного приема 3, ре1042199 гистры сдвига 4 и 5, сумматор совпадений 6, пороговый блок 7, генератор

ПСП 8, блок подтверждения синхронизма 9, триггер обнаружения 10, генератор тактовых импульсов 11, делитель частоты 12, переключатель 13, дополнительный делитель частоты 14, адресный счетчик 15, одновибратор 16, арифметический сумматор 17, блок вентилей 18, счетчик циклов 19, элемент ИЛИ 20 и оперативный запоминаю- 10 щий блок 21.

Предлагаемое устройство работает следующим образом.

Входная псевдослучайная последовательность после фильтрации в ФНЧ.1 15 поступает на перемножитель 2 и блок поэлементного приема 3, в котором > производится оценка символов принимаемой последовательности либо на.интервале длительности одного символа, 2О либо на интервале в Р раз меньшей длительности, где Р— целое число, в зависимости от требуемой помехозащи- щенности и точности определения за- держки сигнала. Полученные значенйя продвигаются в регистре сдвига 4 в темпе их формирования, с выходов раз рядов которого поступают на входы: . сумматора совпадений 6.

В регистр сдвига 5 поступают от-. счеты местной последовательности, формируемой генератором ПСП 8 (но

P отсчетов на элементе) . Частота: .

Формирования последовательности генератором ПСП 8 в режиме поиска сигнала равна (K+1)1щ, где р — тактовая: частота входной последовательности.

Тактовая частота регистра сдвига. 5 соответственно равна Р (К+1) f>.

Формирование этих частот осуществляется следующим образом. 40

Генератор тактовых импульсов. 11. вырабатывает частоту РК1,„, которая поступает на один вход элемента ИЛИ 20 непосредственно и на второй через делитель частоты 12 в К раз., 45

Элемент ИЛИ 20 осуцествляет сложение частот. Полученный сигнал час-,,тоты Р K+1fù поступает через открытый переключатель 13 на регистр сдви га 5 и делитель частоты 14 в Р раз, который формирует сигнал тактовой . частоты (К 1) 1, управляющий генератором ПСП 8.

При каждом сдвиге выборок в регистре сдвига 4 пооисходит сдвиг вы- борок в регистре сдвига 5, а между ними еще РК сдвигов в регистре Ьдвига 5, при каждом из которых осуществляется подсчет числа совпадакщйх разрядов регистров сдвига 4 и 5 в. сумматоре совпадений 6. Результат . 6О подсчета, выраженный в Двоичном коде, поступает на арифметический сумматор

17, в котором суммируется с двоичным числом, поступающим с блока вентилей 18. 65

В исходном состоянии счетчик циклов 19 блокирует прохождение сигналов через блок вентилей 18, и числа, поступающие с сумматора совпадений 6 непосредственно через арифметический сумматор 17, подаются на оперативный запоминающий блок 21, в котором запоминаются в ячейках памятки с номером, определяемым кодом адресного счетчика

15. Частота изменения кода совпадает с относительной частотой продвижения выборок в регистрах сдвига 4 и 5 и равна PK f, а коэффициент пересчета адресного счетчика 15 равен количеству отсчетов входного сигнала на одном периоде ПСП, т.е. РМ, где число элементов псевдослучайной последовательности °

Таким образом, в первом цикле осуществляется запись значений взаимной корреляции сегментов входной и опорной .последовательностей соответствующих их различным временным задержкам. После записи всех НР значений адресный счетчик 15 выдает импульс переноса, который меняет состояние счетчйка циклов 19 и он открывает вентили записи в блоке вентилей 18 °

При этом числа, записанные в оперативный запоминающий блок 21, поступают на арифметический сумматор 17, суммируются с приходящими и вновь записываются по тому же адресу, и т.д.

Счетчик циклов 19 задает общую длину сегмента последовательности, по которому производится вычисление функции взаимной корреляции.

Так, например, если регистры сдвига 4 и 5 содержат Pi. разрядов, а коэффициент пересчета счетчика циклов 19 равен N, то длина сегмента равна Ь,М

В последнем Ч -м состоянии счетчик циклов 19 выдает на триггер обнаружения 10 сигнал, разрешающий прием информации. Значения функций взаимной корреляции, поступающие с выхода оперативного запоминающзго блока

21 на пороговый блок 7, сравниваются с порогом, в случае превышения которого выдается импульс, переворачивающий триггер обнаружения 10 в состояние; соответствующее обнаружению сигнала. При этом одновибратор 16 вырабатывает короткий импульс, устанавливающий делитель частоты 14 в исходное состояние, а переключатель 13 подключает к делителю частоты 14 сигнал частоты Pf„п . Делитель частоты

14 вырабатывает тактовую частоту f.ðä генератора ПСП 8, Фаза которой соответствует найденному значению.

Формируемая в темпе принимаемой псевдослучайная последовательность генератора ПСН 8 демодулирует входной сигнал в перемножителе 2, сигнал которого интегрируется и сравнивается

1042199

Составитель Т. Лоддубняк

Редактор А.Гулько Техред И. ГайдУ Корректор, Ю,Макаренко

Заказ 7148/58 Тираж 677 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ж-35, Раушская наб., д.4/5 филиал ППП "Патент", г.ужгород, ул.Проектная, 4 с порогом в блоке подтверждения синхронизма 9.

Если порог не превышен, блок подтверждения синхронизма 9 устанавливает адресный счетчик 15 и счетчик циклов 19 в исходное состояние, а триггер обнаружения 10 переводит в состояние, соответствующее необнару кению сигнала.

Технико-зкономическая эффективность устройства поиска псевдослучайных последовательностей заключается в повышении помехозащищенности при приеме ПСП с большими базамн.