Устройство синхронизации по циклам

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ, содержащее последовательно соединенные приемник двоичных сигналов, регистр сдвига, дешифратор, блок коммутации, к другим входам которого подключен другой выход приемника двоичных сигналов через накопитель , и счетчик, выход которого подключен непосредственно и через последовательно соединенные ключ и памяти к входам блока сравйения, выход которого подключен к первому входу решающего блока, о Y л и ч а ю ш е е с я тем, что, с целью повышения помехоустойчивости, в него введены дополнительный блок коммутации и дополнительный счетчик, при этом первый и второй входы ремаюшего блока объединены с соответствуюними входами дополнительного блока коммутации , к двур другим входам которого подключены соответствуюшие ъыхазщ р ешаюшего блока, а выход дополнитёйЬ ного блока коммутации подключен к другому входу ключа и к первому входу дополнительного счетчика, к второму входу которого подключен соответствующий выход приемника двоичных сигналов, а выход дополнительного счетчиТ а подключен к второму входу решающего блока. 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что решаюиий ,блок содержит последовательно соединенные элемент НЕ, вход которого объединен с первыми входами первого и второго элементов И, третий элемент И, другой вход которого объединен с вторым входом первого элемента И, первый.триггер, элемент ИЛИ и второй триггер, к другому вхо (П ду которого подключен выход первого элемента И, первый выход второго триггера через второй элемент и подключён к первому входу первого счетчика , а через последовательно соединенные четвертый элемент И, к другому входу которого подключен выход третьего элемента И, и второй счето чик - к соответствующим входам первого счетчика, первого триггера и эле4 мента ИЛИt причем первый и второй to Nd входы первого элемента И являются входами, а первый и втррой выходы -JBToporo триггера и выход первого счето чика являются выходами рёшакятегб блока.

(199 (В

8(Д) Н 04 (7/08 ф (1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ: ":

N kB TOPCNOMV CÂÈ ÅÒÅË Ñ ÂÓ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ГЮ ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

1 (21) 3405466/18-09 (22) 03.03.82 (46) 15.09.83. Бюл. Р 34 (72) И.В. Тарасов (53) 621.394.662(088.8) (56) 1. Авторское свидетельство СССР

9 543183, кл. Н 04 (7/ОВ, 1978, 2. Авторское свндетелЬство СССР

В 657643, кл. Н 04 L 7/08, 1977 (прототип). (54)(57) 1 ° УСТРОЙСТВО СИНХРОНИЗАЦИИ

ПО ЦИКЛАМ, содержашее последователь- но соединенные приемник двоичных сигналов, регистр сдвига, дешифратор, блок коммутации, к другим входам которого подключен другой выход приемника двоичных сигналов через накопитель, и счетчик, выход которого под-. ключен непосредственно и через последовательно соединенные ключ и блок памяти к входам блока сравнения, выход которого подключен к первому входу решаюшего блока, о г л и ч аю ш е е с я тем, что, с целью повышения помехоустойчивости, в него введены дополнительный блок коммутации и дополнительный счетчик, при этом первый и второй входы решаюшего блока рбъединены с соответствуюшими входами дополнительного блока комму-. тации, к двум другим входам которого подключены соответствукхяие вьв(с(ды решаюшего блока, а выход дополнитайьного блока коммутации подключен к другому входу ключа и к первому входу дополнительного счетчика, к второму входу которого подключен соответстзуюший выход приемника двоичных сигналов, а выход дополнительного . счетчика подключен к второму входу решаюшего блока.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что решающий .бпок содержит последовательно соединенные элемент НЕ, вход которого объединен с первыми входами первого и второго элементов И, третий элемент И, другой вход которого объединен с вторым входом первого элемента И, первый. триггер, элемент

ИЛИ и второй триггер, к другому входу которого подключен выход первого элемента И, первый выход второго триггера через второй элемент И подключен к первому входу первого счетчика, а через последовательно соединенные четвертый элемент И, к другому входу которого подключен выход третьего элемента И, и второй счетчик - к соответствукэ им входам перво. го счетчика, первого триггера и элемента ИЛИ причем первый и второй входы первого элемента И являются .входами, а первый и второй выходи

-, второго триггера v выход первого счетчика являются выходами решантего блока.

1042201

Изобретение относится к технике электросвязи и может использоваться при цикловой синхронизации в систе мах передачи дискретной информации, используюших маркерные синхрослова (синхрокод). 5

Известно уе-ройство приема сигналов сиНхронного запуска, содержашее последовательно соединенные приемник с блоком обработки сигналов и накопитель, а также селектор синхросигна- 10 лов, к одному из входов которого подключен счетчик, регистр сдвига, блок коммутации и блок управления, при этом выход блока обработки сигнала подключен непосредственно и 15 через регистр сдвига к соответствуюшим входам блока управления, выходы которого подключены к соответствуюшим входам счетчика, а выходы раз. рядов регистра сдвига подключены к управля ацим входам блока коммутации, включенного между выходами накопителя и входами селектора синхросигналов (Ц, Однако данное устройство не обладает достаточной помехоустойчивостью,,так как имеет фиксированный порог принятия решении .о выделении синхрбслова, вследствие чего при изменении соотношения сигнал/шум происходит уменьшение вероятности правильного 30 обнаружения синхрокода, а следовательно, снижение помехоустойчивости устройства.

Наиболее близким к предлагаемому является устройство синхронизации 35 по циклам, содержашее приемник двоичных сигналов, сигнальный выход которого через накопитель подключен к одному из входов блока коммутации, а также дешифратор, регистр сдвига, 40 формирователь отношений сигнал/шум и решаюший блок, к входам которого подключены два канала обработки сигнала, каждый из которых состоит из последовательно соединенных ключа, блока памяти и блока сравнения, причем к входу одного канала обработки сигнала подключен выход счетчика, а к входу другого канала обработки сигнала — соответствуюшие выходы накопителя через формирова- 5

50 тель отношений сигнал/шум, выход решаюшего блока подключен к управлявшим входам ключей обоих каналов обработки сигнала, а информационный выход приемника сигналов через после-55 довательно соединенные регистр сдвига и дешифратор подключен к другим в ходам блока коммутации, выход кото2 рого подключен к выходу счетчика () .

Это устройство также не обладает достаточной помехоустойчивостью, так как в нем не осушествляется проверка правильности обнаружения максимума корреляционной Функции, который должен соответствовать положению истин, ного синхрослова.

Цель изобретения - повыаение помехоустойчивости.

Для достижения цели в устройство синхронизации по циклам, содержашее последовательно соединенные приемник двоичных сигналов, регистр сдвига, дешифратор, блок коммутации, к дру гим входам которого подключен другой выход приемника двоичных сигналов

,через накопитель, и счетчик, выход которого подключен непосредственно и через последовательно соединенные ключи и блок памяти к входам блока сравнения, выход которого подключен к первому входу решаюшего блока, введены дополнительный блок коммутации и дополнительный счетчик, при этом первый и второй входы решаюшего блока объединены с соответствуюшими входами дополнительного блока коммутации, к двум другим входам которого подключены соответственно выходы решаюшего блока, а выход дополнительного блока коммутации подключен к другому входу ключа и к первому входу дополнительного счетчика, к второму входу которого подключен соответствуюший выход приемника двоичных сигналов, а выход дополнительного счетчика подключен к второму входу решающего блока.

Решающий блок содержит последовательно соединенные элемент НЕ, вход которого объединен с первыми. входами первого и второго элементов И, третий элемент И, другой вход которого объединен с вторым входом первого элемента И, первый триггер, элемент

ИЛИ и второй триггер, к другому входу которого подКлючен выход первого элемента И, первый выход второго триггера через второй второй элемент

И подключен к первому входу первого счетчика, а через последовательно соединенйые четвертый элемент И, к другому входу которого подключен выход третьего элемента И, и второй счетчик — к соответствуюшим входам первого счетчика, первого триггера и элемента ИЛИ, причем первый и второй входы первого элемента И являются входами, а первый и второй выходы второго триггера и выход первого счетчика являются выходами решаюшего блока.

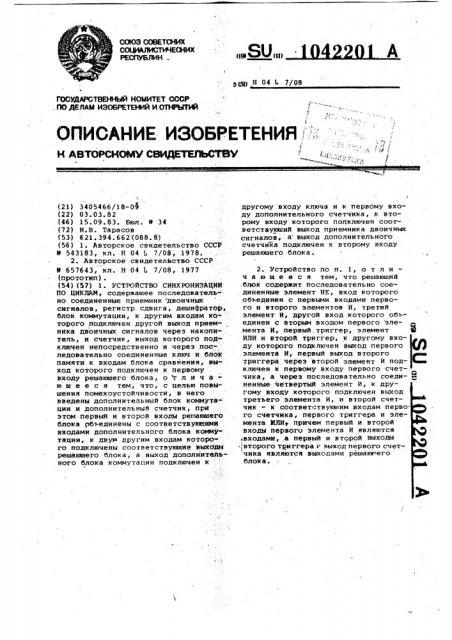

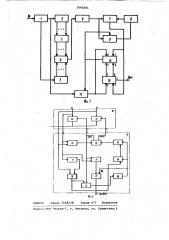

На фиг. 1 изображена структурная электрическая схема устройства синхронизации но циклам; на фиг. 2 — струк- .— турные электрические схемы блока коммутации и решающего блока.

Устройство синхронизации содержит приемник 1 двоичных сигналов, вход которого является входом устройства, регистр 2 сдвига, дешифратор 3, блок

4 коммутации, накопитель 5, счетчик б, блок 7 сравнения, блок 8 памяти, 1042201 ключ 9, дополнительный блок 10 коммутации, выход которого соединен с управляющим входом ключа 9, дополнительный счетчик 11, вход сброса которого подключен к выходу блока 10 коммутации, решающий блок 12, выход которОго является выходом устройства.

Блок 10 коммутации содержит ключи

13 и 14. Решающий блок 12 содержит элементы И 15 и 16, элемент HE 17, триггер 18 с раздельными входами, 10 элемент ИЛИ 19, триггер 20 с раздель-. ными входами элемент И 21, счетчик

22, элемент И 23 и счетчик 24.

Устройство работает следующим образом. 15

Принимаемая кодовая последовательность знаков поступает из приемника

1 двоичных сигналов в регистр 2 сдвига и затем анализируется в дешифраторе 3. При этом на выходе дешифратора 3 появляются единичные .. сигналы при совпадении соответствую щих знаков со структурой синхрослова.

Одновременно сигналы регистрации принятых знаков через накопитель 5 25 поступают в блок 4 коммутации, в ко-. тором вырабатываются сигналы, соот-. ветствующие числу совпадающих и нЕсовпадающих знаков.

Счетчик б, осуществляя подсчет. . 30 совпадающих и несовпадающих. знаков, производит вычисление корреляционной функции для каждого сдвига информа- . ции. Выходной сигнал счетчика б сравнивается в блоке 7 с пороговым: 35 зиачением, хранияющимся в блоке 8 памяти и поступающим в этот блок с выхода счетчика б через ключ 9, который управляется сигналом с выхода блока 10 коммутации. Этот сигнал од- 4О новремвнно поступает на вход сброса .счетчика 11, осуществлявшего подсчет знаков, поступающих с информационного выхода приемника 1 двоичных сиг. налов. Сигнал с выхода блока 7 сравнения следует на соответствующие входы блока 10 коммутации и решающе- го блока 1.2.

В режиме поиска синхрокода при поступлении истинного синхрокода к«>ррелянионная функция, определяемая счетчиком б, имеет максимальное значение. В этом случае величина вы- хбдного сигнала счетчика 6 больше, чем при ранее поступивших сигналах, вследствие чего на выходе блока 7 55 сравнения появляется сигнал„, который следует на информационный вход клю--. ча 13 блока IA коммутации. Одновре- менно этот сигнал подается на,соответствующие входы элементов И 15 14. 60

16. В режим поиска синхрокода иа,:: выходе счетчика ll сигнал отсутствует, поэтому элемент И 15 закрыт, а элемент И 16 открыт, в результате чего триггер 18 устанавливается в состояние, при котором его выходной сигнал, поступая через элемент ИЛИ 19, переводит триггер 20 в обратное состояние. Сигнал с выхода триггера 20 открывает ключ 13, через который сигнал с выхода блока 7 сравнения подается на управляющий вход ключа 9 и на вход сброса счетчика 11 ° . В блок

8 памяти загисывается текущее значение корреляционной функции, подсчитан. ной счетчиком б.

Если в течение следующего кадра сигнал на выходе счетчика 6 меньше записанного в блоке 8 памяти, то ,через К символов, поступивших на

° вход счетчика 11, на его выходе появляется сигнал, который открывает элемент И 15 и закрывает элемент.

И 16. При .этом выходной сигнал элемент ! та V 15 устанавливает триггер 20 в обратное состояние, вследствне чего открывается ключ 14 блока 10 коммутации, и устройство переходит в режим проверки.

В режиме проверки сигнал со счетчика 11 через ключ 14 проходит на вход сброса счетчика 11 и на управляющий вход ключа 9. При этом в блок

8 памяти заносится очередное значение выходного сигнала счетчика 6.

Если в течение следующего кадра нет превышения порога (успешное решение), то сигнал с выхода .счетчика .11 поступает через элемент И 21 в счетчик

22, подсчитывающий количество успешных решений. После подсчета определенного количества успешных решений на выход решающего блока 12 поступает сигнал, соответствующий окончательному решению о выделении синхрокода (захват) .

Если в режиме проверки в течение кадра происходит превышение порога в блоке 7 сравнения, то сигнал с его выхода через элементы И 16 и 23 поступает в счетчик 24« подсчитывающий количество..ошибочных решений.

После подсчета определенного числа ошибочных решений выходной сигнал счетчика 24 через элемент ИЛИ 19 устанавливает триггер 20 в состояние, соответствующее режиму поиска, а счетчик 22 — в исходное состояние.

Таким образом, введение в устрой- . ство дополнительного блока 10 коммутации, дополнительного счетчика 11 и указанная реализация решающего блока 12 позволяют осуществить йраверку правильности обнаружения синхрокода. При этом решение о выделении,. синхрокода принимается при получении заранее установленного числа успешных решений, в результате чего по-, вышается вероятность Правильного при- . нятия решения, а следовательно, поМ« хоустойчивости устройства.

1О4аЛО1 вййиПИ Закаэ 7148/5S Тира к 677 Подписное

Филиал ППП "Патент", r. Уагород, ул. Проектная„,4