Одноразрядный сумматор

Иллюстрации

Показать всеРеферат

ОДНОРАЗРЙДНЫЙ СУММАТОР по авт. св. 907543, о т л и ч а ющ и и с я тем, что, с целью расширения функциональных возможностей за счет осуществления операции вычитания , он содержит третий, четвертый, пятый и шестой п-р-п транзисторы, а также седьмой р-п-р транзистор и пятый многоколлекторный п-р-п транзистор , причем первый коллектор пятого многоколлекторного п-р-п транзистора соединен с шиной разности одноразрядного сумматора, второй коллектор соединен с эмиттером седьмого р-п-р транзистора, а база пятого .многоколлекторного п-р-п транзистора соединена с вторыми коллекторами первого и второго п-р-п транзисторов и соответствующим коллектором многоколлекторного р-п-р транзистора , база третьего транзистора соединена с рторым коллектором пятого р-п-р ,транзистора, а коллектор соединён с базой четвертого п-р-п транзистора и соответствующим коллектором многоколлекторного транзистора, коллектор четвертого п-р-п транзистора соединен с коллектором пятого п-р-п транзистора и под:(лючен к шине заема одноразрядного сумматора, база пятого п-р-п транзистора соединена с ррответству-i ющим коллектором многоколлекторного | р-п-р транзистора и коллектором шестого п-р-п транзистора, база которого соединена с вторым коллектором Шестого и коллектором седьмого р-п-р транзисторов, база седьмого р-п-р транзистора, .эмиттеры всех транзисторов и эмиттер пятого многоО 4ia коллекторного п-р-п транзистора подключены к шине нулевого потенциала.. . : Э: «

СОЮЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) 3(51) 06 P 7 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ : н автонснамм свиц твъствм: г

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПЮ ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТКРЫТИЙ! (61) 907543 . (21) 3460472/18-24 (22) 29.03.82 (46) 23.09 ° 83. Вюл. М 35 (72) Л.К. Самойлов, Ю.И. Рогозов, A.Â.Ãëîáà и А.В. Черных (71) Таганрогский радиотехнический институт им. В.Д. Калмыкова (53) 681.325.5(088.8) 1 (56) 1. Авторское свидетельство СССР

9 907543, кл. G 06 Р 7/50, 1980 (прототип). (54)(57) ОДНОРАЗРНДНЫЙ СУИКАТОР по авт. св. В 907543, о т л и ч а юшийся тем, что, с целью расширения функциональных возможностей эа счет осуществления вперации вычитания, он содержит третий, четвертый, пятый и шестой и-р-и транзисторы, а также седьмой р-и-р транзистор и пятый многоколлекторный и-р-и транзистор, причем первый коллектор пятого многоколлекторного и-р-и транзистора соединен с шиной разности одноразрядного сумматора, второй коллектор соединен с эмиттером седьмого р-и-р транзистора, а база пятого ,многоколлекторного и-р-и. транзисто- " ра соединена с вторыми коллекторами первого и второго и-р-и транзисторов и соответствующим коллектором многоколлекторного р-п-р транзистора, база третьего и-р-и транзистора соединена с вторым коллектором пятого р-п-р,транзистора, а коллектор соединен с базой четвертого и-р-и транзистора н соответствующим коллектором многоколлекторного р-и-р транзистора, коллектор четвертого и-р-и транзистора соединен с коллектором пятого и-р-и транзистора и под1слючен к шине заема одноразрядного сумматора, база пятого и-р-и Я транзистора соединена с соответствующим коллектором многоколлекторного р-и-р транзистора и коллектором шестого и-р-и. транзистора, база которого соединена с вторым коллектором шестого и коллектором седьмого р-и-р ©

Ф транзисторов, база седьмого р-и-р транзистора, .эмиттеры всех и-р-и транзисторов и эмиттер пятого многоколлекторного и-р-и транзистора подключены к шине нулевого потенциала., 10436 41

5О

Изобретение относится к вычисли- тельной технике и может быть исполь зовано при построении интегральных схем обработки информации.

По основному авт. св. 9 907543 известен одноразрядный сумматор, содержащий и-р-п и р-и-р транзисторы, многоколлекторные и-р-п транзисторы и многоколлекторный p-n-p транзистор, эмиттер которого соединен с шиной питания сумматора, а 1О коллекторы, соответственно, с эмиттерами всех р-и-р транзисторов и базами первого, второго и третьего, многоколлекторных и-р-и транзисторов, коллекторы, первого и второго 15 р-и-р транзисторов соединены с базой первого и-р-п транзистора, а кол-, лекторы третьего и четвертого р-и-р транзисторов соединены с базой четвертого многоколлекторного и-р-п транзисторов, базы всех р-и-р транзисторов, эмиттер первого п-р-и .транзисторов, база многоколлекторного р-и-р транзистора и эмиттеры всех многоколлекторных п-р-и транзисторон соединены с шиной нулевого потенциала сумматора, последний содержит также второй n-p-n транзистор, база которого соединена с одним из коллекторов многоколлекторного р-п-р транзистора и первым коллектором первого, второго и третьего многоколлекторных р-и-р транзисторов, вторые коллекторы этих транзисторов соединены соответственно с эмиттерами первого, второго и пятого р-и-р транзисторов, 35 коллектор пятого р-и-р транзистора соединен с коллектором второго р-и-р транзистора, коллектор четвертого р-и-р транзистора соединен с коллектором шестого р-п р транзистора, 40 эмиттер которого соединен с третьими коллекторами первого и второго многоколлекторных и-р-п транзисторов, эмиттер четвертого р-и-р транзистора соединен с тРетьим коллекто- 45 ром третьего и четвертым коллектором второго многоколлекторного и-р-и транзисторон, четвертые коллекторы первого и третьего многоколлекторных и-р-п транзисторов соединены с эмиттером третьего р-п-р транзистора, коллекторы первого и второго и-р-п транэисторон соединены с выходом суммы м сумматора, первый коллектор четвертого многоколлекторного и-р-п транзистора соединен с базой 55 первого и-р-п транзистора, второй коллектор четвертого многоколлекторного и-р-и транзистора соединен с выходом переноса сумматора, а входами сумматора являются базы перво- ц1 го, второго и третьего многоколлекторных п р-и транзисторон (1) .

Недостатком известного устройства является ограничение функ11иональных возможностей, что выража- 65 ется н невозможности осуществления операции вычитания.

Цель изобретения — расширение функциональных воэможностей одноразрядного сумматора за счет осуществления операции вычитания.

Укаэанная цель достигается тем, что одноразрядный сумматор содержит третий, четвертый, пятый и шестой и-р-и транзисторы, а также седьмой р-и-р транзистор и пятый многоколлекторный и-р-и транзистор, причем первый коллектор пятого многоколлекторного и-р-и транзистора соединен с шиной разности одноразрядного сумматора, второй коллектор соединен с ,эмиттером седьмого р-и-р транзистора, а база пятого многоколлекторного и-р-и транзистора соединена с вторыми коллекторами первого и второго п-р-и транзисторов и соответствующим коллектором многоколлекторного р-и-р транзистора, база третьего п-р-п транзистора соединена с нторым коллектором пятого р-и-р транзистора, а коллектор соединен с базой четвертого и-р-и транзистора и соответствующим коллектором многоколлекторного р-и-р транзистора, коллектор четвертого и-р-и транзистора соединен с коллектором пятого и-р-и транзистора и подключен к шине заема одноразрядного сумматора, база пятого п-р-и транзистора соединена с соответствующим коллектором многоколлекторного р-и-р транзистора и коллектором шестого п-р-и транзистора, база которого соединена с вторым коллектором шестого и коллектором седьмого р-и-р транзисторов, база седьмого р-и-р транзисторов, эмиттеры всех и-р-и транзисторов и эмиттер пятого многоколлекторного и-р-и транзистора подключены к шине нулевого потенциала.

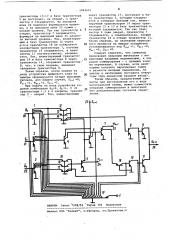

На чертеже представлена принципиальная электрическая схема одноразрядного сумматора.

Одноразрядный сумматор содержит и-р-п транзисторы 1-11, р-и-р транзисторы 12-18 и многоколлекторный инжектирующий транзистор 19. Входами сумматора являются шины 20-22, вы. ходом суммы — шина 23, переноса — шина 24, разности — шина 25 и эаема— шина 26.

Сумматор работает следующим образом.

Предположим, что на входе устройства имеем кодовую комбинацию а 1, Ь =О, U<=1. Транзисторы 1 и 3 открыты, а транзистор 2 закрыт, следовательно, ток, инжектируемый в эмиттеры транзисторон 12 и 13, отбирается соответственно коллекторами транзисторов 1 и 3, а через транзистор 14 ток поступает в базу транзистора 6. Учитыная, что ток через

1043641!

ВНИИПИ Заказ 7338/51 Тираж 706 Подписное

Филиал ППП "Патент", r.Óæãîðîä, ул,Проектная,4 транзисторы 15-17 в базу транзистора

5 не поступает, он открыт, а транзистор 6 открывается. На выходной шине 24 переноса формируется единица, а на выходной шине 23 суммы— низкий уровень. Так как транзистор 6 открыт, транзистор 7 закрывается, формируя на выходной шине 25 разности высокий уровень. Ток, инжектируемый в базу транзистора 10 через р-и-р транзистор 18 не отбирается коллектором транзистора 7, поэтому. транзистор 10 открывается, а транзистор. 11 соответственно, закрывается. Ток, инжектируемый транзистором 19 в базу транзистора 8 через транзистор 14, открывает транзистор .

8, что, в свою очередь, вызывает запирание транзистора 9.

Таким образом, после подачи на вход устройства цифрового кода на выходе сформируется четыре выходных .сигнала, для нашего случая, S + 0 .Рк (1 р И ((1 UK — 1

При подаче на вход устройства кодовой комбинации ак=0, b =1, V =0 транзисторы 1,3 и 4 закрыты, транзистор 2 — открыт. Ток, инжектируемый

< через транзистор 17, поступает в базу транзистора 5, который открывается и отбирает базовый ток, инжектируемый транзистором 19 через транзисторы 12 и 13 в базу транзистора 6, 5 который закрывается. Так как транзистор 4 тоже закрыт, транзистор 7 открывается, а следовательно, закрыт транзистор 10 и открыт транзистор 11.

Таким образом., по окончании переходного процесса на выходе устройства устанавливается код S +< =1, Рк+ =О, W„,,„=0, и„„=о.

Следует отметить, что сумматор производит операцию вычитания с ин 5 версными входными переменными, а опе. рацию суммирования - с прямыми кодами переменных. В случае, если необходимо получить параллельно сумму и разность входных переменных, на выходе и необходимо поставить инверторы (при инверсном входном входе).

Таким образом, предлагаемый сумматор при изготовлении его в виде интегральной схемы, может совместить операции суммирования и вычитания беэ дополнительных сигналов управления.