Устройство для потенцирования массивов двоичных чисел

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПОТЕНЦИРОВАНИЯ МАССИВОВ ДВОИЧНЫХ ЧИСЕЛ, содержащее регистр аргумента, первый выход которого соединен с входом первого блока памяти, первый регистр, первый сумматор, первый выход которого подключен к информационному входу триггера, второй блок памяти, , блок сдвига, регистр результата и блок синхронизации, отличающееся тем, что, с целью повышения быстродействия при обработке массивов чисел, в него введены восемь регистров, блок памяти и два сумматора, второй выход регистра аргумента соединен с информационньлм входом первого регистра, выход которого подключен к первому входу первого сумматора, второй вход которого соединен с выходом второго регистра , выход первого блока памяти подключен к информационным входам второго и третьего регистров, выход первого-регистра соединен с информационным входом четвертого регистра, выход которого подключен к входу второго блока памяти, второй выход первого сумматора соединен с информационным входом .пятого регистра, выход которого подключен к входу третьего блока памяти, выход триггера соединен с первым входом второго сумматора, второй вход которого подключен к выходу шестого регистра, информационный вход которого соединен с выходом третьего регистра, выход второго блока памяти подключен к информационному входу седьмого регистра,, выход которого соединен с первым входом третьего сумматора, выход третьего блока памяти подклюсл чен к информационному входу восьмого регистра, выход которого соединен с первым входом блока сдвига, выход которого подключен к второму входу третьего сумматора, выход второго сумматора соединен с информационным входом девятого регистра, выход ко . торого подключен к второму входу блока сдвига, выход третьего сумматора 4;: соединен с информационным входом регистра результата, управляющий вход 00 05 устройства соединен с входом блока синхронизации, выход которого подключен к управляющим входам всех реNI гистров и триггера. О5

СОЮЭ СОВЕТСКИХ

М И

РЕСПУБЛИК

3(5В G 06 F 7 556

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТНРЬГГИЙ

l (21) 3458417/18-24 (22) 24.06.82 (46) 23.09.83. Вюл. 9 35 (72) А.A. Мельник (53) 681.326(088. 8) (56) 1.. Авторское свидетельство СССР

9 330448, кл. G 06 F 5/02, 1970

2. Авторское свидетельство СССР

Р 641448 кл. С Об Р 7/38, 1976 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ПОТЕНЦИРОВА-.

НИЯ МАССИВОВ ДВОИЧНЫХ ЧИСЕЛ, содер- жащее регистр аргумента, первый выход которого соединен с входом первого блока памяти, первый регистр, первый сумматор, первый выход кото" рого подключен к информационному входу триггера, второй блок памяти, блок сдвига, регистр результата и блок синхронизации, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия при обработке массивов чисел, в него введены восемь регистров, блок памяти и два сумматора, второй выход регистра аргумента соединен с информационным входом первого регистра, выход которого подключен к первому входу пер-, вого сумматора, второй вход которого соединен с выходом второго регистра, выход первого блока памяти подключен к информационным входам второго и третьего регистров„ выход

„„SU„„1043646 A первого-регистра соединен с информационным входом четвертого регистра, выход которого подключен к входу второго блока памяти, второй выход первого сумматора соединен с информационным входом .пятого регистра, выход которого подключен к входу третьего блока памяти, выход триггера соединен с первым входом второго сумматора, второй вход которого подключен к выходу шестого регистра, информационный вход которого .соединен с выходом третьего регистра, выход второго блока памяти подключен к информационному входу седьмого регистра, выход которого соединен с первым входом третьего сумматора, выход третьего блока памяти подключен к информационному входу восьмого ф/) регистра, выход которого соединен с первым входом блока сдвига, выход С которого подключен к второму входу третьего сумматора, выход второго сумматора соединен с информационным входом девятого регистра, выход ко- .Обреа торого подключен к второму входу бло-.ра ка сдвига, выход третьего сумматора соединен с информационным входом ре- Д йв гистра результата, управляющий вход (е, устройства соединен с входом блока синхронизации, выход которого под- © ) ключен к управляющим входам всех ре- Д ( гистров и триггера.

С5

1043646

Изобретение относится к вычислительной технике н предназначено для использования в высокоскоростных универсальных и специализированных вычислительных устройствах, предназначенных для обработки больших мас- 5 сизов данных.

Известно устройство для потенци " рования, содержащее регистр аргумента, два блока памяти, узел сдвига, триггер и коммутатор 11 . . Наиболее близким по технической сущности к предлагаемому является устройство для потенцирования, содержащее регистр аргумента, два блока памяти, узел сдвига, трйггер, блок управления, коммутаторы, буферный регистр, регистр результата и сумматор. Быстродействие данного устройства не превышает Т = 21 „ +

+ 2tsû6+ сде где 1см — вРемя суммирования на сумматоре, t 6 6 вРемЯ выбоРки иэ памнти, Фсдв — вРемя осуществления сдвига в блоке сдвига (2 ).

Недостатком известных устройств является низкое быстродействие.

Цель изобретения — повышение быстродействия при обработке массивов чисел.

Поставленная цель достигается тем, что в устройство для потенцирования массивов двоичных чисел, содержащее регистр аргумента, первый выход которого соединен с входом первого блока памяти, первый. регистр, первый сумматор, первый выход которого подключен к информационному входу триггера, второй блок памяти, блок сдвига, регистр результата и блок синхронизации, введены восемь регистров„ блок памяти и два сумма- 46 тора, второй выход регистра аргумента соединен с информационным -входом первого регистра, выход которого подключен к первому входу первого сумматора, второй вход которого сое- 45 динен с выходом второго регистра, выход первого блока памяти подключен к информационным входам второго и третьего регистров, выход первого регистра соединен с информационным входом четвертого регистра, выход которого подключен к входу второго блока памяти, второй вход первого сумматора соединен с информационным входом пятого регистра, выход которого подключен к входу третьего блока памяти, выход триггера соединен с первым входом второго сумматора, второй вход которого подключен к выходу шестого регистра, информационный вход которого соединен с выходом третьего регистра, выход второго блока памяти подключен к информационному входу седьмого регистра, выход которого соединен с первым входом третьего сумматора, выход 65 третьего блока памяти подключен к информационному входу восьмого регистра, выход которого соединен с первым входом блока сдвига, выход которого соединен с первым входом блока сдвига, выход которого подключен к второму входу третьего сумматора, выход второго сумматора соединен с информационным входом девятого регистра, выход которого подключен к второму входу блока сдвига, выход третьего сумматора соединен с информационным входом регистра результата, управляющий вход устройства соединен с входом блока синхронизации, выход которого подключен к управляющим входам всех регистров и триггера.

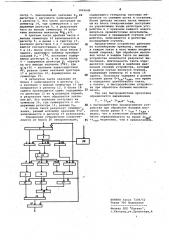

На чертеже представлена блок-схема предлагаемого устройства, Устройство содержит регистр 1 аргумента, первый 2, второй 3 и третий 4 блоки памяти, первый 5, второй

6, третий 7, четвертый 8, пятый 9, шестой 10, седьмой 11,восьмой 12 и девятый 13 регистры, первый 14, второй 15 и третий 16 сумматоры, триггер 17, блок 18 сдвига, регистр 19 результата и блок 20 синхронизации.

Промежуточные регистры 5 — 13 и триггер 17 предназначены для кратковременного запоминания результатов промежуточных вычислений и обеспечения конвейерного способа обработки.

Вычисление. функции 2 от аргуменX та Х (О < Х < 1) производится в устройстве на основе следующих соотношений.

Пусть Хо — число, образованное старшими разрядами аргумента, д Х— число, образованное младшими разрядами аргумента. Тогда

Х Х +аХ Хо

2=2 V =2 о

Для определения точного значения функции 2 к значению Уо необходимо добавить приращение и У, равное хо+,4х х хо лх ау 2 о 2 2 (2 1) откуда, логарифмируя по основанию 2, получаем

Ро ;2 х =х + 0 "2(2 -< ) .

Тогда

8oy d У Хо+ РоЯ-2 (2 -1 м= . =г

Устройство работает следующим образом

В первом такте работы устройства в регистр 1 аргумента 2 поступает аргумент Х. Значение ВХ из этого регистра поступает на блок 2 памяти, хранящий таблицу преобразований

Ео 2 < 2 " -1) .

Во втором такте дробная часть значения из блрка 2 записывается в регистр 6, а характеристика — в ре1043646 гистр 7. Одновременно значение Ха из регистра 1 аргумента записывается в регистр 5. Это число поступает на . сумматор 14, где суммируется с содержимым регистра 6, в результате чего на выходе сумматора 14 полу- 5 чаем значение мантиссы Hog 4 У.

В третьем такте дробная часть с

1 выхода сумматора 14 записывается в регистр 9, а целая — в триггер 17, значения регистров 5 и 7 переписываЮтся соответственно в регистры

9 и 10. После этого на вход блока 3 памяти, хранящего таблицу преобразований У о = 2 «, поступает содержимое регистра 8, а на вход блока

4 — содержимое регистра 9, образуя на его выходе значение 2 ду, где

q,(с >0.) — значение характеристики

4У, равное сумме значений триггера

17 и регистра 10, формируемое на сумматоре 15. 20

В четвертом такте значение иэ блока 3 записывается в регистр 11, а значение с выхода сумматора 15 записывается в регистр 13 ° В блоке 18 сдвига производится сдвиг содержимо- 25 го регистра 12 на « разрядов вправо, в результате чего образуется значение ЬУ. Это значение поступает на сумматор 16, где суммируется,с содержимым регистра 11; равным Уо. 30

В пятом такте результат суммироХ вания, равный искомому значению У=2 записывается в регистр 19 результата.

Управление устройством осуществляется от блока 20 синхронизации, 35 содержащего генератор тактовых импульсов со схемами пуска и останова.

После прихода сигнала пуска импульсы иэ блока синхронизации поступают на управляющие входы регистров устройства и с приходом каждого нового импульса промежуточные реэульааты, полученные в предыдущей ступени уст- ройства, записываются в регистры последующей ступени.

Предлагаемое устройство работает по конвейерному принципу, поэтому в каждом такте в него можно вводить новый операнд. При обработке массивов чисел в каждом такте на выходе устройства появляется результат вычисления. Длительность такта определяется задержкой в наиболее медленной ступени устройства, который в данном случае является ступень, содержащая сумматор 16 и блок 18 сдвига. Поскольку задержка в данной ступени равна T=t +t s, зто время и определяет длительность такта, а значит, и быстродействие устройства при обработке больших массивов чисел.

Так как быстродействие прототипа определяется выражением

2 см 2"вь Б+ аде, а быстродействие предлагаемого устройства при обработке больших массивов чисел равно Т = t + t«; s, видно, что в известном устройстве числа обрабатываются на время 2 Э +

+ в медленнее, чем в предлагаемом.

ВНИИПИ Заказ 7339/52

Тираж 706 Подписное

Филиал ППП "Патент", r. Ужгород,ул. Проектная, 4