Многоканальное устройство для управления буферизацией данных

Иллюстрации

Показать всеРеферат

, МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ БУФЕРИЗАЦИЕЙ ДАННЫХ, содержащее в каждом канале триггер, нулевой выход которого является соответствующим выходом разрещения загрузки памяти устройства , в первом канале - элемент ИЛИ, входы которого соединены с группой управляющих входов загрузки памяти устройства, а выход соединен с входом установки единицы триггера первого канала, во втором канале - элемент И, а в остальных каналах - злементы И и ИЛИ, причем во. всех каналах, кроме первого и второго , первый вход и выход элемента И соединены соответственно с выходом элемента ИЛИ и входом установки единицы триггера того же канала, а первый вход элемента ИЛИ соединен с единичным выходом триггера предшествующего канала, синхронизирующие входы триггеров всех каналов соединены с входом синхросигнала устройства, а второй вход элемента ИЛИ третьего канала соединен с единичным выходом триггера первого канала, отличающееся тем, что, с целью повыщения достоверности в работе в него введены триггер контроля флажков, триггер сбоя флажков, два элемента сложения по модулю два и элемент ИЛИ, причем вход установки единицы триггера второго канала соединен с выходом элемен та И второго канала, во всех каналах, кроме последнего, вход установки нуля триггера Ьое-; динен с нулевым выходом триггера последующего канала, а вход сброса - с входом сброса устройства и инверсным входом установки единиць триггера контроля флажков, синхронизирующий вход которого соединен с входом синхросигнала устройства, а вход установки нуля и прямой вход установки единицы - с выходом первого элемента сложения по модулю два, первый вход которого соединен с выходом элемента ИЛИ первого канала, второй вход - с вторым входом элемента И, входом установки нуля триггера последнего канала и выходом элемента ИЛИ, входы кото8 рого являются группой вхедов разгрузки па (П мяти устройства, второй вход элемента И каналов, кроме второго и последнего, соедис нен с единичным выходом триггера последующего канала, второй вход элемента ИЛИ каналов , кроме первого и третьего, подключен к выходу элемента ИЛИ предыдущего канала, первый и второй входы элемента И второго канала соединены соответственно с единичными выходами триггеров первого и третьего каналоВ: dt вход сброса триггера сбоя флажков является входом гащения сбоя устройства, синхронизиСП рующий вход соединен с выходом синхросиго нала устройства, вход установки нуля - с шиной логического нуля, а вход установки единицы - с выходом второго элемента сложения по модулю два, группа выходов которого соедииена 1 с нулевыми входами триггеров каналов и единичным выходом триггера контроля флажков, а выход - с выходом сбоя флажков устройства .

(19) (11) СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) G 06 F 9/46; G 06 F 3/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3450214/18 — 24 (22) 11.06.82 (46) 23.09.83. Бюл. й0 35 (72) М. А. Верига и Ю. В. Тихович (53) 681.325 (088.8) (56) 1. Каналы ввода — вывода ЭВМ ЕС вЂ” 1020, М., "Статистика", 1976, с. 131.

2. Авторское свидетельство СССР

N 849213, кл. G 06 F 9/46, 1979 (прототип); (54) (57), МНОГОКАНАЛЬНОЕ УСТРОЙСТВО

ДЛЯ УПРАВЛЕНИЯ БУФЕРИЗАЦИЕЙ ДАННЫХ, содержащее в каждом канале триггер, нулевой выход которого является соответствующим выходом разрешения загрузки памяти устройства, в первом канале — элемент ИЛИ, входы которого соединены с группой управляющих входов загрузки памяти устройства, а выход соединен с входом установки единицы триггера первого канала, во втором канале — элемент

И; а в остальных каналах — элементы И и ИЛИ, причем во. всех каналах, кроме первого и второго, первый вход и выход элемента И соединены соответственно с выходом элемента ИЛИ и входом установки единицы триггера того же канала, а первый вход элемента ИЛИ соединен с единичным выходом триггера предшествующего канала, синхронизируюшие входы триггеров всех каналов соединены с входом синхросигнала устройства, а второй вход элемента

ИЛИ третьего канала соединен с единичным выходом триггера первого канала, о т л ич а ю щ е е с я тем; что, с целью повышения достоверности в работе в него введены триггер контроля флажков, триггер сбоя флажков, два . элемента сложения по модулю два и элемент

ИЛИ, причем вход установки единицы триггера второго канала соединен с выходом элемента И второго канала, во всех каналах, кроме последнего, вход установки нуля триггера соединен с нулевым выходом триггера последующего канала, а вход сброса — с входом сброса устройства и инверсным входом установки единицы триггера контроля флажков, синхроннзирующий вход которого соединен с входом синхросигнала устройства, а вход установки нуля н прямой вход установки единицы — с выходом первого элемента сложения по модулю два, первый вход которого соединен с выходом элемента ИЛИ первого канала, второй вход — с вторым входом элемента И, входом установки нуля триггера последнего канала и выходом элемента ИЛИ, входы котоф рого являются группой вхвдов разгрузки памяти устройства, второй вход элемента И каналов, кроме второго и последнего, соединен с единичным выходом триггера последующего канала, второй вход элемента ИЛИ каналов, кроме первого и третьего, подключен к выходу элемента ИЛИ предыдущего канала, первый и второй входы элемента И второго канала соединены соответственно с единичными выходами триггеров первого и третьего каналов, вход сброса триггера сбоя флажков является входом гашения сбоя устройства, синхронизирующий вход соединен с выходом синхросигнала устройства, вход установки нуля — с ши- ной логического нуля, а вход установки единицы — с выходом второго элемента сложения по модулю два, группа выходов которого соединена с нулевыми входами триггеров каналов и единичным выходом триггера контроля флажков, а выход — с выходом сбоя флажков устройства.

1043656

Ф

Изобретение относится к вычислительной технике и может быть использовано в каналах ввода — вывода ЭВМ и в устройствах для сопряжения повышенной надежности, Известно устройство для управления буферизацией данных, которое содержит триггеры хранения и триггеры состояния полного —.пустого регистров буферной памяти, триггеры передачи из предыдущего в последующий регистр буферной памяти. Продвижение данных в устройстве 10 осуществляется последовательно через все регистры буферной памяти, причем байт данных в буферной памяти всегда сдвигается за один машинный такт до регистра буферной памяти, триггер состаяния "полный" которого установлен (1!.

Однако аппаратура, управляющая приемом, продвижением и хранением данных в устройст- ве не контролируется,.что.ведет к значительному снижению надежности работы всего устройства.

Наиболее близким к изобретению по технической сущности является многоканальное устройство для управления буферизацией данных, содержащее в каждом канале триггер, в первом канале — элемент И, в друтих кана.лах, кроме последнего, — два элемента И, и первом и последнем каналах элемент ИЛИ, во втором и последнем каналах — элемент задержки, а в других — два элемента ИЛИ, причем. выход первого элемента И канала соединен с первым входом триггера канала, инверсный выход которого является соответствующим выходом устройства, первый и второй управляющие входы которого соединены соответственно с первым и вторым управляющим выходами устройства и через элемент ИЛИ первого канала с вторым входом триггера первого канала и инверсным входом элемента И первого канала, третий управляющий вход является третьим управляющим выходом устрой- 40 ства и соединен с входом первого элемента

- ИЛИ второго канала и инверсным входом первого элемента И второго канала, прямой выход триггера первого канала соединен с первым входом первого элемента ИЛИ третьего канала и 45 через элемент задержки с первым входом второго элемента И второго канала и первым прямым входом элемента И первого канала, инверсный выход триггера второго канала соединен с вторым прямым входом элемента 50

И первого канала, выход второго элемента И второго канала соединен с вторым входом первого элемента ИЛИ второго канала, выход первого элемента ИЛИ второго канала соединен с вторым входом триггера второго канала (21. SS

Недостатки известного устройства состоят в низкой достоверности работы устройства и больших аппаратурных затратах.

Цель изобретения — повышение достоверности работы устройства и снижения аппаратурных затрат.

Поставленная цель достигается тем, что в многоканальное устройство, содержащее в каждом канале триггер, нулевой выход которого является соответствующим выходом разрешения загрузки памяти устройства, в первом канале — элемент ИЛИ, входы которого соединены с группой управляющих входов загрузки памяти устройства, а выход соединен с входом установки единицы триггера первого канала, во втором канале — элемент И, а в остальных каналах — элементы .И и ИЛИ, причем во всех каналах, кроме первого и второго, первый вход и выход элемента И соединены соответственно с выходом элемента ИЛИ и входом установки единицы триггера того же канала, а первый вход элемента ИЛИ соединен с единичным выходом триггера предшествующего канала, синхронизируюшие входы триггеров всех каналов соединены с входом синхросигнала устройства, а второй вход элемента ИЛИ третьего канала соединен с единичным выходом триггеl ра первого канала, введены триггер контроля флажков, триггер сбоя флажков, два элемента сложения по модулю два и элемент ИЛИ, причем вход установки единицы триггера второго канала соединен с выходом элемента И второго канала, во всех каналах, кроме последнего, вход установки нуля триггера соединен с нулевым выходом триггера последующего канала, а вход сброса — с входом сброса устройства и инверсным входом установки единицы триггера контроля флажков, синхронизирующий вход которого соединен с входом синхросигнала устройства, а вход установки нуля и прямой вход установки единицы — с выходом первого .элемента сложения по модулю два, первый вход которого соединен с выходом элемента

ИЛИ первого канала, второй вход — с вторым входом элемента И, входом установки нуля триггера последнего канала и выходом элемента ИЛИ, входы которого являются группой входов разгрузки памяти устройства, второй вход элемента И каналов, кроме второго и последнего, соединен с единичным выходом триггера последующего канала, второй вход элемента ИЛИ каналов, кроме первого и третьего, подключен к выходу элемента ИЛИ предыдущего канала, первый и второй входы элемента И второго канала соединены соответственно с единичными выходами триггеров первого и третьего каналов, вход сброса триггера сбоя.флажков является .входом гашения сбоя устройства, синхронизирующий вход соединен с входом синхросигнала устройства, вход установки нуля — с шиной логического нуля, а вход установки единицы — с выходом з 10436 второго элемента сложения по модулю два, группа входов которого соединена с нулевыми : входами триггеров каналов и единичным выходом триггера контроля флажков, а выход с выходом сбоя флажков устройства.

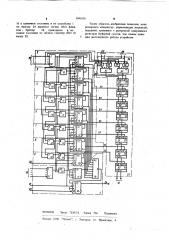

На чертеже представлена блок — схема предлагаемого устройства.

Устройство содержит (для определенности) восемь каналов 2 — 9, включающих элементы

ИЛИ 10, элементы И 11 и триггеры 12, элементы 13 и 14 сложения по модулю два, триггер 15 контроля флажков, триггер. 16 сбоя флажков, элемент ИЛИ 17, группы 18 и 19 управляющих входов загрузки памяти устройст- ва, вход 20 сброса устройства, вход 21 синхро- !5 сигнала устройства, вход 22 гашения сбоя, выходы 23 разрешения загрузки памяти устройства и выход 24 сбоя флажков. . Буферная память включает восемь регистров 26 — 33 (показаны два их разряда), коммутатор 34 групп информационных входов 35 и

36; состоящий из групп элементов ИЛИ 37 и групп элементов И 38, адресные входы 39 коммутатора 34 и информационные выходы 40 памяти.

Устройство 1 служит для управления прие.мом, хранением информации от группы источников (показаны входы 35 и 36 для подключения двух источников) и выдачи информации

1 по выходам 40 по сигналам от группы приемников, подаваемым на входы 19.

Устройство работает следующим образом, Нулевые выходы триггеров 12 (флажков) управляют приемом информации в соответствующий регистр памяти 25. Единичные выходы триггеров 12 указывают, что соответствующие им.регистры 26 — 33 памяти 35 заполнены.

Пусть регистры 26 — 33 служат для хранения байтов данных. Байты данных загружаются в регистры 26 — 33 по одному байту череэ коммутатор 34 по входам.35. Принять и в регистр 2640 байт данных сдвигается до регистра 33 и выда1 ется из него на информационные выходы 40, если на выхода". 23 устройства 1 присутствуют единичные сигналы.

Байт данных от первого, например, источни- 45 ка поступает на информационный вход 35 и при наличии управляющего сигнала на первой шине

18 входа передается через коммутатор 34 на информационные входы регистра 26. Высокий уровень на нулевом выходе триггера 12 кана ла 2 указывает на отсутствие информации в регистре 26. Триггер 12 канала 2 устанавливается в единичное состояние по сигналу загрузки с входа 18 через элемент ИЛИ 10 и заднему фронту синхросигнала, поступившему 55 на вход 21, указывая на присутствие информации в регистре 26, информация из которого переписывается последовательно до первого эа56 4 нятого информацией регистра 25 памяти. О том, что регистр занят информацией, указывает низкий уровень на нулевом выходе соответствующего ему триггера 12. Если в регистрах

26 — 33 отсутствует информация, содер,кимое регистра 26 переписывается в регистр 33, а единичное состояние флажка 12 канала 2 переписывается через элементы ИЛИ 10 и

И 11 по заднему фронту синхросигнала с входа 21 в триггер 12 канала. Поэтому же сйнхросигналу триггер 12 канала 2 сбрасывается в нулевое состояние, указывая, что регистр 32 освободился для приема информации. Следующая информация от источника заносится аналогичным образом и размещается в регистре

32. Одновременно в памяти 25 может храниться 1-8 байтов данных.

Для выдачи информации из устройства сигнал разгрузки от приемника поступает на соответствующую шину 19 входа и через элемент ИЛИ 17 сбрасывает триггер 12 канала 9 в нулевое состояние. Информация в приемник выдается из регистра 33 по информационному выходу 40. Устройство позволякт одновременно выполнять загрузку информации в регистр 26 и разгрузку информации из регистра 33.

Для контроля правильности работы и повышения надежности устройство содер.кит триггер

15 контроля флажков, триггер 16 сбоя флажков и элементы 13 и 14 сложения, которые обеспечивают слежение за состоянием триггеров 12, состояние которых указывает на количество байтовых данных, одновременно хранящихся в регистрах 26 — 33. Триггер 15 дополняет информацию о кбличестве байтов данных, находящихся в регистрах, до нечетного числа. В первоначальном состоянии по сигналу сброса по входу 20 триггеры 12 сбрасываются, а триггер 15 устанавливается в единицу. При занесении. информации в регистр 26 триггер 15 через элемент 13 сложения меняет свое состояние на противоположцое по заднему фронту синхросигнала на выходе 21 одновременно с установкой триггера 12 канала,2, При выдаче информации из регистра 33 триггер 15 также меняет свое состояние на противоположное и одновременно происходит сброс триггера 12 канала 9. При одновременном занесении байта данных в регистр 26 и выдачи другого байта данйых из регистра 33 триггер 15 не меняет своего состояния. Сигналы с нулевых выходов триггеров 12 и единичного выхода триггера 15 поступают на входы элемента 14 сложения, где суммируются Ilo модулю два. В случае, если нарушается четность числа байтовых данных, хранящихся на регистрах 26--33, на инверсном выходе элемента 14 сложения возникает высокий уровень, который устанавливает триггер

1043656

ВНИИПИ Заказ 7339j52. Тираж 706 Подписное. Филиал П ПП "Патент", г. Ужгород, ул. Проектная, 4

16 в единичное состояние и из устройства 1 по выходу 24 выдается сигнал сбоя флажков - Tparrep 1б приводится в исходное состояние по сигналу гашения сбоя по входу 22.

Таким образом, изобретение позволяет контролировать аппаратуру, управляющую загрузкой, передачей, хранением и разгрузкой содержимого регистров буферной памяти, тем самым повы5 шая достоверность работы устройства.