Цифровой адаптивный корректор дискретного сигнала

Иллюстрации

Показать всеРеферат

(19) (И) СОЮЗ СОВЕТСНИХ

СООИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

В Н 04 В 3/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HOMHTET СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3359681/09 (22) 26.11.81 (46) 23.09.83. Бюл, и 35 (72) С.В.Стукалов, Л.Г.Израильсон и Л.А.Гельбрас (53) 621.395.664(088.8) (56) 1. Патент США И 3633105, кл. 325-42, 1970.

2. Авторское свидетельство СССР

N 801269, кл..Н 04 В 3/04, 1978 (прототип). (54)(57) ЦИФРОВОЙ АДАПТИВНЫЙ КОРРЕКТ0Р ДИСКРЕТНОГО СИГНАЛА, содержащий последовательно соединенные узел двухканального аналого-цифрового преобразования,.блок памяти выборок и блок умножения, причем входы узла двухканального аналого-цифрового преобразования являются аналоговыми входами устройства, тактовым вхо" дом которого является вход блока про-. граммного управления, первый выход которого подключен к первому входу блока корреляции, к второму входу бло-. ка памяти выборок, к первым входам первого и второго сумматоров и бло- .-, ка памяти коэффициентов передачи, другой вход которого соединен с выхо-. дом блока корреляциы, первые выходы первого и второго сумматоров являются выходами устройства, а вторые выходы подключены к второму входу блока корреляции, другой выход узла двухканального аналого-цифрового преобразования подключен к другому входу блока программного управления, отличающийся тем, что, с целью повышения. помехоустойчиво:сти и скорости настройки корректора путем реализации среднеквадратично- го алгоритма настройки в него введены формирователь кода эталонного сигнала, первый, второй и третий коммутаторы, при этом выход формирова- теля кода. эталонного сигнала соединен с первым входом первого коммутатора, второй вход которого соединен со вторым выходом блока программного управления, третий выход которого подключен к первому входу второго коммутатора, второй вход которого соединен с выходом блока памяти коэффициентов передачи, а третий и четвертый входы. которых соединены с выходом первого коммутатора, выход блока умножения подключен к третьему входу первого коммутатора, и через третий коммутатор подключен к третьему входу блока корреляции, четвертый вход которого соединен co . вторым выходом блока памяти выборок, а четвертый выход блока программного управления подключен к другому входу третьего коммутатора.

1043830 3

30

Изобретение относится к электросвязи и другим областям, связанными с приемом модулированных сигналов данных, передаваемых по каналам тональной частоты (ТЧ), и,предназна" чено для коррекции межсимвольной интерференции ИСИ в модулированных сигналах, сформированных однополосными или двухполосяыми многопозиционными методами модуляции.

Известен цифровой адаптивный корректор дискретного сигнала, .содержащий последовательно соединенные аналого-цифровой преобразователь (АЦП), блок памяти выборок и арифметический блок, состоящий из блока умножения и сумматора, причем входы ,АЦП являются аналоговыми входами корректора, тактовый вход которого является входом программного блока, второй вход которого подключен к другому выходу АЦП, а тактовый выход программного блока подключен к входам блока памяти выборок,,арифметического блока и блока памяти коэффициентов передачи, выход которого подключен к третьему входу арифметичес" кого блока, один выход которого является выходом устройства, а другой подключен к третьему. входу блока памяти выборок, другой выход которого через блок корреляции подключен к другому входу блока памяти, коэффициентов (11.

Однако в этом корректоре недостаточны помехоустойчивость данных сигналов и скорость.-настройки, так как в нем используется знаковый алгоритм настройки корректора.

Наиболее близким к изобретению является цифровой адаптивный корректор дискретного сигнала, содержащий последовательно соединенные узел двухканального аналого-цифрового преобразования, блок памяти выборок и блок умножения, причем входы узла двухканального аналого-цифрового преобразования являются аналоговыми входами устройства, тактовым входом которого является вход блока программного управления, первый выход которого подключен к первому входу блока корреляции, ко второму входу блока памяти выборок, к первым входам первого и второго сумматоров и блока памяти коэффициентов передачи, другой вход которого соединен с выходом блока корреляции, первые выходы первого и второго сумматоров яв" ляются выходами устройства, а вторые выходы подключены к второму входу блока корреляции, другой выход узла двухканального аналогоцифрового преобразования подключен к другому входу блока программного управления f2).

Однако известное устройство имеет недостаточную помехоустойчивость и дальность передачи сигналов дан" ных, и недостаточную скорость на- стройки.

Цель изобретения - повышение помехоустойчивости и скорости настрой" ки корректора путем реализации среднеквадратичного алгоритма настройки.

Поставленная цель достигается тем, что в цифровой адаптивный корректор дискретного сигнала, содержащий последовательно соединенные узел двухканального аналого-цифрового преобразования, блок памяти выборок и блок умножения, причем входы узла двухканального аналого-цифрового преобразования являются аналоговыми входами устройства, тактовым входом которого является вход блока программно" го управления, первый выход которого подключен к первому входу блока корреляции, ко-второму входу блока памяти выборок,к первым входам первого и второго сумматоров и блока памяти коэффициентов передачи, другой вход которого соединен с выходом блока корреляции, первые выходы первого и второго сумматоров являются выходами устройства, а вторые выходы под" ключены к второму входу блока корреляции, другой выход узла двухканаль40 ного аналого-.цифрового преобразова,ния подключен к другому входу блока программного управления, введены формирователь кода эталонного сигнала, первый, второй и третий коммутаторы, 45 при этом выход формирователя кода эта* лонного сигнала соединен с первым входом первого коммутатора, второй вход которого соединен со вторым выходом блока программного управления, 50 третий выход которого подключен к первому входу второго коммутатора, второй вход которого соединен.;с выходом блока памяти коэффициентов передачи, а третий и четвертый входы подключены к третьим выходам первого и второго сумматоров, вторые входы которых соединены с выходом первого коммутатора, выход блока умножения подключен к третьему входу перво1043830 го коммутатора, и через третий коммутатор подключен к третьему входу блока корреляции, четвертый вход которого соединен со вторым выходом блока памяти выборок, а четвертый выход блока программного. управления подключен к другому входу третьего коммутатора.

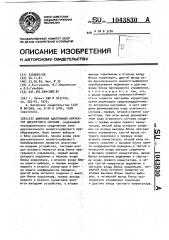

На фиг. 1 приведена структурная электрическая схема цифрового адап" .!О тивного корректора; на фиг. 2 - мас" сивы коэффициентов и выборок.

Цифровой адаптивный корректор дискретного сигнала содержит приемник

1, адаптивный корректор 2, узел 3 -15 двухканального аналого-цифрового преобразования, блок Ц программного управления, блок 5 памяти выборок, блок 6 корреляции, блок 7 памяти коэффициентов передачи, формирователь 20

8 кода эталонных сигналов, блок 9 умножения, коммутаторы 10-12, сумматоры 13 и 14.

Цифровой адаптивный корректор дискретного сигнала работает следу- 25 ющим образом. лц

Аналоговые сигналы Л, и о с выходов демодуляторов приемника 1 поступают на узел 3 двухканального аналого-цифрового преобразования, где производится стробирование этих сигналов в отсчетные моменты .времени, запоминание и хранение амплитуд полученных напряжений выборок и преоб" разование этих напряжений в П -раз35 рядные кодовые числа. Процесс преоб- . разования осуществляется так, .что сначала преобразуется сигнал Ь; с выхода первого демодулятора, а затем сигнал о; с выхода второго демодуля- .40

Q тора (не показаны) приемника 1. В та" кой же очередности производится запись в блок 5 памяти выборок двухраэрядных чисел выборок, полученных в результате преобразования. После окончания 45 процесса преобразования в,узле 3 формируется сигнал "Пуск" и блок 4 вырабатывает сигналы, необходимые для работы блока 5 памяти выборок и блока 7 памяти коэффициентов передачи, и сумматоров 13 и 14. В это время

50 коммутаторы 10-12 установлены в исходное положение,. при котором блок 7 памяти коэффициентов передачи подключен к блоку 9 умножения, выход блока 9 умножения подключен к сумматорам 55

13 и 14, и на вход блока 6 корреляции через коммутатор 12 сигнал от блока 9 умножения не поступает.

На основании принятого среднеквад; ратичного алгоритма настройки сигналы управления для изменения коэффици" ентов передачи регуляторов отводов адаптивного корректора 2 вырабатываются в блоке 6 корреляции в соответствии со следующими выражениями:

При .компенсации собственного мешающего влияния

Ь; =ео а 1 (1)

sgnh sgne i sgna +sgna„; (2)

sgnh sgne + sgna + з9па ° (")

При компенсации перекрестного мешающего влияния (5)

sgnh"; sgneî sgnaî+ sgna," (6)

sgnh; з9пе t sgna + sgna;. ()

В выражениях (1)-(8) приняты следу" ющие обозначения: з9па и з9па - знак проекции сигнала, подверженного мешающему влиянию, на ортогональные когерентные колебания R u

В

Q соответственно;

sgna и з9па - знак проекции сигЛ 1 нала, создавшего мешающее влияние на ортогональные когерентные колебания R и Q соответЯ ственно;

sgne . sgne --знак отклонения о о проекции амплитуды откорректированного сигнала от номинала на когерентные. колебания R и (.Я соответственно; е и ео -. величина отклонения амплитуды оТкорректированного .сигнала от номи нала на когерентные колебания R и С1соответственно; а; и а. - величина проекции

1 сигнала, создавшего мешающее влия- ние, на когерентные колебания R

Ъ и Q соответственно, 1043830 . 6

Йа основании выражений (1), (3), (5), (7) определяется величина изменения коэффициента передачи, а на основании выражений (2), (4), (6), (8) ." знак этого изменения.

Коэффициенты передачи регуляторов отводов записываются в блок 7 памяти коэффициентов передачи.

В случае передачи сигналов данных двухполосными или однополосными (при приеме на центральной частоте спектра) методами модуляций массивы коэффициентов и выборок в блоке 5 памяти выборок и блока 7 . памяти коэффициентов передачи после окончания преобразования в узле 3 располагаются друг относительно дру.га так, как это изображено на фиг.2а, где приняты следующие обозначения:

P - -коэффициент передачи регулятора по перекрестной связи; . к - коэффициент передачи регуля,» тора по прямой связи; о.--индекс знакового разряда;

1 - количество разрядов в кодовом числе, отображающем модуль коэффициента передачи регуля:тора отвода и модуль выборки (n=l+1);

f - номер отвода слева от центрального;

m - -номер отвода справа от центрального;

r .- выборка сигнала.с выхода первого (синфазного) демодулятора;

q - выборка сигнала с выхода второго (квадратурного) демодуля. тора.

По командам. блока 4 -из блока 5 памяти выборок непосредственно, а из блока 7 памяти коэффициентов пе редачи через второй коммутатор 11 на

-. блок 9 умножения поступают два кодо вых числа, соответствующие модулям и полярностям кодов выборки и коэффициента передачи соответствующего отвода корректора 2 ° Причем сначала в блок 9 умножения поступает код вы". борки синфаэного демодулятора.,: а за.тем код выборки квадратурного демодулятора приемника 1 для умножения на один и тот же коэффициент. пере.дачи регулятора отвода корректора 2.

Полученные произведения двух riap чи,сел передаются через коммутатор 10.

1О

30 одновременно на входы сумматрров 13 и 14. Однако операции суммирования производятся раздельно для синфазных и квадратурных сигналов, в соответствии с сигналами управления, поступающими иэ программного блока 4 в каждый из сумматоров 13 и 14 соответственно.

Затем по команде программного блока 4-иэ блоков 5 памяти выборок и блока 7 памяти коэффициентов rte" редачи,на вход блока 9 умножения по- . даются кодовые числа, соответствующие операциям со следующих отводов корректора 2. Получейные произведения алгебраически суммируются в сум- маторах 13- и 14 с числами, хранящимися в них от предыдущей команды программного блока 4. Этот процесс будет продолжаться до тех пор, пока в сумматорах 13 и 14 не будут записа ны суммы, полученные в результате суммирования произведений кодов вы. борок и коэффициентов передачи регуляторов по прямой связи для всех отводов корректора 2. По окончании этого процесса массивы коэффициентов и выборок в- блоках 4 и 7. памяти будут располагаться так,. как это .представлено:на фиг. 2б.

Далее, процесс умножения кодов коэффициентов передачи по перекрестной связи и выборок и последовательного суммирования произведений

\ повторяется аналогично. . После окончания .этого процесса результирующие суммы с выходов сумма" торов 13 и 14 поступают в приемник.

1 для декодирования и формирования сигналов управления корректором 2.

Затеи по команде программного блока (9) 4 коммутатор 1О.отключает выход блока 9 умножения от входов сумматоров

13 и 14 и подключает. ко входам сум45 маторов 13 и 14 формирователь 8 ко- . да эталонного сигнала. Формирователь

8 кода эталонного сигнала преобра зует сигналы управления, вырабатываемые в приемнике 1 и определяющие нормированное значение амплитуд

Ф откорректированных сигналов а и а на выходах сумматоров 13 и ?4, в два

l""ðàçðÿäíûõ кодовых числа 1а 1 и

la ). B сумматорах 13 и 14 формируются сигналы, отображающие величины оаибки (1 . и11Я в соответствии с выражениями

I1„ 1а - la, ;

7 .. 1043

1©-1. 1- )©- (1О>

Затем по команде программного блока 4 выход блока 9 умножения через коммутатор. 12 подключается к блоку 6 корреляции, а коммутатор 11 отключает блок 7 памяти коэффициентов передачи от блока 9 умножения и на вход последйего подключает требуемый сигнал ошибки I или 1 . В блоке 9 1р

Я, умножения производится последователь: ное умножение кодовых чисел выборок на кодовое число,,соответствующее требуемому значению -сигнала ошибки

1о или 1О . Полученные произведения, Я знак которых выбирается в соответствии с выражениями (2), (4), (6), (8), определяют величину и направле-" ние изменения, коэффициентов передачи . регуляторов отводов. При этом массивы выборок и коэффициентов передачи . в блоках .5 памяти выборок и блока 7 памяти коэффициентов передачи располагаются так, как изображено.на фиг. 2а.. : . . 25

Далее по командам программного блока 4 снова начинают работать блоки .5 памяти выборок и, блок 7 памяти коэффициентов,. передачи, но сигналы управления .на сумма-. торы 13 и 14 не поступают. При

830 8 этом осуществляется изменение коэффициентов передачи регуляторов отводов в соответствии с формулами (1)-(8). Процесс, повторяется до тех пор, пока в блоке 7 памяти коэффициентов передачи не будут записаны новые значения коэффициентов: . передачи регуляторов по прямым и пе рекрестным связям для всех отводов корректора 2.

После этого по команде программного блока 4 коммутаторы 10-12 устанавливаются в исходное положение до поступления следующих элемештов сигнала на вход блока 3 корректора 2. В процессе настройки корректора 2 в блоке 7 памяти коэффициентов переда. чи записываются такие числа коэффициентов передачи для регуляторов от- . водов, при которых величина МСИ ми" . нимальна.

Поскольку при изменении коэффициентов передачи учитывается не только направление, изменения, но и величина сигналов ошибки, определяемая выражениями (g) и (10), то процесс коррекции существенно ускоряется, повышается точность коррекции, а так же допустимая величина исходных искажений характеристик канала ТЧ, что эквивалентно увеличению дальности передачи сигналов. данных.

1043830. 1043830 ту а f У1 ® ) ® °

«зев . Фю яе ню ню

° ° е

° °

° ° ф °

° с

fs rr. ° ., fл гг:.р

pr -1

)) р rn

° ° е ф 0

Р 1

У Xf

1 Р

° °

° °

Ф-У

Ку

° ° г ) ° ° ° р Р1 ) ® т

1 р е

° °

° . °

° Э

gl Ps a)Ps ). s> Д) / еее) ° ф и Др n)ee Чи pi, ъ

)Г у, sss-g в

8НИИПИ Заказ 7358/6l Тираж 677 Подписное ююе ЮЮЮ ° Э филиал ППП "Патент", r. Ужгород, ул. Проектная, 4