Формирователь сигнала для выборки элементов матрицы

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ СИГНА ЛА ВЫБОРКИ ЭЛЕМЕНТОВ МАТРИЦЫ , содержащий выходной транзистор, цва резистора и ц входных транзисторов, базы которых объецинены, коппекторы поцкпючены к базе выкоцного транзистора и через поспецоватепьно соециненные первый и второй резисторы к ишне питания , эмиттеры входных: транзисторов со&цинены с вкоцами, эмиттер выхоцного транзистора подключен к выходной шине, отличающийся тем, что, с цепью увеличения быстродействия, он дополнительно содержит транзистор, циоц и источник тока, причем выход источника тока соединен с катодом оиода, которого подключен к эмиттеру транзистора и базам входных транзисторов, коллектор транзистора соецинен с шиной питания, база - с общим выводом первого и второго резисторов

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК ()9) ())) зсмк) Н 03 К 5/01

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3428234/18-21 (22) 21.04.82 (46) 30.09.83, Бюп. % 36 (72) В. В. Пастон, И. Л. Дробышева и Л. П. Хопоцнова (53) 621.374 (088.8) (56) 1. Патент Ангпии % 1489861, кл. Н 03 К 13/25, 1977.

2. bS 5C Ñ,. 1977, 16, р. 78 {прототип), (54) (57) ФОРМИРОВАТЕЛЬ СИГНАЛА ЩЯ ВЫБОРКИ ОЛЕМЕНТОВ NATPHUbI, соцержащий выхоцной транзистор, два резистора и И вхоцных транзисторов, базы которых объединены, коппекторы поцкпючены к базе выхоцно) о транзистора и через поспецоватепьно соединенные первый и второй резисторы к шине питания, эмиттеры вхоцных транзисторов соединены с вхоцами, эмиттер выхоцного транзистора подключен к выхоцной шине, о т п и ч а ю шийся тем, что, с цепью увепичения быстроцействия, он цопопнительно соцержит транзистор, циоц и источник тока, причем выхоц источника тока соединен с катоном циоца, ацоц которого поцкпючен к эмиттеру транзистора и базам вхоцных транзисторов, коплектор транзистора соединен с шиной питания, база - с общим вывоцом первого и второго резисторов.

1045364

Изобретение относится к импульсной и вычиспитепьной технике и предназначено цпя испопьзования в качестве одного из эпементов управпения матрицей накопитепя памяти интеграпьиого запоминаю- 5 щего устройства.

Известен дешифратор, состоящий из

И -ацреснык входных устройств, прецставпяющик собой эмиттерые повторитеци, каждый из которык поцкпючен к входу 10

ЭСЛ инвертора Pi j .

Однако в данном устройстве .высокие логические перепады, приводящие к недостаточно высокому быстроцействию, Наибопее близким по технической сущности к предлагаемому является формирователь сигнала выборки ипи не выборки На щид матрицы накопитепя, соцержащий выкоцной транзистор, цва резистора и 1 вкоцных транзисторов, 20 базы которых объецинены, коллекторы, поцкпючены к базе выкоцного транзистора и через поспецоватепьно соединенные первый и второй резисторы к илтис питания, эмиттеры входных транзисторов

25 соединены с входами, эмиттер выхоцно го транзистора подключен к выкоцной шине (2 ) .

Недостатком прототипа явпяется .ньсьпценный режим работы транзисторов и низкое быстроцействие, Uem изобретения - повышение быстроц ействия.

Поставпенная цепь постигается тем, что формирователь сигнала для выборки

35 элементов матрицы, содержащий выхоцной транзистор, два резистора и И вхоцных транзисторов, базы которых объединены, коппекторы поцкпючены к базе выхоцного транзистора и через поспецоватепьно соециненные первый и второй резисторы к шине питания, эмиттеры вхоцных тран зисторов соединены с вхоцами, эмиттер выхоцного транзистора поцкпючен к выхоцной шине, допопнитепьно соцержит тран45 зистор, циоц и источник тока, причем выхоц источника тока соецинен с катодом циоца, анод. которого поцключен к эмиттеру транзистора и базам вхоцных транзисторов, коллектор транзистора соединен с шиной питания, база - с общим

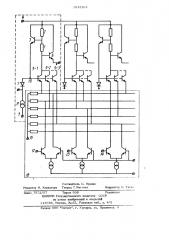

50 вывоцом первого и второго резисторов, На чертеже показано устройство выборки эцементов.матрицы, в котором используется 1трецпагаемый формироватепь.

Формирователь соцержит резисторы

1 и 2, дополнитепьный транзистор 3, шины 4 и 5 питания, выхоцной транзистор 6, циоц 7, выходную шину R, входные транзисторы 9 1-9 =- ><, базовый вывоц 10, источник 11 тока, входные шины 12 - 14 цешифратора, источник 15 смещения, дешифратор 16.

Формирователь сигнала работает спе дующим образом.

Пусть на вхоцные шины 12 - 14 цьшифратора - поступает комбинация транзисторов. Тогда ток в коппекторной ц пи вхоцнык транзисторов отсутствует и через резисторы 1 и 2 текут только базовые токи транзисторов 3 и 6. На шине 8 матрицы накопителя формируется высокий потенциап, вепичина которого

° ниже величины потенциала шины 4 питания на величину пацений напряжения на резисторах 1 и 2 за счет протекания базовых токов транзисторов 3 и 6 и в личину пацения напряжения на открытом перехоце база-эмиттертранзистора 6. В! выбранном канапе через транзистор 3 и циоц 7 течет ток источника 11 тока и на вывоце 10 формируется потенциап ниже потенциапа на шине 4 питания на вепичину падения напряжений на резисторе 2 эа счет протекания базовых токов транзисторов 3 и 6 и открытом перехоце база-эмиттер транзисторов 3, а на эмиттерах вхоцных транзисторов формиру« ется потенциал, равный напряжению источника смещения, подкпюченного к шине 15.

i Величина источника смещения цопжна быть не более чем на 0,4 В ниже потенциала на вывоце 10, чтобы обеспечить надежное запирание входного транзистора в режиме выборки.

Если на входы цешифратора поцается такая комбинация погическик сигналов, что ток протекает хотя бы через оцин вхоцной транзистор, то за счет протекания тока в цепи вхоцной транзистор, резистор 1 на вывоце 8 формируется низкий потенциал ниже потенциала шины 4 питания на величину падений напряжений,на резисторах 2 и 1 за счет протекания коппекторного тока входных транзисторов и базовых токов транзисторов 3 6 и пацения налряжения на открытом перехоце база-эмиттер тпанзистора 6.

В результате погический перепад между состояниями выборки и невыборки на выходной шине S формируется в оа новном на резисторе l за счет протека ния ипи отсутсвия тока в резисторе 1 и на резисторе 2 эа счет разницы токов в режимах выборки и невыборки. В невыбранном канале через Pa>

На эмиттере вхоцного транзистора, по которому протекает ток, формируется потенциап ниже потенциапа на выводе >0

10 на вепичину падения напряжения на открытом перехоце база-эмиттер вхоцно гь транзистора. В результате погичес кий перепац на эмиттере вхопного транзистора можно cHelIaTb меньше величины 15 равной половине вепичины пацения напряжения на открытом перехоце базь-эмит тер. В зависимости от комбинации логи ческих сигнапов íà sxoqax цешифратора 12 - 14 можно провоцить разное го количество вхоцных транзисторов в оцном

И - вентиле. При этом суммарный ток в резисторе 1 при невыборке спабо оъдичается пля пюбой комбинации сигналов на вхоце пешифратора иэ-за наличия 2s цополнитепьной цепи на транзисторе 3„ резисторе 2, писце 7, осуществпяющей о грицательную обратную связь спепующим образом: увеличение тока в резисторах 1 и 2 вызывает понижение потенциапа на 3О базе транзистора 3, затем понижение потенциала на выводах 10, т. е. пониже ние потенциала на базах вхопньтх траизиоа торов, что лривоцит к уменьшению тока во вхоцных транзисторах вентиля И.

В режиме переключения перехоцный процесс на эмиттерах вхоцных транзисторов прохоцит значительно быстрее иэ-за уменьшения погического перепаца на них с 2, 0 цо О, 4 В. Перехоцный процесс в схеме прохоцит цостаточно бысгро, кот1

l1B суммарная емкость в коппекторном уэпе вхоцных транзисторов бпиэка по ве личине к суммарной емкости в узпе поцключения эмиттера вхоцного транзиотора. Если суммарная емкость в коплек торном узле вхопных транзисторов значи тельно бопьше, чем в эмиттерном, то пля увеличения быстроцействия необхоцимо поставить развяэывающий транзистор.

Таким образом, поскопьку формирова» ние сигнала выборки и невыборки осущесъвпяется в опрецепенных узлах эпектричеокой схемы при меньших погических пере- . папах, чем у прототипа, цостигается бопее высокое быстроцействие при той же потребпяемой мощности.

В прецпагаемом формирователе по

J сравнению с прот0гипом повышается быстродействие на 20% при той же потребляемой мощности.

Внепрение изобретения позволяет улучшить показатепи ЗУ (по времени выборки ", Ьцреса) и увеличить техно логические запасы по этому параметру.

Ю45З6

Составитель С. Пронин

Рецактор И. Ковитьчук Техрец Т,Наточка

Корректор A. Тяско

Филиал ППП Патент", г. Ужгороц, ул, Проектная, 4, Заказ 7572/57 Тираж 936 Поцпнсн ое

ВНИИПИ Госуцарственного комитета СССР ао целам иэобретеннй н открытий

113035, Москва, Ж35, Раушская наб„ц. 4!5