Пороговый элемент

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ .РЕСПУБЛИН (5 ) - Н 03 К 19/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ . .Ф. ° И. %1 л, ° .: - 4И. ; м .ы

q °, IЙю,:. Г" ф

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Хр

4г

Рив (21) 3251380/18 21 (22) 23.02. 81 (46) 07.10.83. Бюл. Р 37 (72) О. Н. Муэыченко (53) 681.325.655(088.8) (56) 1. Авторское свидетельство СССР

9 683025, кл. Н 03 К 19/42, 17.07.73.

2. Авторское свидетельство СССР

9 771876, кл. H 03 K 19/42, 30.10.78. (54)(57) ПОРОГОВЫЯ ЭЛЕМЕНТ, содержащий преббраэователь весов входов, соединенный выходами с входами блока формирования порога, о т л и ч а„„SU„„1046932 А ю шийся тем что с целью рас. ширения функциональных воэможностей и упрощения, в него введены коммутатор и г регистров памяти, причем информационные выходы коммутатора соединены с,входами преобразователя весов входов, подключенного выходами к входам регистров памяти, при этом выходы регистров памяти соединены с дополнительными входами блока формирования порога, а их входырарешения записи — с соответствующими выходами коммутатора.

Р Ъ

CO

4ь

Cb с©

СЮ

1046932

50

55 б0

Изобретение относится к автоматике и вычислительной технике и может быть испоИьэованЬ для построения различных устройств обработки дискретной информаций.

Известен мажоритарный логический элемент, содержащий преобразователи весов на два входа, состоящие из элемента И и элемента ИЛИ с параллельно соединенными входами, блок формирования порога и выходной элемент ИЛИ (1 3;

Наиболее близким по технической сущности к предлагаемому является мажоритарный логический элемент, содержащий два преобразователя весов входов, соединенных с входами блока формирования порога (2 ).

Недостатками известных устройств являются низкие функциональные возможности и сложность технической реализации.

Цель изобретения — расширение функциональных возможностей и упрощение устройства.

Для достижения поставленной цели в пороговый элемент, содержащий преобразователь весов входов, соединенный выходами с входами блока формирования порога, введены коммутатор и . регистров памяти, причем информационные выходы коммутатора соединены с входами преобразователя весов входов, подключенного выходами к входам регистров памяти, при этом выходы регистров памяти соединены с дополнительными входами блока формирования порога, а их входы разрешения записи — с соответствующими выходами коммутатора.

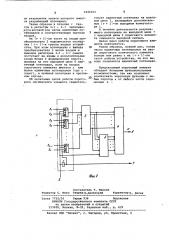

На фиг. 1 изображена структурная схема предлагаемого пороГового элемента для общего случая; на фиг.2 то же, для случая г = 1.

Пороговый элемент (фиг. 1) состоит из коммутатора 1, преобразователя 2 весов j n/(-+ 1) (входов, регистров 3-1 - 3- памяти и блока 4 формирования порога. Информационные выходы (их число равно.3 п/(1- + 1.)() коммутатора 1 соединены с входами преобразователя 2 весов входов. Преобразователь 2 весов входов соеди- j нен выходами с входами блока 4 формирования порога и входами регистров 3-1 — 3- памяти.

Выходы регистров 3-1 -3- памяти соединены с дополнительными входами блока 4 формирования порога, а входы разрешения записи — с выходами коммутатора 1.

На вход 5 устройства подаются тактовые импульсы, а выход блока 4 формирования порога .подключен к выходной шине б. Выходная шина 7 является дополнительным выходом коммутатора 1.

Блок 4 формирования порога может быть выполнен в виде группы элементов И, соединенных выходами с входами элемента ИЛИ, а входами — с выходами преобразователя ? весов входов и регистров 3-1 †. 3- r памяти, образуя все неповторяющиеся комбинации весов их выходов, сумма которых равна порогу, Выходы преобразователя 2 весов входов и регистров

3-1 — 3- памяти с весом, равным порогу (для случаев, когда порог . а 4 3о/(r + 1.) ), соединены с входами элемента ИЛИ.

Преобразователь 2 весов входов

15 является многопороговым логическим элементом на grI /(r + 1)(входов, имеющим выходы с весами от „„„.„= 1 при a<)nr /(r + 1) Г и W, „= s.— gnr /

/(r + 1)(при à))nr /(r + 1)f до 0 W o = 8 при аХ)n/(+ 1)(и W „=

"3 п /(ã + 1)(при а )) /(r + 1)(Регистр 3-i (i = 1, 2, ..., г ) памяти имеет,,-W „. + 1 разрядов при W „ не превйшающем числа вхоg5 дов в соответствующей данному регист ру группе входов и W „- W „ разрядов в противном случае. Все входы устройства разделены на r +1 групп,. причем j(r + 1)) n /(+ 1) (— и ) групп имеют 3 /(- + 1) t -1 входо

З0 а остальные группы — j h/(г + 1) ( входов. При подаче разрешающего потенциала на вход разрешения записи регистра 3-i памяти в него записывается код, поступающий в этот момент

З5 на информационные входы. код на выходах регистра 3-i памяти сохраняется до поступления очередного сигнала разрешения записи.

Пороговый элемент функционирует

40 следующим образом.

В исходном состояния во все регистры 3-1 — 3- г памяти записаны нулевые коды.

На вход 5 устройства подаются тактовые импульсы. При этом коммутатор 1 начинает последовательно подключать группы входов к выходам, соединенным с входами преобразователя 2 весов входов. Одновременно с подключением i-й группы входов на выходе коммутатора, соединенном с входом разрешения записи i-го регистра, 3-i памяти (i = 1, 2, г ), появляется разрешающий потенциал. При подключении на входы преобразователя 2 весов входов i-й группы входов устройства на его выходах формируется весовой код, единица на выходе с весом, которого означает, что на входах преобразователя 2 не менее W единичных потенциалов. Весовой код с выходов преобразователя 2 йоступает на входы регистров 3-1 — 3-t памяти и

I записывается в регистр 3-i на вхо1046932

Составитель Н. Маркин

Редактор С. Юско Техред В.Далекорей КоРРектоР О, Билак

Заказ 7752/56 Тираж 936 Подписное

Вниипи Государственного комитета СССР по делам изобретений и открытий

113035, Москва, М-35, Раушская наб., д. 4/5

Филиал IIIIII "Патент", r. ужгород, ул. Проектная, 4 де разрешения записи которого имеется раэрейающий потенциал.

Таким образом в течение r тактов в регистры 3-1 - 3- г записыва,ется весовой код числа единичных потеицйалов в соответствуюших группах входов.

На tr + 1)-ом такте на входы преобразователя 2 подключается последняя (r + 1)-я группа входов устройства. При этом потенциалы с выхода преобразователя 2 весов входов и выходов регистров 3-1 - 3--r памяти поступают на входы и дополнительные входы блока 4 формирования порога, выэывая на его выходной шине б .единичный потенциал, если на входах порогового элемента имеется а или более единичных потенциалов (где 8, порог), и нулевой потенциал в противном случае.

Об окончании цикла работы порогового логического элемента свидетель-! ствует единичный потенциал на выходной шине 7, являющийся дополнительным (I + 1)-ом выходном коммутаторе 1, В течение длительности.разреша5 кицего потенциала на выходной шине 7 с выходной шины б порогового элемента снимается выходной сигнал. далее цикл работы порогового эле" мента повторяется.

)О Таким образом, всякий Раз, когда число единичных потенциалов на входе порогового логического элемента больше или равно а íà (I + 1)-ом такте. работы устройства íà его выходе появляется единичный потенциал.

Предлагаемый пороговый элемент обладает бсльшими функциональными воэможностями, так как позволяет, реализовать пороговую функцию с любым порогом в от любого числа переменных