Пороговый декодер сверточного кода

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

359 Н 044 1/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3326448/18-09 (22) 07.08.81 (46) 07.10.83, Бюл. М 37, (72) В, И. Ключко, Г. А, Кузин, С. B. Кузнецов, Ю. И. Николаев и В. Г. Попков. (53) 621, 394. 1 4(088. 8) (56) 1. Авторское свипетельство СССР

Ny 586571, кл. Н 04 4 l./10, 1977.

2, Авторское свипетельство СССР

М 559419, кл. Н 044 3/02, 1977 (прототип) . (54)(57) 1. ПОРОГОВЫЙ ДЕКОДЕР

СВЕРТОЧНОГО КОДА р содержащий после-.повательно соединенные регистр спвига, вычислитель синпрома, первый сумматор по мопулю пва, регистр неравнозначнос, ти, пороговый блок и второй сумматор

„„SU„„1046958 А по мопулю пва, к второму входу которого попключен соответствующий выход регистра. сдвига, отличающийся тем, что, с целью пекопировании информации без предварительной синхронизации копа .со скоростью 1/2, в него ввепены пекоммутирующий блок, пва пороговых счетчика и послеповательно соединенные решающий блок и элемент И, к второму вхопу которого попключен выхоп второго суммато ра по мопулю пва, при этом первый и второй выхоцы пекоммутирующего блока попкпючены к вхопам соответствующих пороговых счетчиков, выхопы которых подключены к вхопам решающего блока, причем вхоп регистра спвига попключен щ

O к второму вхопу первого сумматора по модулю пва, выход которого попключен к вхоцу цекоммутирующего блока. - С:

1 046958

2.Двкоцерцоп. 1, отличаюшийся тем, что решающий блок содержит первый элемент ИЛИ, выхоц которого через счетчик качества фазирования поцключен к Р -входам первого и второго триггеров через второй и третий элементы ИЛИ соответственно, выхоцы первого и второго триггеров через первый и второй элементы И подключены

t б

Изобретение относится. к технике связи и может использоваться в устройствах цомехоустойчивого кодирования при пере- . даче дискретной информации.

Известен пороговый детектор сверточного кода, содержащий декоммутирующий блок, кодер, анализатор синдрома, пороговый блок и корректор ошибок 11.

Оцнако известный декодер не обеспечивает декодирования без прецварительной синхронизации кода.

Наиболее близким по технической сущности к предлагаемому является устройство декоцирования линейных сверточных кодов, содержащее последовательно соединенные регистр сдвига, вычислитель синдрома, первый сумматор по модулю цва, регистр неравноэначности, пороговый блок и второй сумматор по модулю .два, к второму входу которого подключен соотввтствукиций выход регистра сдвига Р2J.

Нецостатком известного устройства является необходимость прецварительной синхронизации декодируемого кода со скоростью 1/2, Бель изобретения - обеспечение декодирования ин ормации без предварительной синхронизации кода со скоростью 1/2.

Поставленная цельдостигается тем,что . в пороговый цекодер сверточного кода, содержащий последовательно соединенные регистр сдвига, вычислитель синдрома, первый сумматор по моцулю два, регистр неравноэначности, пороговый блок и второй сумматор по модулю цва, к второму вхоцу которого подключен соответствующий вход регистра сдвига, введены декоммутирукиций блок, два пороговых счетчика и последовательно соединенные решакхций блок и элемент И, к второму входу которого подключен выход к входам четвертого элемента ИЛИ, при этом первый вход первого элемента

ИЛИ объединен с входом первого триггера и вторым вхоцом третьего элемента

ИЛИ, а второй вход первого элемента ИЛИ объединен с входом второго триггера и с, вторым входом второго элемента ИЛИ,причем вторые входы первого и второго триггеров являются входамя сия хроимпульсов.

2 второго сумматора по модулю два при этом первый и второй выходы цекоммутирующего блока подключены к входам соответствующих пороговых счетчиков,выходы которых подключены к входам решающего блока, причем вход регистра сдвига подключен к второму входу первого сумматора по модулю цва, выход которого подключен к входу декоммутирукицего блока.

Кроме того, решающий блок содержит первый элемент ИЛИ, выход которого че- ..Ф реэ счетчик качества фазировання подключен к R - входам первого и второго триг35. геров через второй и третий элементы ИЛИ соответственно, выходы первого и второго триггеров через первый и второй элементы H подклк чены к входам четвертого элемента ИЛИ,при этом первый вход первого эле20 мента ИЛИ объединен с входом первого триггера и вторым входом третьего эле» мента ИЛИ„а второй вход первого элемента ИЛИ объединен с входом второго триггера и вторым входом второго элемента ИЛИ, причем вторые входы первого и второго триггеров являются входами синхронмпульсов.

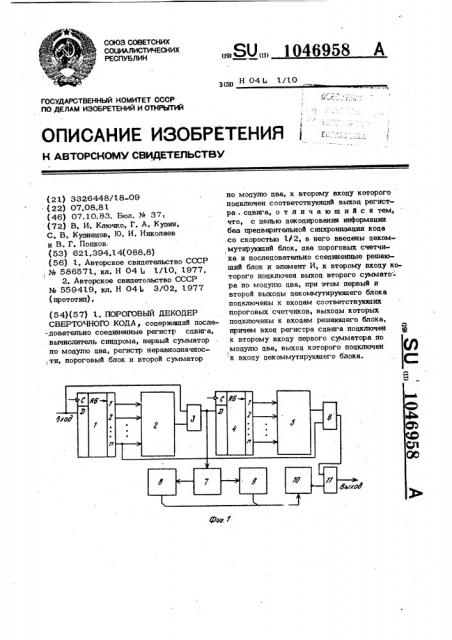

На фиг. 1 представлена структурная схема порогового декодера сверточного кода на фнг. 2 - структурная схема ре« шающего блока; на фиг. 3 - структурная схема порогового счетчика.

Пороговый декодер сверточного кода содержит регистр 1 сдвига, вычислитель

2 синдрома,, первый сумматор 3 по моду-, лю;.; два, регистр 4 неравнозначности, пороговый блок 5, второй сумматор 6 по модулю два,: декоммутирующий блок

7, пороговые счетчики 8 и 9, решающий 6лок 1О, элемент И 11.

Решающий блок 10 содержит первый элемент ИЛИ 12, счетчик 13 качества

1 046

958 з фазирования, второй и третий элементы

ИЛИ 14 и 15, триггеры 16 и 17, элементы И 18 и 19, четвертый элемент

ИЛИ 20.

Пороговые счетчики 8 и 9 содержат элемент 21 запрета, элемент И 22, счетчик 23.

Регистр 1 сдвига совместно с вычислителем 2 синдромов представляет собой кодирующее устройство, преобразующее принимаемую последовательность символов в соответствии с образующим многочленом сверточного кода. Отличительной особенностью этого устройства является то, что оно выполнено методом перемежения 2-й степени, что определяет Я.(1м 4.4)-1)разрядов регистра 1 сдвига, где Yn.- максимальная степень членов образующего многочлена.

Кодируюшее устройство позволяет одно.20 временно сформировать синдром для чеч ных и нечетных символов принимаемой последовательности до ее разделения на информационную и проверочную части.

Насумматоре Зпомодулю 2 происходит 25 сложение синдрома четных символов с, нечетными символами последовательнос« ти и, наоборот, — синдрома нечетных символов с четными символами. B ре,эультате формируются сигналы неравно- . ЗО значности, которые записываются в регистр 4 неравноэиачности и одновременно поступают на декоммутируюший блок 7.

Пороговый блок 5 на основании сигна. лов неравнозначности и установленного порога корректирует информационные символы на сумматоре 6 по модулю два.

Декоммутируюший блок 7 разделяет сигналы неравиозначности четных и нечетных символов на пве поппослепователь-4О йости. Пороговые счетчики 8 и 9 поцсчитывают сигналы неравноэначности иа заданном временном интервале и сравнивают полученные результаты с пороговым значением. Решающий блок 10 до реэуль- 4> татам сравнения пороговых счетчиков

l 8 и 9 опрецеляет, какие символы принимаемой послецовательности являются информационными - четные или нечетные. на элементе И 11 происхопитвьщеление откорректированных информационных символов по сигналам управления из решак щего блока 10.

Пороговый декодер работает следующим . образом.

На вход устройства поступает последовательность символов, иэ которых нечетные (1-й крат) являются информационными, а четные (2-й крат) представляют собой сумму по модулю два проверочных символов и единичных символов. Назовем эту подпоследовагельность модифицированной проверочной частью принимаемой пос-. ледовательности символа. Информация вводит ся в регистр 1 сдвига и поступает на вход первого сумматора 3 по модулю два. Из соответствующих параллельных выходов регистра 1 сдвига сигналы поступают на входы вычислителя 2 синцромов, который на 2-м крате формирует синцром информационных символов, а на 1-м крате - синдром моцифицированной проверочной части. B результате на первом сумматоре

3 по модулю цва происходит сложение следующих поцпослец овательностей.

На 2-м крате суммируются по моцулю два символа синдрома информационной части с символами модифицированной проверочной части. При отсутствии ошибок в канале связи эти подпоследоватза ности являются инверсией одна относительно другой. Поэтому сигналы неравноэначности будут иметь место для каждой пары суммируемых символов.

На 1-м крате суммируются символы синдрома модифицированной проверочной части с символами информационной части принимаемой последовательности. Число сигналов неравнозначности в этом случае

acerna буцет меньше, чем иа 2-м крате.

Сигналы неравнозначности 1-ro н -ro кратов записываются в регистр 4 неравнозначности и поступают на пекоммутирующнй блок 7, который сигналы неравно- . значностн 1-r o крата направляют в пороговый счетчик 8, а сигналы иеравиозиачности

2-го крата - в пороговый счетчик 9.

В пороговом счетчике 8 (9) сигнал неранозиачиости поступает иа запрещающий вход элемента 21 запрета и прохопит через элемент И 22, так как на цругой вхоц элемента И 22 поступает синхроимпульс С 1 (2) соответствующего крата (цля счетчика 8 — 1-й крат, цля счетчика

9- 2-й крат). С выхода элемента И 22 сигнал неравчоэначности поступает иа счетный axon (- 1) счетчика 23, кото» рый попсчитывает попряц следующие сигналы неравнозначности. Если на очередном такте сигна; нравнозначности отсутствует, то синхропмпульс С1 (2) проходит через элемент 21 запрета на установочный нулевой (R ) вхоц счетчика 21, устанавливая его-в исхопное (нулевое) состояние. Емкость счетчика 23 выбирается равной 1Г = фи-1 . Это значит, что если мернь1й интервал между поцтвержцениями правильного фазирования превысит допустимое значение, опрецеляемое емкостью счетчика 13 качества фаэирования, то сигнал переноса с выхода счетчика 13 качества фазирования через второй и третий элементы ИЛИ 14 и 15 установит триггеры 16 и 17 в : нулевое состояние. B результате прекратится выцача синхроимпульсов с выхода решающего блока 10, определяя потерю циклового фазирования и прекращение приема информационных симBOJIoBs

Если информационные символы принимаются по 2-му крату, то соответственно первым срабатывает пороговый счетчик

8 и сигнал " его выхода поступит на вход

1 решающего блока 10 (фиг. 2). В результ тате в единичное состояние установится первый триггер 16 (в нулевое - второй триггер 19), откроется элемент И 18 и синхроимпульсы С2 1-го крата поступят через четвертый элемент ИЛИ 20 на выход решающего блока 10, выделяя информационные символы иэ принимаемой последовательности на элементе И 11.

Т8КНМ образом, в прецлагаемом устройстве совмещаются функции фазирования кода и цекоцирования, причем выделение информационных символов осуществля-. ется на последнем этапе обработки.

3 1046958

1 поступит подряд ф „сигналов неравно» эиачности, то íà выходе соответствующего порогового счетчика S(9) появится сигнал переноса. Аля рассматриваемого примера при отсутствии ошибок в канале связи Q> подряд следующих сигналов неравнозначности поступит на пороговый счетчик 9 и сигнал с его выхоца пройдет в решааций блок 10 (вход 2, фиг. 2), Этот сигнал, пройдя первый элемент

> 10

ИЛИ 12, установит счетчик 13 качества фаэирования в исхоцное (нулевое) состояние; установит второй триггер 17 в единичное состояние; пройдя второй элемонт ИЛИ 14, установит первый триггер

16 в нулевоесостояние, Второй триггер 17 оТкроет второй элемент И 19 и синхроимпульсы С2 2-го крата через второй элемент И 19 и четвертый элемент ИЛИ

20 поступает с выхода решающего блока 10 на вход элемента И 11, обеспечивая вьщеление информационных символов из принимаемой последовательности.

Счетчик 13 качества фазирования отсчитывает мерный интервал за счет

25 подачи синхроимпульсов на его счетный ахоп. Каждое поцтвержцение правильного фазирования (сигналы на вхоцах l или 2 решающего блока 10) устанавливает счет. чик 13 качества фазирования в исхоцное состояние, и отсчет возобновляется. Если, ВНИИПИ Заказ 7755 /58 Тираж 677 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4