Устройство для обнаружения ошибок в регистре сдвига

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) зсю С 06 F 11 08

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

По ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Я; (;Г; 1 у:. р,, „;-, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3457381/18-24 (22) 28.06.82 (46 ), 15. 10. 83. Бюл . и 38 (72) М,Н . Голованов, В.P. Дума, Г.Л. Левин и Ю.Н. Родин ,(53) 681.3 (088.8) (56) 1, Авторское свидетельство СССР и 710043, кл . G 06 F 11/08, 1978.

2; Авторское свидетельство СССР N 809118, .кл. G 06 F 11/08, 1979 .(прототип). (54)(57) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ

ОШИБОК В РЕГИСТРЕ СДВИГА, содержащее два блока определения четности, Ф

=элемент И, формирователь импульсов, причем разрядные выходы регистра сдвига соединены с входами первого блока определения четности, выход которого соединен с первым входом элемента И, выход которого соединен с входом формирователя. импульса, выход которого я.вляется выходом сигнала ошибки устройства, выход старшего разряда регистра сдвига является выходом последовательного кода устройства, тактовый вход ,регистра сдвига соединен с входом тактовых импульсов устройства, информационные входы всех разрядов регистра сдвига, кроме старшего, соединены с входами второго блока определения четности и образуют информационный вход устройства, вход строба записи устройства соединен с входом записи регистра сдвига, о т л и ч а ю щ е е. с я тем, что, с целью упрощения устройства, оно содержи-г элемент ИЛИ и коммутатор, причем второй вход элемента И соединен с выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с входами строба записи и тактовых, импульсов устройства, выходы второго блока определения четности соединены с соответствующими информационными входами коммутатора, выход которого соединен с информационным входом старшего разряда регистра, управляющий вход коммутатора соединен с входом контроля устройства, выход последо вательного кода устройства соединен с последовательным входом регистра сдвига.

1048477

Изобретение относится к импульсной технике, в частности к передаче дискретных сигналов, и может быть использовано в цифровых вычислительных системах, например в системе внутриреакторного контроля, управления и локальной защиты ядерных реакторов °

Современные системы контроля и управления характеризуются большим количеством информации, которая передается между входящими в их состав подсистемами. В частности, система внутриреакторного контроля, управления и локальной защиты ядерного реактора осуществляет сбор и обработку порядка 1000 параметров, характеризующих состояние активной зоны и первого контура реактора.

Повышение требования по надежности и быстродействию системы привели к гому, что в ее составе насчитывается около á0 каналов передачи данных в последовательном коде, пл которым информация передается между отдельными устройствами системы с общим объемом передаваемой информации около 4 .10 бит в секун4 ду. В результате, накладываются жесткие требования к надежности передачи информации, поскольку возникшая при передаче ошибка может привести к выдаче неправильного управляю щего сигнала, либо к пропуску аварийной ситуации.

Известно устройство для обнаружения ошибок в регистре сдвига, содержащее сдвиговый регистр, два сумматора по модулю два,. блок. определения четности, элемент И, триггер, элемент запрета и формирователь сигнала ошибки. Устройство осуществляет контроль правильности работы сдвигового регистра путем сравнения по четности содержимого триггера, в который заносится результат сложения по модулю два сигнала на входе и выходе регистра, с результатом сложения по модулю два содержимого сдвигового регистра. По несовпадении этих двух сигналов на выходе устройства вырабатывается сигнал ошибf0

50 ки (1) Недостатками устройства являются его сложность; а следовательно, низкая надежность, а также отсутствие возможности контроля занесения параллельного кода в сдвиговый

45 регистр для последующей его передачи

s последовательный канал.

Наиболее близким по технической сущности к предлагаемому является устройство для обнаружения ошибки в регистре сдвига, содержащее сдвиговый регистр, два сумматора по модулю, элемент запрета, формирователь сигнала ошибки, основной определитель четкости, триггер, дополнительный определитель четности и элемент"

И. Сдвиговый регистр, основной определитель четности, первый сумматор по модулю, элемент И и формирователь сигнала ошибки последовательно соединены между собой . Входные шины параллельного приема информации соединены с входом сдвигового регистра и второго определителя четности, выход которого через элемент И, управляемый от шины параллельной записи, соединен с входом триггера„ выход которого соединен с входом первого сумматора по модулю. Контроль правильности выдачи последовательного кода осуществляется путем сравнения содержимого сдвигового регистра с содержимым триггера, в котором в зависимости от режима работы устройства хранится либо значение контрольного разряда, либо ожидаемое значение четности содержимого сдвигового регистра, на следующем шаге сдвига . Сравнение проводится на первом сумматоре по модулю два, на выходе которого при исследовании- сигнала с выхода основного определителя четности и триггера появляется сигнал, разрешающий прохожедние импульсэв через элемент запрета на вход формирователя сигнала ошибки )2)

Недостатками устройства являются

его сложность и невозможность проверки цепей контроля устройства в процессе его работы, что снижает надежность -устройства в целом.

Цель изобретения - упрощение устройства.

Поставленная цепь, достигается тем, что устройство для обнаружения ошибок в регистре сдвига, содержащее два блока определения четности, элемент И, формирователь импульса, причем разрядные выходы регистра сдвига соединены с входами первого блока определения четности, выход которого соединен с первым

3 10 входом элемента И, выход которого соединен с входом формирователя импульса, выход которого является выходом сигнала ошибки устройства, выход старшего разряда регистра сдвига является выходом последовательного кода устройства, тактовый вход регистра сдвига соединен со входом тактовых импульсов устройства, информационные входы вгех разрядов регистра сдвига, кроме старшего, соединены с входами второго блока определения четности и образуют информационный вход устройства,. вход строба записи устройства соединен со входом записи регистра сдвига, содержит элемент ИЛИ и коммутатор, причем второй вход элемента И соединен с .выходом элемента

ИЛИ, первый и второй входы которого соединены соответственно с входами строба записи и тактовых импульсов устройства, выход второго блока определения четности соединены с соответствующими информационными входами коммутатора, выход которого соединен с информационным входом старшего разряда регистра сдвига, управляющий вход коммутатора соединен с входом контроля устройства, выход последовательного кода устройства соединен с последовательным входом регистра сдвига.

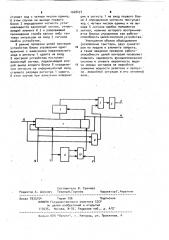

На чертеже приведена структурная схема устройства для обнаружения ошибок в регистре сдвига.

Устройство содержит последовательно соединенные регистр 1 сдвига, первый блок 2 определения четности, элемент И 3 и формирователь 4 импульса, выхсд которого является выходом сигнала ошибки устройства, информационные входы регистра 1 сдвига соединены с входами второго блока

6 определения четности и с информационным входом 7 устройства, вход записи регистра 1 гдвига — с первым входом элемента ИЛИ 8, с первым входом дополнительного разряда 9 сдвиговсго регистра и входом 10 строба записи устройства, последовательный вход регистра 1 сдвига старшего разряда сдвигового регистра 1 сдвига и является выходом 11 последова" тельного кода устройства, а тактовый вход регистра.1 сдвига соединен с вторым входом элемента ИЛИ 8 и является входом 12 тактсвь.х импульсов

48477

55 устройства. Выход элемента ИЛИ 8 соединен со вторым входом элемента

И 3, первый и второй выходы второго блока 6 определения четности соединены с соответствующими информационными входами коммутатора 13, выход которого соединен с информационным входом старшего разряда регистра 1 сдвига, а управляющий вход - с входом 9 контроля устройства.

Устройство работает следующим образом.

По импульсу, поступающему по входу

10 строба записи устройства, информаI ция в параллельном коде с информационногс вхсда 7 заносится в регистр

1 сдвига. Кроме того, информация поступает на вход второго блока 6 определения четности, на первом и втором выходах которого появляется соответствующий сигнал дополнения до нечетности и четности, заносимый в старший разряд регистра 1 сдвига одновременно с информацией. При нулевом сигнале на входе 9 контроля, в старший разряд регистра 1 сдвига через коммутатор 13 заносится информация с первого выхода второго блока 6 определения четности, дополняющий информацию -в регистре

1 до нечетного числа единиц, При отсутствии ошибок занесения инфсрмации на вход первого блока 2 определения четности поступает с нечетным числом единиц так, что на его выходе устанавливается нулевой сигнал, запрещающий прохождение строба записи через элемент И 3 на выход 5 сигнала ошибки. При отсутствии сигнала ошибки из блока управления (не показан) начинают поступать сигналы на вход 12 тактовых импульсов, по которым содержимое регистра 1 сдвига вместе с содержимым старшего разряда поступает на выход 11 устройства и на последовательный вход регистра-1. При правильной работе устройства в режиме выдачи последовательного кода четность содержимого сдвигового регистра 1 сдвига не изменяется и на вь.ходе первого блока 2 определения четности останется нулевой потенциал, запирающий элемент И 3.

При неправильном занесении параллельного кода либо сшибке в режиме выдачи последовательного кода на вход первого блока 2 определения четности с выходов регистра 1 по1

Составитель В. Гречнев

Редактор А . Долинич ТехредМ.Гергель Корректор Г. Реаетник

Заказ 7933/54 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5 филиал ППП "Патент, r. Ужгород, ул . Проектная, .4

5 104 ступает код с четным числом единиц.

В этом случае на выходе первого блока 2 определения четности устанавливается единичный сигнал, откры-, вающий элемент И 3 и разрешающий прохождение строба записи либо тактовых импульсов на вход 5 сигнала ошибки устройства.

В режиме проверки цепей контроля устройства блока управления одно. временно с занесением параллельного кода в регистр 1 сдвига на вход контроля устройства поступает единичный сигнал, подключающий второй выход второго блока б определе- ния четности на информационный вход стар оего разряда регистра 1 сдвига.

В этом случае при занесении информа8477. б ции в регистр 1 на вход первого блока 2 определения четности поступает код с четным числом единиц и на выходе 5 сигнала ошибки появляется

5 сигнал, наличие которого воспринимается блоком управления как работоспособность цепей контроля устройства.

Уменьшения объема оборудования (исключение триггера, двух суммато10 ров по модулю и. элемента запрета, а также введение проверки работоспособности цепей контроля позволяет повысить надежность функционирования системы и снизить вероятность выда15 чи ложных сигналов на аварийное снижение мощности реактора и пропус- " ка... аварийной ситуации в его активной . зоне.