Устройство преобразования цифрового сигнала

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ цифрового СИГНАЛА, содержащее входной элемент И, первый вход которого соединен с первым входом устройства, счетный триггер, вход которого сое-, динен с выходом входного элемента . И, второй элемент И, первый вход . которого соединен с выходом счетно-, го триггера, третий элемент И, Первый вход которого соединен с первым, входом устройства, элемент ИЛИ, первый вход которого соединен с выходом третьего элемента И, а выход элемент ИЛИ соединен с выходом устройства, t Г цвдз отличающееся тем, что, с целью повышения помехоустойчивости в него дополнительно введены сдвигающий регистр, первый вход которого соединен с первым входом устройства, второй и третий входы сдвигающего регистра соединены с вторым и третьим входами устройства соответственно, первый выход сдвигающего регистра соединен с вторым входом входного элемента И, второй выход сдвигающего регистра соединен с вторым входом второго элЪмента И, входной D-триггер, первый вход которого соединен с третьим входом сдвигающего регистра, второй вход входного D-триггера соединен с вторым выходом сдвигающего регистра, выход входного D-триггера соединен с вторым входом третьего элемента И, выХодной D-триггер первый вход которого соединен с выходом второго элемента И, второй вход выходного D-триггера соединен с третьим входом устройства, выход выходного D-триггера соединён с вторым входом элемента ИЛИ.

СОЮЗ СОВЕТСКИХ

СОЗВЛИР

РЕСПУБЛИК

09) (И) 3(Я) " 03 K 13/24 Н 03 K /20 ...

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA

Н ABTGPCHOMY СВИДЕТЕЛЬСТВУ

".« лба.„

В:. 1" С!Ц ),"... r 1 q

f0

Я

I

/ (211 3439622/18-21 (22) 14. 05.82 (46) 15.10.83. Бюл. Н 38 (72) М.И. Беляков, В.Д. Лиференко) ,И.А. Лукин, Р;В, Марков и В.Т; Хрыкин... (53) 681.325 (088,8) (56) 1. Патент Великобритании

У 2004165 кл. H 03 K 19/30, опублик. 1979. . 2.. Вклад G 70314-Е МККТТ, конференция Д" G ЕОТЕ1-ЕСОМ, февраль 1974-. (прототип). (54)(571 УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ

ЦИФРОВОГО СИГНАЛА, содержащее вход-. ,ной элемент И, первый вход которого соединен с первым входом устройства; счетный триггер, вход которого сое- ..динен с выходом входного элемента

И, второй элемент И, первый вход . которого соединен с выходом счетно-.; го триггера, третий элемент И, первый вход которого соединен с первым входом устройства, элемент ИЛИ, первый вход которого соединен с выходом третьего элемента И, а выход элемента

ИЛИ соединен с выходом устройства, отличающеесятем, что, с целью повышения помехоустойчивости в него дополнительно введены сдвигающий регистр, первый вход которого соединен с первым входом устройства, второй и третий входы сдвигающего регистра соединены с вторым и третьим входами устройства соответственно, первый выход сдвигающего регистра соединен с вторым входом входного элемента И, второй выход сдвигающего регистра соединен с вторым входом второго элемента И, входной D-триггер первый вход которого соединен с третьим входом сдвигающего регистра, второй вход входного D триrгера соединен с вторым выходом сдвигающего регистра, выход входного D-триггера соединен с вторым входом третьего элемента И, выХодной D-триггер первый вход которого соединен с выходом второго элемента И, второй вход выходного Р-триггера соединен с третьим входом устройства, выход выходного D-триггера соединен с вторым входом элемента ИЛИ.

1048575 2 выход сдвигающе го реги стра соединен с вторым входом второго элемента И, входнойП -триггер, первый вход которого соединен с третьим входом сдвигаю5 щего регистра, второй вход входного

D-триггера соединен с вторым выходом сдвигающего регистра, выход входного.11-триггера соединен с вто- рым входом третьего элемента И, выход10 нойс -триггер, первый вход которого соединен с выходом второго элемента

И, второй вход выходногоD -триггера соединен с третьим входом устройства, выход выходного П -триггера coet5 динен с вторым входом элемента ИЛИ.

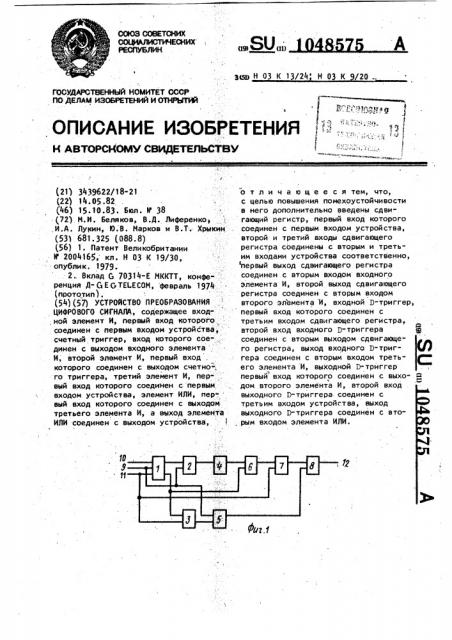

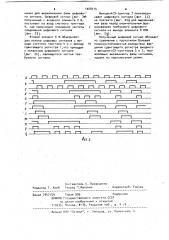

На фиг. 1 изображена функциональная схема устройства, на фиг. 2 временные диаграммы, поясняющие работу устройства.

20 Устройство содержит сдвигающий регистр 1, входной элемент 2 И, входнойЭ -триггер 3, счетный триггер 4, элемент 5 И, элемент 6 И, выходной2 -триггер 7, элемент 8 ИЛИ

25 вход 9 устройства, вход 10 устройства, вход 11 устройства и выход 12. н- Устройство работает следующим образом.

На вход 10 устройства подается

gp информационная последовательность цифровых сигналов (Фиг. 25), поступающая на вход сдвигающего регистра

1. Fla вход 9 устройства подается цифровой сигнал с частотой. следования, равной тактовой частоте

35 (фиг. Za) . На вход 11 устройства подается инверсный цифровой сигнал, равный тактовой частоте (фиг. 2с) .

Изобретение относится к технике связи и может быть использовано как устройство преобразования цифро вого сигнала линейного тракта.

Известно устройство преобразова ния цифрового сигнала, состоящее из трех логических элементов И, моностабильного элемента, D -три ггера, Т-триггера и элемента задержки tlj

Недостатком этого устройства является низкая помехоустойчивость преобразования цифрового сигнала.

Наиболее близким к изобретению по технической сущности является устройство преобразования цифрового сигнала, содержащее входной элемент

И, первый вход которого соединен с первым входом устройства, счетный триггер, вход которого соединен с выходом входного элемента И, второй элемент И, первый вход которого соединен с выходом счетного триггера третий элемент И, первый вход которо го соединен с первым входом устройст ва, элемент ИЛИ, первый вход которого соединен с выходом третьего элеме та И, а выход элемента ИЛИ соединен с выходом устройства (2)

Недостатком устройства является. низкая помехоустойчивость преобразователя цифрового сигнала из-за наличия цепей с различной задержкой прохождения цифрового сигнала.

Цель изобретения - повышение поме хоустойчивости .

Цель достигается тем, что в устройство преобразования цифрового сигнала, содержащее входной элемент

И, первый вход которого соединен с первым входом устройства, счетный триггер, вход которого соединен с виходом входного элемента И, второй элемент И, первый вход которого соединен с выходом счетного тРиггера, 45 третий элемент И, первый вход которого соединен с первым входом устройства, элемент ИЛИ, первый вход которого соединен с выходом третьего элемента И, а выход элемента ИЛИ соединен с выходом устройства, дополнительно введены сдвигающий регистр, первый вход которого соединен с первым входом устройства, второй и третий входы сдвигающего регистра соединены с вторым и третьим входами устройства соответственно, первый выход сдвигающего регистра соединен с вторым входом входного элемента И, второй

На выходах сдвигающего регистра

1 получают цифровой сигнал, соответствующий входному сигналу, сдвинутому .на полутактовый {фиг. 2d) и на тактовый (фиг. 2Ц интервалы. На выходе входного элемента 2 И получаем простробированный тактовой частотой цифровой си гнал (фиг. 2 e), соответ- ствующий сдвинутой на полтакта информационной последовательности входного цифрового сигнала. Такой же цифровой сигнал, соответствующий входной информационной последовательности, но сдвинутый на 1,5 тактовых интервала (фиг. 2р), получается на выходе элемента 5 И благодаря совпадению тактовой частоты (фиг, 2 Q.) и цифрового сигнала (фиг. 2n) с выхода входного ?3-триггера 3. Входной -триггер 3 предназз 1 начен для выравнивания Фазы цифрово- го сигнала. Цифровой сигнал (фиг . 2e) полученный с входного элемента 2 И, поступает на вход счетного триггера

4, где происходит понижение частоты следования цифрового сигнала фиг ..21) .

Второй элемент 6 И объединяет два потока цифровых сигналов с выхода счетного триггера 4 и с выхода сдвигающего регистра 1,что приводит к появлению цифрового сигнала (Фиг. 2L), являющегося частью требуемого сигнала.

048575

Составитель С . Кривуценко

Редактор Т. Колб Техред Т.Иаточка КорректорВ. Гирняк

Заказ 7947/59 Тираж 936: Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж" 35, Раушская наб., д. 4 /5

Филиал ППП Патент", г. Ужгород, ул . Проектная, 4

С

d е

Г

К

P

Выходной Il-триггер 7 производит сдвиг цифрового сигнала (фиг. 2 1.) на контакта (фнг. 2Л1) Ллл выаавннвания фазы перед окончательным формированием требуемого цифрового сигнала на выходе элемента 8 ИЛИ фиг. 2®.

Полученный цифровой сигнал обладает по сравнению с прототипом большей

10 помехоустойчивостью вследствие введения сдвигающего регистра входного и выходного)3 -триггеров 3 и 7, позволяющих выравнивать фазы сигналов, идущих по параллельным цепям.