Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

1. БУФЕРНОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО, содержащее накопитель , входы кот«фого подключены к выходам адресного блока, входы адресного блока яяпяются уяравпякшими входами устройства, о гличаюшееся тем, что, с целью повышения надежности за счет перераспределения данных между информационными каналами, оно содер жит первый и второй счетчики, входы которых подключены к соответствующим входам адресного блока, и первый и второй блоки коммутации , управляющие входы которых подключены к выходам соогветствуюших счетчиков, информационные входы накопителя подключены к выходам первого блока коммутации, информационные входы которого являются информационными входами устройства, выходы накопителя подключены к информационным входам второго блока коммутации; выходы которого являются информационными выходами устройства. 2. Устройство поп. 1, отлнча1бШ е е с я том, что блок коммутации содержит матрицу элементов И,дещифратор и регистр, входы которого являются информационными входами блока коммутации , входы дешифратора являются управляющими входами блока коммутации, первые входы элементов И каждого столбца матрицы объединены и подключены (Л к соответствующему выходу регистра, звторые входы элементов И каждой строс ки матрицы подключены к вторым входам соответствующих элементов И других Строк матрицы и подключены к соответствующим выходам дешифратора, выходы элементов И каждой строки матрицы объеединены и яЕ ;пяются выходами блока комму ;о со .тации. Од 00

С01ОЭ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

PECflYSJlHH

1 ! (1Ю (В

y g 1 Q 11 С 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HOMHTET СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3450218/18-24 (22) 11.06.82 (46) 23.10.83, Бюл. М 39 . (72) B,М,Гриць, В.С.Лупиков, В,С.Масле ников и С.С.Спиваков (53) 681.327.6 (088.8) (56) 1. Авторское свидетельство СССР

Ж 809358, кл, 9 11 С 9/00, 1981.

?. Авторское свидетельство СССР

Ж 822287, кп. Cj 11 С 9/00, 1981. (54)(57) 1 ° БУФЕРНОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО, содержащее накопитель, входы которого подключены к выхо.дам адресного бпока, входы адресного блока являются управляющими входами устройства, о т л и ч а ю ш е е с я тем, что, с целью повышения надежности за счет перераспределения данных между информационными каналами, оно содер жит первый н второй счетчики, входы которых подключены к соответствующим входам адресного блока, и первый и второй бпоки коммутации, управляющие входы которых подключены к выходам соответствуюших счетчиков, информационные входы накопителя подклкнены к выходам первого блока коммутации, информационные входы которого являются информационными входами устройства, выходы накопителя подключены к информационным входам второго блока коммутации, выхо» ды которого являются информационными выходами устройства.

2. Устройство по п.1, о т л и ч а ю ш е е с я тем, что блок коммутации содержит матрицу элементов И,дешифратор и регистр, входы которого являются информационными входами бпока коммутации, входы дешифратора являются управляющими входами блока коммутации, первые Bxollbl элементов И каждого стопб- Pg ца матрицы объединены и подключены к соответствующему выходу регистра, вторые входы элементов И каждой crpo- y ки матрицы подключены к вторым входам соответствующих элементов И других; а строк матрицы и подключены к соответси вуюшим выходам дешифратора, выходы элементов И каждой строки матрицы объе динены и являются выходами бпока комму. тации.

1049968 1 входы аешифрагора являются упреапгггоггпгми входами блока коммутации, первые входы элементов И каждого столбца матрицы объединены и подключены к соог5 вегсгвующему выходу регистра, вторые входы элементов И каждой строки матриlIbl подключены к вторым входам соотвез ствующих элементов И других строк Магриал и подключены к соответствующим

10 выходам аешифра тора, выходы элементов

И каждой матрицы строки матрицы объединены и являются выходами блока коммутации.

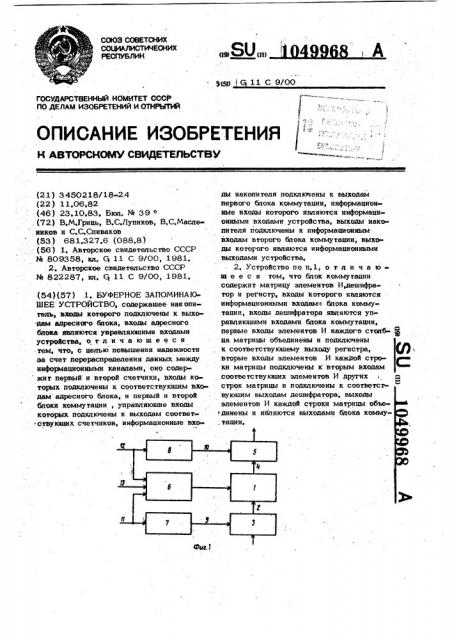

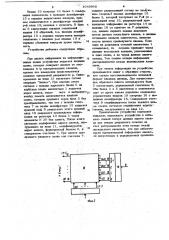

На фиг. 1 показана структурная схема !

5 предлагаемого устройства; на фиг. 2структура блока коммутации, на фиг. 3структура второго бпока коммутации, на фиг, 4 - схема матрицы элементов И, Устройство содержит накопитель l, шим входам БЗУ, а выходы соединены с адресными входами накопителя (2), Однако в известном устройстве отказы разрядных сечений, что является наибоп,ее характерным .отказом при использовании интегральных микросхем памя- 25 ти, приводят к полной потере данных определенного канала измерительной систеЬ», мы, если эти данные хранятся в блоке памяти в упакованном виде, т,е. в одной . ячейке памяти записано несколько слов различных каналов, 11ель изобретения - повышение надеж ности (при отказах разрядных сечений) эв счет перераспределения данных между информационными каналами, Поставленная цель достигается тем, 35 что в буферное запоминающее устройство, содержащее накопитель, входы которого подключены к выходам адресного бпока, входы адресного блока являются

40 управляющими входами устройства,допол нительно введены первый и второй счетчики, входы которых подключены к соответствующим входам адресного блока, и первый и второй блоки коммутации, 45 управляющие входы которых подключены выходам соогветствуюших счетчиков, l информационные входы накопителя подключены к выходам первого блока коммутации, информационные входы которого являются информационнвми входами устройства, вы50 ходы накопителя подключены к информационным входам второго блока коммутации, BbD .oäû которого являются информационными выходами устройства, Кроме того- блок коммутации содержит 55

У матрицу элементов И, дешифратор н регистр, входы которого являются информационными входами блока коммутации, Изобретение относится к вычислитель.. но:В технике и может быть использовано при построении БЗУ в подсистемах ввода иэмери тельной информации.

Известно буферное эапоминвкацее ус г ройство (БЗУ), содержащее блок пемз и и бпок формирования адреса, соединенный с управляющими входами устройства и с адресными вхоаамц блока памяти Г1, Однако это устройство обладает мй лой устойчивостью к отказам блока памяти, что приводит к -искажениям и t1oгерям данных.

Наиболее бпиэким к изобретению по технической сущности является БЗУ, содержащее .накопитель, соединенный с ии формационными входами и выходами устройства, счетчики адреса записи и чтения, входы которых подключены .к управляю-. информационные вкоды 2 накопителя, блок 3 коммутации, выходы накопителя ,4, блок 5 коммутации, адресный блок 6, счетчики 7 и 8 с сответствуюшими выходами 9 и 10, управляющий вход 11 мо,дификации адреса записи, управляющий .вход 12 мщ ификации адреса считывания и управляющий вход 13 задания режима, Блок 6 содержит счетчики адреса эа» писи и чтения, выходы которых соединены с входами элементов И-ИЛИ по числу адреса, а другие входы элементов И-ИЛИ подключены прямо и через инвертор к входу 13, Блоки 3 и 5 коммутации содержат регистр 14, дешифратор 15 и матрицу

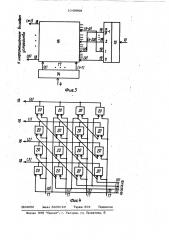

16 элементов И, выходы 18 и входы 19 матрицы 16. Матрица 16 содержит и х и элементов И 20, где tl. — разрядность ячейки памяти. Одни входы элементов

20 И объединены и подключены к соответствующему входу 17,Выходы g йлементов 20, соедженных с раэнымн входами

17 и разными входами 19 подключены к одному и гому же выходу 18, Каждый (иэ входов 19 также подключен к д элементами И 20. Причем к входу 19 с номером К подключаются другие входы эле,ментов 20, стояших на пересечении выхо:дов 18 с номером строки н входа 17 с номером столбца, при этом номера и К связывает зависимость, описываемая выражением (1 ), На фиг, 2 — 4 в скобках показана нумерация разрядов

К - 1 — (4+j ), если + j<9- 1 20 - (i +> )., если + j >n - 1. Модуль счета счетчика 7 и 8 равен копи« честву слов по числу информационных ! каналов, размещаемых в одной ячейке памяти накопителя.

3 хопе

Входы 19 матрицы 16 блоки 3 комМу- тации подключены к выходам дешифратора

15 в порядке возрастания номеров, причем подключается к дешифратору каждый р-й вход 19, начиная с нулевого. В бло- 5 ке 5 коммутации порядок соединений входов 19 обратный, r.е. выходы дешиф ратора 15 в порядке возрастания номеров соединены с каждым р-м входом 19 в. пор дке уб ания нбмеров кр е нул 10 вого.

Устройство работает следующим образом, 1., При записи информации на информационные входы устройства подается входное

cnaso, которое содержит данные от нескольких tl /р измерительных каналов, причем все измерения представляются словами одинаковой разрядности р. Одновременно на вход 13 поступает сигнал операции- "Запись". При помощи этого сигнала с выхода адресного блока 6 на адресные входы накопителя 1 подается .айрес записи, после :чего в выбранную 5 ячейку. памяти записывается входное слово, которое проходит через блок 3 беэ преобразования, так как с выхода счет-. чика 7 на входы дешифратора 15 подается нулевой ко4 В результате этого нулевой вход 19 разрешает прохождение информации иэ регистра 14 блока 3 через элементы И 20 беэ сдвиге. После этого сигналом модификации адреса записи, постуцающим на вход .11, модифицируется адрес записи, формируемый блоком 6, и содержимое счетчика 7. При записи сле. дующего входного слова код счетчика 7".

968 создает разрешающий сигнал на следую-. щем (первом) выходе дешифратора 15 блока 3, который поступает íà P-й управляющий вход 19, разрешающий прохождение информации из регистра 14 на выходы 18 со сдвигом íà P разрядов, r.е. данные первого канала занимают место данных последнего канала, а данные остальных каналов сдвигаются, занимая место данных предыдущего канала. Если одно из разрядных сечений накопителя 1 отказывает, то .сечение проходит через данные нескольких каналов, упакованных в одно слово, а не через данные одного канала. Тем самым потери информации распределяются между несколькими каналами, При чтении информации иэ устройства производится- сдвиг в обратную сторону, тем самым восстанавливается исходный формат входных данных,,0ля осуществления обратного сдвига используется блок

5 коммутации, управляемый счетчиком 8, Оба блока 3 и 5 идентичны и отличаются друг от друга только порядком соединения управляющих входов 19 матрицы 16 с выходами дешифратора 15. Содержимое счетчика 8 модифицируется после каждого цик;ла чтения сигналом модификация адреса -" чтения, поступающего на вход 12.

Предлагаемое устройство позволяет повысить надежность устройства и избежать полной подбери данных одного канала при отказе разрядного сечения эа счет распределения этих потерь между несколькими каналами, что при избыточности измерительной информации является допустимым в определенных пределах.

1049968

ФигЗ

У

78

ЧВ

ВНИИПИ Заказ 8436/49 Тираж .594 Подписное

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 5