Запоминающее устройство

Иллюстрации

Показать всеРеферат

С ЗЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

3(5Р G, 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВ, ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3467332/18-24 (22) 08.07.82 (46) 23.10.83. Бюл. 9 39 (72) Л.О. Беспалов и A.Ã. Головачев (53) 681.327.6(088.8) (56 ) 1. Авторское свидетельство СССР

М 467409, кл. G 11 С 29/00, 1974 ° . 2. Авторское свидетельство СССР по заявке В 3339806/24, кл. G 06 F 9/06, 1981 (прототип). (54)(57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО содержащее блоки памяти, первые и вторые входы которых являются.входои устройства, вторые входы блоков.памяти подключены к входу элемента задержки, два блока контроля, первые входы . которых связаны с выходом элемента задержки, первый выход одного йлока памяти подключен к второму входу перво.го блока контроля и к.первому входу первого элемента И, первый выход другого блока памяти подключен к второму входу второго блока контроля н к первому входу второго элемента И, второй выход одного блока памяти соединеи с третьим входом первого блока контрОля и с.вторым входом первого элемента И, второй. выход другого блока памятн ПОд- ключен к третьему входу второго блока контроля н к второму входу второго . элемента И, выходи первого и второГо элемента И соединены с блоком элемеитов ИЛИ, выход которого является вы

„.SU„„49982 А ходом устройства, о т л и ч а ю щ е е«." .с я тем, что, .с целью повышения быстродействия.устройства при высокой достоверности считываемой информации, оНо содержит третий элемент И, блок сравнения, три блока элементов И, причем первый и второй входы блока сравнения подключены соответственно к первым выходам одного и другого блока памяти, первый вход первого блока элементов И соединен с выходом первого блока контроля, первый вход второго блока элементов И подключен к выходу второго блока контроля, первый вход третьего блока элементов И соединен с первым выходом блока сравнения,вторые входы первого и второго . ф блоков элементов И подключены к второму выходу блока сравнення, второй вход третьего блока элементов H соединеы с вторым входом устройства, выход первого блока элементов И подключен к третьему входу первого эле- O

Т мента И, выход второго блока элементов H соединеН с третьии входом вто- рого элемента И, выход третьего блока элементов И подключен к третьему входу третьего элеиента И, первый вход третьего элемента К соединен с уе вторыми выходом одного блока памяти, а второй вход - с первым выходом (© другого блока памяти, выходы третье- О го элелинта и подк>почены к входу блока элементов ИЛИ.

1049982

Изобретение относится к цифровой вычислительной технике и мо ет быть использовано в составе специализиро-.

,ванных цифровых вычислительных машин (СЦВМ) или систем обработки и передачи цифровых данных.

Известно запоминающее устройство с контролем записанной информации, содержащее адреса, выход которого через дешифратор адресов подключен к входу накопителя, соединенного соответствующими выходами с входами регистра, причем любая ячейка памяти наряду с информационной частью имеет дополнительные разряды, в которых хранятся контрольные признаки сверт- 15 ки, относящиеся как к коду числа,так и к коду адреса, по которому выбирается данная ячейка (1 ).

Недостатком этого устройства является отсутствие в его составе средств28 обеспечивающих функционирование устройства при обнаружении в нем схемами контроля отказа одной из ячеек накопителя, что снижает его надежность.

Кроме того, свертка информации по мо- 25 дулю и сравнение ее с контрольными признаками, необходимое для установления факта исправности или неисправ-. ности, увеличивает время выдачи информации из устройства, что приводит к снижению его быстродействия.

Наиболее близким к изобретению по технической сущности является запоминающее устройство, содержащее блок постоянной памяти и блок памяти с электрической сменой информации,вклю-з5 чающие информационную сеть с контроль, ыми признаками, блок коитроля, сосоящий из схемы свертки и схемы сравнения, блоки вентилей,. блок сравнения контрольных признаков и выходной 49 блок. В случае отказа по любому адресу ячейки постоянного запоминающего блока, в устройстве обеспечена возможность замещения ее ячейкой памяти постоянного запоминающего блока с элект-45 рической сменой информации E 23.

Недостатком известного устройства является необходимость осуществления свертки информации, считываемой

*. как из постоянного запоминающего блока, так и йз постоянного запоминающего блока с электрической сменой информации, и сравнение свертки информации с ее контрольными признаками, в результате чего увеличивается время выдачи информации из устройства, что приводит к снижению его быстродействия.

Цель изобретения - повышение быстродействия устройства при высокой достоверности считываемой информации.60

Поставленная цель достигается тем, что в запоминающее устройство,содержащее блоки памяти, первые и вторые ,входы которых являются входом устрой;ства, вторые входы блоков памяти под-65 ключены к входу элемента задержки, два блока контроля, первые входы которых связаны с выходом элемента задержки, пЕрвый выход одного блока памяти подключен к вторбму входу перaoro блока контроля и к первому входу первого элемента И, первый выход другого блока памяти подключен к второму входу второго блока контроля и к первому входу второго элемента И, торой выход, одного блока памяти соеинен с третьим входом первого блока контроля и с вторым входом первого элемента И, второй, выход другого блока памяти подключен к третьему входу второго блока контроля и к второму входу второго элемента И, выходы первого и второго элементов И соединены с блоком элементов ИЛИ, выход которого является выходом устройства, введены третий элемент И, блок сравнения,три блока элементов Й, причем первый и второй входы блока сравнения подключены соответственно к первым выходам одного и другого блоков памяти, первый вход первого блока элементов И соединен с выходом первого блока контроля, первый вход второго блока элементов И подключен к выходу второго блока контроля, первый вход третьего блока элементов И соединен с .первым выходом блока сравнения, вторые входы первого и второго блоков элементов

И подключены к второму выходу блока сравнения, второй вход третьего блока элементов И соединен с. вторым входом устройства, выход первого блока элементов И подключен к третьему входу первого элемента И, выход второго блока элементов соединен с третьим входом второго элемента И, выход третьего блока элементов И подключен к третьему входу третьего элемента И, первый вход третьего элемента И соединен с вторым выходом одного блока памяти, а второй вход — с первым выходом другого блока памяти, выходы третьего элемента

И подключены к входу блока элементов ИЛИ.

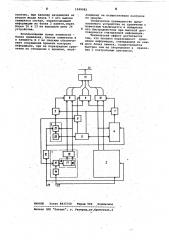

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит два блока 1 и

2 памяти, два блока 3 и 4 контроля, три блока 5-7 элементов И, три элемента И 8-10, блок 11 сравнения,элемент 12 задержки, блок 13 элементов

ИЛИ. Каждый из блоков 1 и 2 памяти включает в себя регистр 14 адреса, дешифратор 15 кода адреса, накопитель 16, информационное поле 17 накопителя, поле 18 контрольных разрядов накопителя, выходной регистр

19. Каждый из блоков 3 и 4 состоит иэ блока 20 свертки по модулю два и блока.21 сравнения. Устройство содержит адресный вход 22, вход 23 опроса и выходную шину 24, являющую1049982

cg.выходом устройства. Первые входы блоков 1 и 2 памяти подключены к адресному входу 22 .устройства, вторые входы блоков памяти соединены с: входом 23 опроса устройства. Первый выход блока 1 памяти подключен к вто- 5 рому входу блока 3, к первому входу элемента И 8 и к первому входу блока 11. Второй выход блока 1:памяти соединен с третьим входом блока 3, с вторым входом элемента И 8 и с пер- 10 вым входом элемента И.9. Первый выход блока памяти. 2 подключен к второму входу блока 4, к первому входу элемента И 10, к второму входу элемента И и к второму входу блока 11.Вто» 15 рой выход блока 2 памяти соединен с третьим входом блока 4 и со вторым входом элемента И 10. Первые входы волоков 3 и 4 подключены к выходу элемента 12 задержки, вход которого сое-20 динен с входом 23 опроса устройства.

Выход блока 2 подключен к первому входу блока 5, а выход блока 4 соединен с первым входом блока 7.

Вторые входы блоков 5 и 7 подключены 25 к второму выходу блока 11, первый выход которого соединен с первым входом блока 6. Второй вход которого подключен к входу 23 опроса устройства. Выходы блоков 5 — 7 соединены с третьими входами элементов И. 8 — 10 соответственно. Выходы элементов И

8 - 10 подключены к входу блока 13, выход которого соединен с выходной шиной 24. Второй вход блока 3 (4) яв ляется входом блока 20, выход которо-З5 го подключен к первому входу блока 21., Второй и третий входы блока 21 являются первым и третьим входами блока

3(4), а его выход — выходом соответственно блока 3(4). Первый вход бло- 40 ка 1(2) памяти является входом регистра 14, выход которого связан с первым входом дешифратора 15, второй вход которого является вторым входоМ блока 1(2 )памяти . Выход дешифратора 15 45 подключен к входу накопителя 16.Информационное поле 17 и поле 18 контроль" ных разрядов накопителя 16 связаны с выходным регистром 19, первый и второй выходы которого являются соот-50 ветственно первым и вторым выходами ,блока 1(2 ) памяти.

Устройство работает следующим о6разом.

На вход 22 устройства поступает код адреса, а.на вход 23 — сигнал опроса. В каждом блоке 1 и 2 памяти код адреса подается на вход регистра 14, а сигнал опроса - на второй вход дешифратора 15, управляемого регистром 14. При наличий сигнала . 60 опроса на входе дешифратора 15; на одном из его выходов появляется сигнал, при помощи которого выбирается информация из соответствующей ячейки накопителя 16. С выхода информацион- 65 ного поля.17 и поля 18 контрольных разрядов, накопителя 1ф, считанная информация поступает на вход регистра 19 ° С выхода регистра 19 информация поступает на выходы блоков 1 и 2 памяти. Информационная ее часть с первого выхода блоков 1 и 2 памяти подается соответственно на первый и второй входы блока 11, где осуществляется поразрядное сравнение. В случае равенства сравниваемой информации на первом выходе блока 11 формируется разрешающий потенциал для блока 6 элементов И. При наличии на втором входе блока 6 элементов И сигнала опроса, этот сигнал, пройдя блок б элементов И, поступает на третий вход элемента 9. На первый вход элемента

9 подаются контрольные признаки информации, считываемые из блока 1 памяти, а на второй вход элемента И 9 информационная часть, считанная из блока 2 памяти. При наличии на третьем входе элемента И 9 сигнала опроса, поступившая на его первый и .второй входы информация будет передана через блок 13 на выходную шину 24.

В случае неравенства информации, поступающей на вход блока 11, на его первом выходе появляется сигнал запрета для блока 6 элементов И, а на втором выходе - сигнал разрешения для блоков 5 и 7 элементов И. Информация с выходов блоков 1 и 2 памяти поступает. соответственно на входы блоков

3 и 4 контроля, где ее информационная часть свертывается при помощи блока 20. по заложенным контрольным признакам. Результаты свертки сравниваются в каждом блоке 3 и 4 с контрольным признаком (признаками) блоком 21 сравнения. Сигнал опроса подается на первые входы блоков 3 и 4 контроля с выхода элемента задержки 12 (для синхронизации работы устройства). В случае равенства результата свертки информационной части и .контрольного признака (признаков) в блоке 3, а также наличия сигнала опроса на входе этого блока блок 21 блока 3 формирует сиг-.. нал, который поступает на вход блока

5 элементов И. При наличии на втором входе блока 5 разрешения на его выходе появляется сигнал, который поступает на третий вход элемента 8. По этому сигналу информация, поступившая на вход элемента 8 передается, через блок элементов ИЛИ 13 на выходную шину 24 устройства. В случае неравенства результатов свертки инфбрмационной части и контрольного признака (признаков) в блоке З,этот блок не вырабатывает сигнал опроса.

В работу включатся цепи, обеспечива- . ющие ситывание информации из блока

2 памяти через элемент 10. Работа блока 4 и формирование им сигнала опроса для блока 7 происходит ана1049982

I

ВНИИПИ Заказ 8437/50 Тираж .594 Подписное

Филиал ППП "Патент", r. Ужгород,ул.Проектная,4

Ъ логично. При наличии разрешения на втором входе блока 7 с ez î, выхода снимается сигнал, переписывающий информацию из блока 2 памяти, через блоки 10 и 13 на выходную шину 24 устройства.

Использование новых элементов— блока сравнения, блоков элементов И и Элемента И с их связями обеспечивает сокращение времени контроля информации, при .ее поразрядном сравнении по .отношению к времени, необходимому на осуществление контроля .по модулю.

Техническое преимущество предлагаемого устройства по сравнению с известным заключается в повьиаении

5 его быстродействия при высокой достоверности считываемой информации.

Технический эффект достигается тем, что процесс поразрядного сравнения информации, считываемой из каж10 дого блока памяти, осуществляется быстрее чем ее свертывание и сравнение с контрольным признаком.