Устройство для контроля блоков постоянной памяти

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИК

„„SU„„983 А

3(51) 0 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНбМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

fO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

f21) 3469998/18-24 (22) 09.07.82

; (46 ) 23. 10. 83. Вюл. М 39 (72) В.A. Калиниченко и Л.Ф.. Супрун (53) 681.327 ° 6(088.8) (56) 1. Авторское свидетельство СССР

9 510753, кл.G 11 С 29/00, 1976.

2. Устройства эапоминающие постоянные. Методы контроля функционирования. ОСТ 92-8565- 74 (прототип ). (54)(57) УСТРОЙСТВО ЦЛЯ КОНТРОЛЯ ВЛОКОВ ПОСТОЯННОЙ ПАМЯТИ, содержащее. генератор импульсов, шифратор дополнительных кодов эталонных контрольных сумм, элемент И, счетчик адреса, цешифратор, блок сумматоров, блок триггеров и индикации, причем генератор импульсов подключен к шифратору дополнительных кодов эталонных конт- рольных сумм, элементу И и счетчику адреса, выходы которого соединены с входами дешифратора, выход которого соединен с входом генератора импульсов и вторым входом элемента И, первый вход блока сумматоров соединен с выходом шифратора дополнительных кодов эталонных контрольных сумм, о т л и ч а ю щ е е с я тем, что, с целью повышения, быстродействия устройства, оно содержит первый и второй блоки элементов И,первые входы второго блока элементов И,подключены к выходу блока сумматоров, вторые входы. соединены с выходом элемента И, а.выходы соединены с входами блока триггеров и индикации, одни входы первого блока элементов И соединены с выходами счет- Е

O чика адреса, а другие .являются входом устройства, выходы первого блока элементов И соединены с вторыми входами. блока сумматоров.

1049983

Изобретение относится к запоминающим устройствам, а именно к устройствам контроля блоков постоянной памяти.

Известно устройство, содержащее считывающий блок, подключенный к входам блока управления и регистра адреса, и блок сравнения, счетчик и сумматор, входы которого подключены к выходам регистра адреса и одним входом блока сравнения, а вы- !О ходы - к входам счетчика, выходы которого соединены с другими входами блока сравнения, выход которого подключен к блоку управления (1).

Однако это устройство содержит )5 в своем составе считынающий блок, что снижает быстродействие устройства, а также не содержит в своем составе схем, обеспечивающих проверку блоков постоянной памяти по полным и частным контрольным суммам, 20

Наиболее близким к изобретению по технической сущности является устройство для контроля блоков постоянной памяти методом полных и частных контрольных сумм, содержа.щее блок управления, счетчик адре сов, счетчик сумм, дешифратор,устройство установки, блок ОЗУ, сумматор, сборку разрядов сумматора, блок сравнения °

В.этом устройстве формирование и проверка частных и полных контрольных. сумм на соответствие эталонным осуществляется путем (и+1) кратного просчета контрольных сумм по всем адре- 35 сам проверяемого блока постоянной памяти, где п - количество разрядов счетчика адреса Г2 3..

Недостатком известного устройства является низкое быстродействие., так, 40 как для получения контрольных сума требуется (и+1) циклов обращения к адресам проверяемого блока постоянной памяти.

Цель изобретения - повышение быст-45 родействия усУройства за счет получения всех контрольных сумм за один цикл обращения к адресам проверяемого блока памяти.

Постанленная цель достигается тем, 0 что в устройство, содержащее генератор импульсон, шйфратор дополнительных кодов эталонных контрольных сумм, элемент И, счетчик адреса, дешифратор, блок сумматоров, блок триггеров и индикации, причем генератор импуль-55 сов подключен к шифратору дополни-. тельных кодов эталонных контрольных сумм, элементу И и счетчику адреса, выходы которого соединены с входами дешифратора, выход которого соединен 60 с входом генератора импульсов и вторым входом элемента И, первый вход блока сумматоров соединен с выходом аифратора дополнительных кодов эталонных контрольных сумм введены пер- 65. вый и второй блоки элементов И, пер- . вые входы второго блока элементов

И подключены к выходу блока сумматоров, вТорые входы соединены с выходом элеменТа И, а выходы соединены с входами блока триггеров и индикации, одни входы первого блока элементов И соединены с выходами счетчика адреса, а другие являются входом устройства, выходы первого блока элементов И соединены с вторыми входами блока сумматоров.

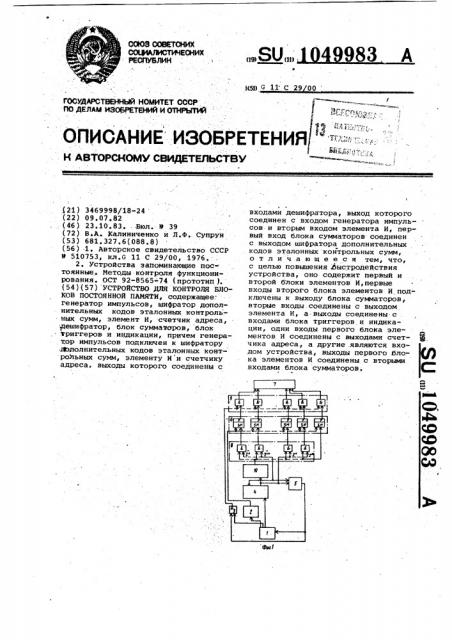

Ha фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 закономерность формирования сигналов на вторых. входах первого блока элементов И для блока постоянной памяти на восемь чисел.

Устройство для контроля блоков постоянной памяти содержит генератор 1, шифратор 2 дополнительных кодов эталонных контрольных сумм, элемент И 3, счетчик 4 адреса, дешифратор 5, блок б сумматоров, блок 7 триггеров и индикации, дополнительные первый и второй блоки элементов И 8 и 9. Первый выход генератора 1 импульсов подключен к входу дешифратора 2 дополнительных кодов эталонных контрольных сумм, второй выход генератора 1 импульсов подключен к первому входу элемента И 3 и входу счетчика 4 адреса. Прямые и инверсные выходы счет- чика 4 адреса соединены с входами дешифратора 5, выход которого соединен с входом .генератора 1 импульсов, и вторым входом элемента И 3. Блок 6 сумматоров первым входом подключен к выходу шифратора 2 дополнительных ходов эталонных контрольных сумм.

Первые входы второго блока элементов

И 9 подключены к выходам блока б сумматорон, нторой вход соединен с выходом элемента И 3, а выходы соединены с входами блока 7 триггеров и индикации. Первый блок элементов И

8 первцми входами соединен с выходами проверяемого блока посТоянной памяти 10, а вторыми выходами соединен:. с прямыми и инверсными выходами счетчика 4, адреса, выходы первого блока элементов И 8 соединены с вторыми входами блока 6 сумматоров.

Устройство работает следующим образом.

Первый импульс нулевого цикла генератора 1 импульсов поступает на вход шифратора 2 дополнительных кодов эталонных контрольных сумм, с выхода которого дополнительные коды эталонных полной и частных контрольных сумм поступают íà первые входы блока б сумматоров. Код нулевого адреса с выхода счетчика 4 адреса поступает на вход контролируемого блока постоянной памяти. Информация с выхода контролируемого блока постоянной памяти через первые,.1049983

Фиа2

Составитель O. Кулаков

Редактор О. Черниченко Техред.М.Надь Корректор А.Дзятко

8437/50 Тираж 594 Подписное

ВНИИПИ Государственного, комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Заказ. Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4. входы первого блока элементов И 8 .поступает на вторые входы блока б сумматоров.

Прямые и инверсные выходы разрядов счетчика 4 адреса соединены с вторыми входами блока элементов И 8 таким образом, что информация на вход соответствующего сумматора частной сумма в блок б сумматоров поступает только в том случае, если в соответствии с таблицей (фиг. 2) данный 1Î адрес участвует в формировайии.соот-. ветствующей частной контрольной сум мы, знак "1" показывает, что содержимое соответствующей ячейки адреса входит в состав данной суммы, а f5 знак "0" - содержимое ячейки не входит в состав суммы.

Информация, сОответствующая первому, второму и т.д. адресам контролируемого блока постоянной памяти обрабатывается аналогично. После пере бора количества адресов, соответствующего емкости контролируемого блока постоянной памяти, сигнал с выхода дешифратора 5 поступает на вход

"Останов" генератора 1 импульсов и на второй вход элемента И 3,.по совпадению с последним импульсом данного цикла с .выхода генератора 1 импульсов, сигнал с выхода элемента И 3 поступает на первый вход второго блока элементов И 9. В случае несоответствия одной иэ контрольных .сумм эталонному значению сигнал с выхода второго блока И 9 вызывает срабатывание триггера с соответствующей индикацией в блоке 7 триггеров и индикации. Процесс контроля заканчивается.

Предлагаемое устройство обеспечивает получение всех контрольных сумм за один цикл обращения q адресам проверяемого блока памяти, что отсутствовало ранее в известном,и обеспечи,вает снижение времени койтроля в

2 раза.