Стабилизированный преобразователь напряжения

Иллюстрации

Показать всеРеферат

СТАБИЛИЗИРОВАННЫЙ ПРЕ. ОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ, содер: жащий выходной выпрямитель с фильтром, подключенный к трансформатору усилителя мощности, управляющие переходы транзис-, торов которого соединены с выходами двух логических элементов И, при этом первые входы последних подключены к парафазным выходам триггера, счетным входом, подключенного к генератору тактовых импульсов, их вторые входы объединены и подключены к выходу узла защиты, а третьи, объединенные входы подключены к выходу триггера широтно-импульсного модулятора, Sвход которого подключен к выходу упомянутого генератора, тактовых импульсов, Rвход - к выходу компаратора, одним из входов подключенного к генератору линейно измен 1ющегося напряжения, а также опорный -источник,, отличающийся тем, что с целью .повыщення стабильности выходного напряжения при резких изменениях напряжения электроснабжения, в него введены пиковый детектор и управляемый ключ, при этом генератор линейно изменяющегося на с: & пряжения выполнен по схеме интегратора с сумматором на входе, первый из входов (Л которого подключен к выходу опорного источника , второй -к выходу выходного фильтра , третий - к выходу выпрямителя и входу пикового детектора, четвертый - к выходу последнего и выходу управляемого ключа , управляющий вход которого подключен к выходу R-S триггера.

СОЮЗ СОВЕТСКИХ

СС)ЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1050061 д ц Н 02 М 3/335; G 05 F 1/64

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ гор-»

1 .1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ I

Н ABTOPCKOMV СВИДЕТЕЛЬСТВУ

С

CO

CO

С5 (21) 3409552/24-07 (22) 12.03.82 (46) 23.10.83. Бюл. № 39 (72) В. В. Попов, А. И. Скоков, Е. С. Мытник и В. Э. Пацевич (71) Специальное. конструкторско-технологическое бюрб с опытным производством Минского радиотехнического института (53) 621.314.58 (088.8) (56) 1. Авторское свидетельство .СССР № 817696, кл. G 05 F 1/64, 1979.

2. Патент США № 3873903, кл. G 05 F 1/56, 1975.

3. Патент Великобритании М0 2019132, кл. Н 02 М 3/335,,19?9.

4. Патент США № 4150424, кл. Н 02 М 3/335, 1979. (54) (57) СТАБИЛИЗИРОВАННЫИ ПРЕ-., ОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ, содержащий выходной выпрямитель с фильтром, подключенный к трансформатору усилителя мощности, управляющие переходы транзисторов которого соединены с выходами двух логических элементов И, при этом первые входы последних подключены к парафазным выходам триггера, счетным входом, подключенного к генератору тактовых импульсов, их вторые входы объединены и подключены к выходу узла защиты, а третьи объединенные входы подключены к выходу R-S триггера широтно-импульсного модулятора, S вход которого подключен к выходу упомянутого генератора тактовых импульсов, Rвход — к выходу компаратора, одним из входов подключенного к- генератору линейно изменяющегося напряжения, а также опорный -источник,. отличающийся тем, что с целью повышения стабильности выходного напряжения при резких изменениях напряжения электроснабжения, в него введены пиковый детектор и управляемый ключ, при этом генератор линейно изменяющегося на пряжения выполнен по схеме интегратора с В сумматором на входе, первый из входов которого подключен к выходу опорного источника, второй — к выходу выходного филь- у тра, третий — к выходу выпрямителя и вхо- ду пикового детектора, четвертый — к выходу последнего и выходу управляемого клю- 2 ча, управляющий вход которого подключен к выходу R-S триггера.

1050061

Цель изобретения — повышение стабильности выходного напряжения преобразователя при резких изменениях напряжения электроснабжения., Поставленная цель достигается тем; что 4 стабилизированный преобразователь напряжения содержащий выходной выпрямитель с фильтром, подключенный к трансформатору усилителя мощности, управляющие переходы транзисторов которого соединены с выходами двух логических элементов И, при этом первые входы последних подключены к парафазным выходам триггера, счет- @ ным входом подключенного к генератору тактовых импульсов, их вторые входы объединены и подключены к выходу узла за- у щиты, а третьи объединенные входы подключены к выходу К-S триггера ширЬтноимпульсного модулятора, S-вход которого

Изобретение относится к преобразовательной технике и может быть использовано при разработке источников вторичного питания радиоэлектронной аппаратуры.

Известны стабилизированные преобразователи, содержащие усилитель, модности с выходным трансформатором, выпрямителем и фильтром, управляющие переходы которых подключены к узлу управления, выполненного на логических элементах И, счетном триггере, широтно-импульсном модуляторе (ШИМ) и генераторе тактовых импульсов (1), (2) и (3).

Недостатком данных преобразователей является низкая стабильность при резких изменениях входного напряжения питания.

Наиболее близким к изобретению по технической сущности является стабилизированный преобразователь, содержащий выходной выпрямитель с фильтром, подключенный к трансформатору усилителя мощности, управляющие переходы транзисторов которого подключены к выходам двух логических элементов И, при этом первые входы. последних подключены к парафазным выходам триггера, счетным входом подключенного к генератору тактовых импульсов, их вторые входы объединены и подключены к выходу узла защиты, а третьи объединенные входы подключены к выходу R-S триггера широтно-импульсного модулятора, S-вход которого подключен к выходу упомянутого генератора тактовых импульсов, R-вход — к выходу компаратора, одним из входов подключенным к генератору линейно изменяющегося напряжения, а также опорный источник (4).

Недостатком известного преобразователя также является низкая стабильность выходного напряжения из-за применения обратной связи с выхода выходного фильтра, так как ошибка выходного напряжения в устройстве будет отработана только в последующих тактах из-за задержки, внесенной постоянной временй фильтра.

40 подключен к выходу упомянутого генератора тактовых импульсов, à R-вход — к выходу компаратора, одним из входов подключенного к генератору линейно изменяющегося напряжения, а также опорный источник, введены пиковый детектор и управляемый ключ, при этом генератор линейно изменяющегося напряжения выполнен по схеме интегратора с сумматором на входе, первый из входов которого подключен к выходу опорного источника, другой — к выходу выходного фильтра, третий — к выходу выпрямителя и входу пикового детектора, четвертый — к выходу последнего и выходу управляемого ключа, управляющий вход которого подключен к выходу

R-S триггера.

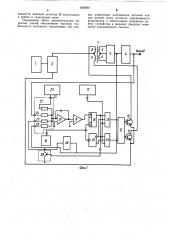

На фиг. 1 приведена структурная схема стабилизированного преобразователя напряжения; на фиг. 2 и 3 — временные диаграммы, поясняющие работу устройства..

Преобразователь содержит источник 1 электроснабжения с фильтром 2, выходной выпрямитель 3 с выходным фильтром 4,. под ключенный к выходным полуобмоткам 5 и

6 трансформатора 7, первичные полуобмотки

8 и 9 которого подключены к транзисторам

10 и 11 усилителя мощности, при этом управляющие переходы транзисторов через узел 12 согласования подключены к выходам двух логических элементов И 13 и 14, первые входы которых подключены к парафазным выходам счетного триггера 15, счетным входом соединенного с генератором 16 тактовых импульсов, вторые входы элементов И объединены и подключены к выходу узла 17 защиты, а их третьи объединенные входы соединены с выходом R-S триггера 18, S-вход которого подключен к выходу генератора тактовых импульсов, R-вход к выходу компаратора 19, входом подключенного к выходу интегратора 20 с сумматором 21 на входе, первый вход 22 которого подключен к выходу опорного источника

23, второй вход 24 — к выходу выходного фильтра, третий вход 25 — к выходу. выпрямителя и входу пикового детектора

26, четвертый вход 27 — к выходу последнего и выходу управляемого ключа 28, управляющий вход которого подключен к выходу R-S триггера 18.

Преобразователь работает следующим образом.

Когда на суммирующий вход 22 интеграгора 20 (фиг. 1) поступает эталонное отрицательное постоянное напряжение с источника 23 опорного напряжения, конденсатор интегратора заряжается по пилообразному закону и на выходе интегратора 20 появляется линейно возрастающее положительное напряжение (фиг. 36),. которое поступает на неинвертирующий.вход компаратора 19, а с. его выхода — íà R-вход R-S триггера 18.

1050061 или 11 проходят через другую схему . И.

Схема 17 защиты запрещает прохождение импульсов управления на выход элементов

И и, соответственно, на базы транзисторов

10 и 11 в случае аварии.

Увеличение стабильности выходного напряжения достигается за счет того, что в предлагаемом устройстве за счет наличия ° обратной связи с выхода выпрямителя сигПоследовательность импульсов (фиг. За) с выхода генератора 16 синхроимпульсов поступает на вход счетного триггера 15.

Парафазные выходы счетного триггера 15 (фиг. 3е, Зд) устанавливают разрешающий положительный потенциал на входах схем

13 и 14 И. Синхроимпульс, поступающий на

S-вход R-S триггера 18, переводит его в состояние логической единицы (в состояние логического нуля К-S триггер был переведен в предыдущем такте по R-входу. При этом на одном из выходов элементов И 13 или

14, в зависимости от наличия разрешающего положительного потенциала на одной из схем 13 или 14 появится положительный потенциал, который без инверсии проходит через согласующий узел 12 и открывает соответствующий из транзисторов 10 или

1 1 (фиг. 33, 3U) . ПОЯВКВшийсЯ при этом импульс тока через трансформатор 7 при-. водит к появлению выходного положительного импульса (фиг. 314) на выходе выпрямителя. !

Этот импульс поступает через вход 25 на вход интегратора 20 и заставляет конденсатор интегратора разряжаться, уменьшая напряжение на выходе интегратора (фиг. 2а). Интегратор сравнивает интегральное значение входного сигнала (площадь S, входного сигнала на тактовом промежутке) с интегральным значением выходного импульса (площадь Sy выходного импульса на том же тактовом промежутке). Как только напряжение на выходе интегратора 20 достигнет нуля (площади входного и выходного сигналов равны), срабатывает компаратор 19 и по фронту импульса на его выходе переведет (по входу R) выход триггера 18 в нулевой потенциал. Этот нулевой потенциал через соответствующую схему И (13 или 14) и согласующий узел 12 выключит соответствующий транзистор 10 или 11. При

-этом, естественно, прекращается и импульс на выходе выпрямителя 3.

Далее конденсатор интегратора 20 вновь начинает заряжаться (фиг. 2г), выходной сигнал интегратора - переводит выход компаратора 19 в состояние логической единицы. Процесс переключения схемы в рас сматриваемом такте закончился.

Аналогично происходит работа схемы и в следующем такте, с той лишь разницей, что импульсы управления транзисторами 10 нал рассогласования (или ошибки) отрабатывается в том же такте, когда он возник. Предположим, что напряжение питания стабилизированного преобразователя напряжения изменилось на +Е1 (фиг. 2б). Положим, что напряжение изменилось до прихода тактового импульса, включающего силовые транзисторы. При этом конденсатор интегратора, заряжается от опорного источника (фиг. 2а) и с приходом тактового им10 пульса (фиг. 2в) напряжение обратной связи с выхода выпрямителя поступает на суммирующий вход 25 интегратора 20 и разряжает конденсатор. Прк этом, чем выше напряжение +E>, .тем быстрее разрядится конденсатор и быстрее окончится импульс на выходе преобразователя. При этом интегратор сравнивает площади входного (Sq) и выходного (S ) напряжения на тактовом промежутке. Таким образом, ошибка после выпрямителя 3 до фильтра 4 отсутствует.

20 Пусть напряжение изменилось на + E,i в момент, когда на выходе имеется силовой импульс. В этом случае, поскольку интегратор работает непрерывно, напряжение, поступающее на его вход с выхода выпрямителя до фильтра, заставит конденсатор ин25 тегратора быстрее разрядиться. что в свою очередь приведет к полной компенсации оши— бки, Таким образом, ошибка на выходе фильтра 4 всегда будет отсутствовать. г

Однако использование одной Описанной обратной связи оказывается недбстаточным.

При больших длительностях импульса управления происходит скалывание импульса на выходе трансформатора ? и, естественно, на выходе выпрямителя 3. Это может привести к тому, что импульс на выходе выпрямителя за счет скалывания закончится раньше, чем разрядится до нуля конденсатор интегратора. Т.е. входной сигнал управления не будет отработан выходным импульсом. В этом случае, за счет входного сиг40 нала выход интегратора 20 будет все время находиться в области положительных напряжений, триггер 18 несмотря на наличие на входе тактовых синхроимпульсов перебрасываться не будет, следовательно будет остановлен и процесс переключения выходных

4> транзисторов 10 и 11. Чтобы этого не произошло в схему введены пиковый детектор

26 и управляемый ключ 28. Амплитуда сигнала на выходе пикового детектора 26 соответствует максимальной амплитуде на выходе выпрямителя 3 и будет сохранять свою величину до окончания импульса на выходе выпрямителя, т.е. до достижения на выходе интегратора 20 нулевого потенциала и срабатывания компаратора 19, выключения триггера 18. Своим спадом импульс с выхода у триггера 18 выключает управляемый ключ

28 и сбрасывает выход пикового детектора

26 на ноль. С приходом следующего тактового импульса управляемый ключ 28 разl050061

S мыкается, пиковый детектор 26 подготовлен к работе в следующем такте.

Применение обоих дополнительных обратных связей обеспечивает высокую стабильность выходного напряжения при резких изменениях напряжения питания или при резкой смене входного управляющего напряжения и обеспечивает надежную работу устройства в широких пределах изменения управляющего сигнала..1050061

Opia

К+»

Мпи

Иа генг

Т.Н г иь инае

pcrrn д ц коил

О.П

Фа т, Ж

Фа

Tg

4 eain и

УВы пик делю

УЬ фимау

1050061

Составитель И. Никитин

Редактор А. Шандор Техред И. Верес Корре кто р Л. П а тай

3 а к аз 8448/54 Тираж 687 Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4