Дешифратор

Иллюстрации

Показать всеРеферат

ДЕШИФРАТОР; состоящий иЛ симметричного входного каскада, содер жащего в каждом из двух каналов переключающий и инвертирующий п-р-п транзисторы с объединенными между каналами эмиттерами, и выходного каскада, содержащего в каждой из четырех групп/г-р-А транзисторы и иижектирующне р-п-р транзисторы с объединенными базами, причем коллекторы р-л-р транзисторов каждой группы соединены с выходногол-р-/1ТранЯйсгбратб же группы, а такЖе содержа1а1ЯЙ шияы питания, нулевого потенциала, , входные н четыре выходные Шины, при этом к оллекторы выходных л -р-п транзисторов каждой группы соединены с соответствующей выходной щиной, а эмиттеры всех инжектирук щих рц-р транзисторов связань с шиной питания, отличающийся тем, что, : с целью повышения быстродействия и нагру . зочной способности, база переключающего транзистора подключена к коллектору первого инжектирующего транзистора и к соответствующей входной щиие, объединенные эмиттеры переключающих и базы первых инжектирующих транзисторов соединены с объединенными эмиттерами инвертирующих с базами втбрых инжектирующих транзисторов и с щиной нулевого потенциала, коллекторы нивертнрующих транзисторов каждого из каналов связаиы с соответствующим : объединением базы п-р-п н коллектора р-п-р Выходных транзисторов, коллекторы переключающих транзисторов каждого из ка налов соединены с соответствующим объеi динением базы инвертирующего и коллекто ра второго инжектирующего траизисторов СЛ . того же канала и с соответствующим объединеннем базып-р-п коллектора р-п-р выхо-. дных транзисторов, причем эмиттеры п-р-П и базы р-п-р выходных транзнсторов по: парно объединены н сЬед

СОЮЗ СОВЕТСКИХ .СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(50 Н 03 К 1324

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Я АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИИ И ОТНРЫТИЙ (21) 248806!/21 (22) 19.05.77. (46) 23.10.83. Бюл. № 39 (72) А. 3. Иванников и А. Д. Кравцов (53) 621.372 (088.8) (56) l. Каталог электронных. схем фирмы

«Texas Jnstruments std». Епфапд, 1971, р р. 9-192.

2. Авторское свидетельство СССР № 610298, кл. Q 03 К 13/24, 29.10.76, (54) (57) . ДЕШИФРАТОР, состоящий нэ симметричного входного каскада, содер- жащего в каждом из двух каналов переключающий и инвертирующнй е-р-и транзисторы с объединенными между каналами .эмиттерами, и выходного каскада, содержащего в каждой из четырех группа-р-eтраизисторы и инжектирующие р-и-р транзисторы с объединенными базами, причем коллекторы ра-р транзисторов каждой группы соединены с базой выходногоф-р gтрaнзистора той же группы, а также содержащий шины питания, йулевого потенциала, две .входные и четыре выходные шины, при этом

- коллекторы выходных а -р-а транзисторов каждой группы соединены с соответствую щей выходной шиной, а эмиттеры всех, инжектирующих pW-ð транзисторов связанй

„.SU„,1050110 A с шиной питания, отличающийся тем, что, : с целью повышения быстродействия и натру: зочной способности, база переключающего транзистора подключена к коллектору пер: вого инжектнрующего транзистора н к соответствующей входной шине, объединенные эмиттеры переключающих и базы первых инжектирующих транзисторов соединены с объединенными эмиттерами ннвертнрующих, с базами вторых инжектирующих транзисторов и с шиной нулевого потенциала, коллекторы инвертирующих транзисторов каждого нз кайалов связаны с соответствующим объединением базы а-р-rg и коллектора р-и-р выходных транзисторов, коллекторы переключающих транзисторов каждого из ка:налов соединены с соответствующим объединением базы инвертнрующего и коллекто ра второго инжектирующего транзисторов

-, того же канала и с соответствующим объединением базы а-р- и коллектора р-и-р выхо-. дных транзисторов, причем эмиттеры п-р-и .,и базы р -р выходных транзисторов попарно объединены и соединены с шиной

;нулевого потенциала, а объединенные по-

; Парно коллекторы выходных а-р-Птранзисто ;poa подключены к соответствующей выход,ной шине.

I05()110 входного каскада, содержащего в каждом из двух каналов переключающий и инвертирующийп-р-tz транзисторы с объединеннымежду xaHa aMv эмиттерами а выход 4О ного каскада, содержащего. в каждой из четырех групп lL-ð-и транзисторы и инжектирующие р-и-р транзисторы с объединенными базами, причем коллекторы р-и р транзисторов каждой группы соединены с базой выходногол-р-п транзистора той же группы, а также содержащий шины питания, нулевого потенциала, две входные и четыре выходные шины, при этом коллекторы выходныха-р-птранзисторов каждой группы соединены с соответствующей выходной шиной, а эмиттеры всех инжектирующих р-Фр транзисторов связаны с шиной питания, база переключающего транзистора подключена к коллектору первого инжектирующего транзистора и к соответствующей входной шине, объединенные эмиттеры переключающих и базы первых инжектирующих транзисторов соединены с объединенными эмиттерами инвертирующих и базами вторых инжектирующих транзисторов и с шиной нулевого по

Изобретение относится к вычислительной гехнине и предназначено для использования в качестве одного иэ элементов управления матрицей памяти интегрального запоминающего устройства с произвольной выборкой информа ции, Известны многоканальные дешифраторы, состоящие из входных и выходных дешифрирующих каскадов 11).

Недостатками дешифраторов являются сложность построения, низкая степень интеграции на кристалле и значительное потребле ни е мо щ ности.

Известен также дешифратор, состоящий из симметричного входного каскада, содержащего в каждом из двух каналов переключающий и инвертирующий tE-р-и. транзисторы с объединенными между каналами эмиттерами, и выходного каскада, содержащего в каждой из четырех групп П-р pg транзисторы н инжектирующие р ft-р транзисторы с объединенными базами, причем коллекторы pw-ð транзисторов каждой группы соединены с базой выходного й-рп транзистора той же группы, а также содержащий шины литания, нулевого потенциала, две входные и четыре выходные шины, при этом коллекторы выходных и-р-Птранзисторов каждой группы соединены с соответствующей выходной шиной, а эмиттеры всех инжектирующих р и-р транзисторов связаны с шиной питания !2).

Недостатком его является сравнительно невысокое быстродействие и низкая нагрузочная способность.

Цель изобретения — повышение быстродействия и нагрузочной способности устройства.

Этя цель достигается тем, что в дешифраторе, состоящем из симметричного

I0

35 тенцияля, коллекторы инвертирукнцих тран зисторов каждого из каналов связаны с соответствующим объединением базы П-р-и и коллектора р п.р выходных транзисторов, коллекторы переключающих транзисторов каждого из каналов соединены с соответствующим объединением базы инвертирующего и коллектора второго инжектирующего транзисторов того же канала и с соответствующи м объединением базы и-p-fL H коллектора р rg-р выходных транзисторов, причем эмиттеры tz-р-абазы и базы р-tz-ð выходных тра нэисторов попарно объеди иены и соединены с шиной нулевого потенциала, а объединенные попарно коллекторы выход-. ных П-р-и транзисторов подключены к соответствующей выходной шине.

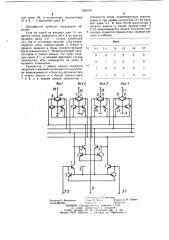

На чертеже показано предлагаемое устройство.

Дешифратор содержит в каждом канале входного каскада переключающий транзистор I, эмиттер которого объединен с базой первого инжектирующего р-fk-ð транзистора 2. База переключающего транзистора 1 объединена с коллектором транзистора 2 и подсоединены к соответствующей входной шине 3-1 и 3-2. Базы первых инжектирующих транзисторов 2 обоих каналов со тинены с эмиттерами транзисторов и подсоединены к объединенным эмитерру и-p rg инвертирующего транзистора 4 и соединенным между собой базам BTophlx инжектирующих р-и-р транзисторов 5 обоих каналов, а также к шине б нулевого потенциала.

Коллектор переключающего транзистора I соединен с базой инвертирующего транзистора 4 и с коллектором второго инжектирующего транзистора 5 того же канала, а также с объединением баз и-р-и транзисторов 7 и 8, и коллекторов р-и-р выходных транзисторов 9 и 10 для левого канала входного каскада и соответственно с объединением баз и-р-и транзисторов 11 и 12 и коллекторов р у-р выходных транзисторов

13 и И для правого канала входного каскада. Эмиттеры первых инжектирующих рС р транзисторов 2 обоих каналов присоединены к шине 15 питания. Коллекторы транзисторов 4 подсоединены к объединениям базп-рЕ и коллекторов р П-р выходных транзисторов 16-19 для левого канала входного каскада и соответственно к объединениям баз П-р-п и коллекторов р-пр выходных транзисторов 20-23 для правого канала входного каскада.

Эмиттеры транзисторов 5, 9, !О, 13, 14, 18, 19, 22 и 23 связаны с шиной 15 питания.

Змиттеры и базы транзисторов 16 и 20, 18 и 22, 7 и Il, 9 и !3, 12 и 17, 14 и 19, 8 и 21, 10 и 23 объединены попарно и подсоединены к шине б нулевого потенциала коллекторы транзисторов 16 и 20 подключены к выходной шине 24, коллекторы транзисторов 7 и 11 — к выходной шине 25, коллекторы транзисторов 12 и 17 — к выход10501!О

Шина

0 1 0 0

0 0 0

1 1 0 1

0 1

0 0

Вых3 бых.2

Вых.9

Состн инте тн Л. Скобелева

Редактор О. Филиппова Тел1гел 11. пер«с Корректор В ярняк

Заказ 846 1 /56 нраж н:и> 11одннсшн

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва. Ж вЂ” 35, Раушская иаб., д. 4/5

Филиал ППП <Патент>, г. Ужгород, ул. Проектная, 4

3 ной шине 26, а коллекторы транзисторов

2l и 8 — — к выходной шине 27.

Дешифратор работает следующим образом.

Если на одной из входных шин 3-1 подается сигнал логического «0», а на другую входную шину 3-2 — сигнал логической

«1», ток от источника питания + Ед инжектируется р-и-р транзисторами 2 левого и правого каналов в базы соответствующих

П-р-Странзисторов 1. Инжектируемый транзистором 2 левого канала ток через вход.ную шину 3-1, к которой приложен сигнал логического <0», замыкается на шину Б нулевого потенциала.

Транзистор 1 левого канала окажется запертым и высокий потенциал его коллектора прикладывается к базе rL-p-дтранзистора

4 левого канала и к базам транзисторов

7 и 8, а в правом канале транзистор 1

4 отпирается током, инжектируемым транэисtopoM 2, при уровне логической <1» на входной шине 3-1. К базе Фр-Г7транэистора 4 правого канала и базам транзисторов l! и 12 прикладывается низкий потенциал коллектора открытого транзистора. Данные сведены в таблицу, 10 3 — 1 3 — 2 24 25 26 27

0 0 1 0 0 0