Делитель частоты с регулируемым коэффициентом деления

Иллюстрации

Показать всеРеферат

ДЕЛИТЕЛЬ ЧАСТОТЫ С РЕГУЛЙРУЮвиМ КОЭФФЩИЕНТСМ ДЕЛЕНИЯ, сЬдеряавдий п д арительный делитель выход которого соединен с входами синхронизации первого и вто рого В -триггеров, с счетными входа |мн лрбГранФШруеА&дх счетчиков импуль сов младших и старших разрядов, выход которого череэ блок опознавание соединен с D пвходом второго D -трнг гера, прямой выход которого подключен к входам начальной установки программируек&ис счетчиков нмпульбов старших и Г4ладших разрядов, выход которого соединен с О -входом первого Р -триггера, инверсиый выход которого подключен к управлякцему входу предварительного делителя частоты , отлич ающийся тем, что, с целью расширения диапазона изменения коэффицнеита деления за счет возможности получ1ения дробных коэффициентов, в иего введен блок nporpai««d, включенный между инверсным выходом второго D -триггера и R-входом первого D -триггера.

СОЮЗ СОЕЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) ГОСУ АРСТВЕННЫЙ КОМИ

Д ТЕТ СССР

AO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИ н автаеанаем ввидитюъатвм =;:,".: -:,,<

-:-Ъ, (ф© 34-57И О/18-21 (23 24.06.82 (46) 36.10.83. Вюл. М 40

° ° ° ° °

22) С.Я.Шишов и Т.С.Райхенберг зЭ) 621; 374 f 088.8) (56 1. Авторское свидетельство СССР

В 601829, кл. Н 03 К 23/02, 1975

2. Pro, minny dh li4s modu Iem рд

3е 99999-,6izenj,primo kifde .))ВСО"SdO lovecl technika", 1976, .т. 24 В 10, с. 367

),54) (57) ДЕЛИТЕЛЬ ЧАСТОТЫ С РЕГУЛИРУЕИЫН КО:-)ФФИцИЕВТОИ ДЕЛЕНИЯ, содерзащий предварительный делитель частоты,. выход которого соединен с-. входами синхронизации первого и вто» рог(й З -триггеров, с счетными входаi ми программируемых счетчиков ийпульcos младших и старших разрядов, выход которого через блок опознавания соединен с В - входом второго 1) -триг. гера, прямой выход которого подключен к входам начальной установки программируемых счетчиков импульсов .старших и младших разрядов, выход которого соединен с Э -входом перво)о D -триггера, инверсный выход хоторого подключен ic управляющему входу предварительного делителя часто-ты, отличающийся тем, что, с целью расширения диапазона изменения коэффициента деления за счет возможности получения дробных ., коэффициентов, в него введен блок программы, включенный мевду инверс- ® ным выходом второго Э -триггера и

R-входом первого Э -триггера.

1051732

Изобретение относится к импульсной технике и автоматике и может быть использовано в аппаратуре обработки цифровой информации.

Известен управляемый делитель частоты, содержащий предварительный делитель частоты с двумя коэффициентами деления, программируемый счет чик, делитель частоты с переменным коэффициентом деления, блок введения единичных приращений, блок управления и управляемый преобразователь параллельного кода в последовательный (блок програюм ) (1) .

Недостатком данного устройства является его сложность вследствие наличия специального блока введения единичных приращений.

Наиболее близким по технической сущности к предлагаемому является делитель частоты с переменным ко-. эффициентом деления, содержащий предварительный делитель частоты, выполненный на четырех D -триггерах и трех логических элементах типа

2И-НЕ, выход которого соединен с входами синхронизации первого и второго 23 -триггеров, со счетным входом программируемого счетчика младших разрядов, выполненного на реверсивном счетчике единиц коэффициента деления, логических элементах

2И-НЕ, 4ИЛЙ-НЕ и инверторе, и со счетным входом программируемого счетчика старших разрядов, пред; ставляющего собой последовательное соединение реверсивных счетчиков де. сятков, сотен, тысяч, десятков тысяч, сотен тысяч коэффициентов дв" ления, выходы которого подключены к входам блока опознавания, выполненного яа четырех логических элементах ИЛИ-НЕ, двух инверторах и . логическом элементе И-НЕ, выходом соединенного с I} -входом второго

В-триггера, прямой выход которого подключен одновременно к входу К -yc тановки первого В -триггера, к входам начальной установки программируемого счетчика старших разрядов и программируемого счетчика мпадаих разрядов, выходом соединенного с

D-входом первого З -триггера, инверсный выход которого подключен к входу управления предварительного делителя.

Причем первый D -триггер необходим в данном устройстве для нормирования задержки, возникающей при формировании сигнала управления коэффициентом деления предварительного делителя, которая не должна превыаать одного такта деления предварительного делителя, что обеспечивает быстродействие всего устройства, равным быстродействию нерегулируемого делителя (2J .

Недостатком известного устройства является невозможность получения нецелого коэффициента деления.

Цель изобретения - расширение диапазона изменения коэффициента деления за счет воэможности получения дробных коэффициентов

Пост авленная цель достигается тем, что в делителе частоты с регулируеьеам коэффициентом вселения, содержащем предварительный делитель частоты, выход которого соединен с входами синхронизации первого и второгоВ -триггеров, со счетными входами программируемых счетчиков импуль15 сов мпадших и старших разрядов, выход которого через блок опознавания соединен cD -входом второго D -триггера, прямой выход которого подключен к входам начальной установки

2р программируемых счетчиков .импульсов старших и младших разрядов, выход которого соединен cD -входом первого 2 -триггера, инверсный выход которого подключен к управляющему входу предварительного делителя частоты,,введен блок программы, включенный .между инверсным выходом второго

Э -триггера и Р -входом первого

Э-триггера.

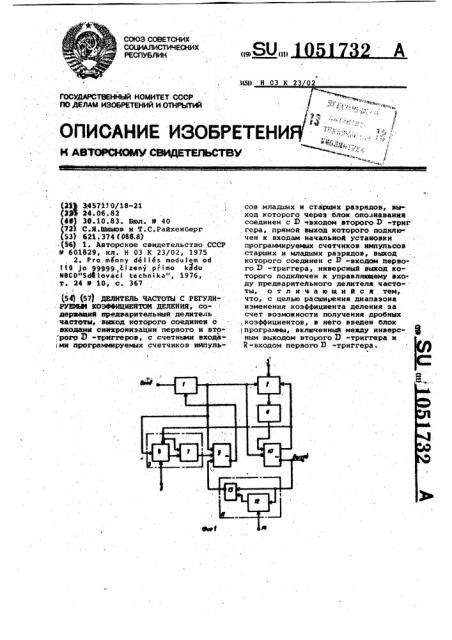

На фиг. 1 приведена структурная электрическая схема предлагаемого делителя частоты с регулируемам коэффициентом деления на фиг. 2 временные диаграмьал, поясняющие работу делителя частоты.

Делитель частоты с регулируемым коэффициентом деления содержит предварительный делитель 1 частоты с коэффициентом деления Е или К+1, программируемый счетчик 2 импульсов

40 старших разрядов, шину 3 ввода параллельного кода управления счетчиком 2, блок 4 опознавания, программируемый счетчик 5 импульсов младших разрядов, состоящий из счетчика б импульсов с предварительной уста" новкой кода и RS -триггера 7, шину

В ввода параллельного кода управления счетчиком 5 импульсов младших разрядов, первый 0 -триггер 9, второй

В-триггер 10, блок 11 программы, состоящий из цифрового накопителя 12 и логического элемента 13 И-НЕ и шину 14 ввода параллельного кода управления блоком 11 программы .

Выход предварительного делителя 1 соединен с входами синхронизации первого и второго Э -триггеров 9 и 10 и со счетными входами счетчиков 2 и 6. Выход счетчика 2 соединен с блоком 4 опознавания, выход которого подключен к D -входу триггера 10, прямой выход которого соединен с входами установки начального кода счетчиков 2 и б и с5 -входом Р5-триггера 7, Инверсный выход второго ходимого количества тактов деления на коэффициент К+1, задаваемого кодом управления младшими разрядами, формирует сигнал, который переключает RS -триггер 7. При этом изменяется информация наЭ -входе первого

2 -триггера 9. По следующему счетному импульсу с выхода предваритель ного делителя 1 первыйЗ -триггер 9 переключается и формируется сигнал на установку в предварительном делителе 1 коэффициента.К. Таким образом, в начале цикла счета счетчик

2 подсчитывает определенное количе» ство тактов деления предварительного делителя 1 с коэффициентом деления К+1. Далее счетчик 2 подсчитывает такты деления предварительного делителя 1 с коэффициентом деления К до окончания цикла. счета счетчика 2. если дробные разряды коэффициента деления не равны нулю, то в некоторых циклах деления, определяемых блоком 11, коэффициент деления всего устройства увеличивается на единицу. Это достигается тем, что блок

11 не пропускает в этих циклах импульс начальной установки наР -вход первого З -триггера 9. При этом переключение первого D -триггера 9 не задерживается на один такт, поэтому длительность сигнала с выхода первого Э -триггера 9 на установку в предварительном делителе 1 коэффициент К+1 увеличивается на один такт. В результате предварительный делитель 1 лишний раз делит частоту входного сигнала на К+1, что увелИчивает коэффициент деления всего устройства на единицу. Порядок распределения циклов деления, в которых коэффициент деления всего устройства увеличивается на единицу, определяется принципом работы цифрового накопителя 12 и кодом К управления дробными разрядами. По каждому выходному импульсу в цифровом накопителе 12 происходит добавление к его содержимому кода К управления дробными разрядами. При переполнении цифрового накопителя 12 иа его выходе формируется логический нуль, который запрещает прохождение импульса начальной установки на R -вход первого Э -триггера 9. Если емкость цифрового накопителя 12 равна И то в К из M циклах деления всего устройства происходит переполнение циФрового накопителя 12. При этом коэффициент деления scего устройства увеличивается на величину, равную

K/M, и дискретность изменения коэффициента деления равна 1/N.

В интервале времени когда происходит Формирование вторым

D-триггером 10 импульса начальной

Q-триггера 10 является выходом всего устройства и, кроме того, соединен с входом синхронизации цифрового накопителя 12 и первым входом логического элемента 13 И-НЕ, второй вход которого подключен к выходу переноса цифрового накопителя 12, а выход соединен с R -входом первого Э -триггера .9. Выход счетчика б соединен с

R-входом@5-Tpprrepa 7, выход которого подключен кЗ -входу первого

Ц-триггера 9, инверсным выходом соединенного с входом управления предварительного делителя 1. Через шины

3, 8 и 14 в счетчики 2 и 6 и цифровой накопитель 12 подается параллель-l5 ный код управления старшими, младшими и дробными разрядами соответственно.

УстройствЬ работает следующим об" разом. 20

Программируемый счетчик 2 подсчи-. тывает количество тактов деления предварительного делителя 1. Количе«

;ство тактов деления определяется ко дом управления старшими разрядами. ,Цикл счета счетчика 2 является цик1 ,лом деления всего устройства. За два такта до окончания цикла счета счетчика 2 блок 4 формирует сигнал, который подготавливает к переключению второй З -триггер 10 по2 -входу.

По следующему счетному импульсу с выхода предварительного делителя 1 эа один такт до окончания цикла счета счетчика 2 второйЭ -триггер 10 переключается Й вырабатывает импульс начальной установки кодов программируемых счетчиков 2 и 5, которые . устанавливаются в начальное состоя» ние. Импульс последнего цикла счета с выхода предварительного делителя 40

1 изменяет состояние счетчиков 2 и . 5 и переключает второй D -триггер

10, тем самым заканчивая импульс. начальной установки. По импульсу начальной установки изменяет свое 45 состояние R5 -триггер 7 и подготавли вает, к переключению первый З -триггер 9 поЗ -входу.

Если дробные разряды коэффициента деления равны нулю, то по импульсу последнего такта цикла счета первый 0-триггер 9 не переключится, < тах как при этом на К -вход первого

D-триггера 9 воздействует импульс начальной установки с выхода блока

1i, который передает его с инверсного выхода второго Э -триггера 10.

Это необходимо потому, что счетчиК б не считает импульс последнего такта цикла счета, поэтому и переключение первого2 -триггера 9 задерживается на один такт. После переклю чения первого D -триггера 9 в предварительном делителе 1 устанавливается коэффициент деления, равный

К+1. Счетчик б после отсчета необ- 45

1051732 установки и первымЭ «триггером 9 сигнала на установку в предварительном делителе 1 коэффициента деления

K+3. и когда счетчики 2 н 6 работают в режиме обратного счета, и младший разряд коэффициента деления равен

3 (Фиг. 2), устройство работает следующим образом.

8 момент времени t t счетчик

2 переходит иэ состояния "три" в состояние "два" (фиг. 2 a}, блок 4 опознавания переключается в состояние логического. нуля «фиг. 28) и втсдойВ триггер 10 подготавливается по Э -входу к переключению. В момент времени t tg счетчик 2 переходит в состояние "один", (фиг. 20) второй Э-триггер 10 переключается в состояние логического нуля по выходу. (фиге 2Ь) )теeà начинается импульс начальной установки, который записывает в счетчик 2 код старших разрядов коэффициента деления, в счетчик

6 - код младшего разряда коэффициен" та деления, равный 3, н переключает

Яб-триггер 7 в состояние логической единицы (фиг.. 2 ), подготавливающий по 0 -входу к переключению первый

О»триггер 9. Следующий счетный импульс с выхода предварительного делителя 1 в момент времени t t4 не может изменить записанного состояния счетчиков 2 и 6, так как в этот момент времени заканчивается импульс начальной установки (фнг. 2Ь) .

Если блок 11 пропускает импульс начальной установки на Я -вход первого

0"триггера9, то в момент времени tt4 первыйР -трйггер 9 заблокирован по

8-входу и переключиться не может (фиг, 28)..В момент времени t счетчики 2 и 6 начинают счет импульсов с выхода предварительного делителя 1 н первыйЭ -триггер 9 по выходу 0, переключается s состояние ло- гического нуля, который устанавлива- р ет в предварительном делителе 1 коэффициент деления, равный К+1. После отсчета счетчиком 6 трех импульсов в момент времени t tg на выходе счетчика 6 формируется импульс фиг. 21), переключающий ЙБ -триггер

s состояние логического нуля (фиг. 20) . Ори этом нервыйЭ -триггер

® 9 подготавливается по Э -входу к переключению, 8 момент времени t t первыйЗ-триггер 9 переключается в состояние логической единицы по вы ходу Ц (фиг. 28) и устанавливает в

15 предварительном делителе 1 коэффициент деления, равный К, Таким образом, три раза в течение цикла де- ления всего устройства в промежутке. времени с ь t « «t> предварительный

2р делитель 1 имеет коэффициент деления, К+1.

Если блок 11 ие пропускает импульс начальной установки и на

Й-вход первогоЭ -триггера 9, то

2 уже в момент времени t t4 первый

9-триггер 9 переключится в состояние логического нуля по выходу н установит в предварительном делителе коэффициент деления, равный

К+1 (фиг. 2®), Далее устройство работает аналогично описанному выше.

8 результате четыре раза в теЧеиие цикла деления всего устройства в промежутке времени .Цс 4 t «((4g предва- рительный делитель 1 имеет коэффициент деления К+1.

Таким образом, введение новых элементов и связей в делителе частоты с переменным коэффициентом деления позволяет уменьшить дискретность изменения коэффициента деления до значений, меньших единицы.

1051732

Составитель М. Фирстова

Редактор М. Янович Техред Т,Иаточка Корректор Л. Патай

Заказ 8687/58 Тираж 936 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4