Устройство для перебора кодов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПЕРЕБОРА КОДОВ , содержащее (h-1)- разрядный двоичный счетчик (п - число разрядов в кодовых комбинациях), счетный . вход которого подключен к входу уст ройства, отличающееся тем, , с целью повышения быстродействия , оно доп олнительно содержит элемент НЕ и коммутаторы, причем вход устройства соединен с первыми управляющими входами, коммутаторов и входом элемента НЕ, выход которого соединен с вторыми управляющими входами коммутаторов, вход устройства является выходом старшего разряда устройства, прямые и инверсные выходы каждого разряда счетчика Соединены с информационными входами cooTBeTctByraaerp кся мутатора, выходы коммутаторов .являются выходами соответствующих младших разрядов, устройства .

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

09) 111) m1) 0 06 F 15/31 ф

ОПИСАНИЕ ИЗОБРЕТЕНИЯ;-

К АВТОРСКОМУ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 34175&0i18-24 (22) 05.04.82 (46) 07.11.83, Бюл. 941 (72) B.Ï. Лачугин и A.IO. Веревкин . (53) 681.3 {088.8) (56) 1. Каган Б.М. Электронные вычислительные системы. N., "Энергия", 1979, с. 92 °

2. филиппов A.Ã., Белкин О.С. Проектирование логических узлов ЭВМ.

М., "Советское радио", 1974, с. 152 (прототйп). (.54)(57):УСТРОЙСТВО,Ц)1Я .ПЕРЕБОРА КО,ЦОБ, содержащее (и-1)- разрядный двоичный счетчик (и — число разрядов s кодовых комбинациях), счетный вход которого подключен к входу уст

t ройства, о т. л и ч а ю щ е е с я тем, чего, с целью повышения быстродействия, оно до)толнительно содержит элемент НЕ и коммутаторы, причем вход устройства:соединен с первыми управляющими входами, коммутаторов и входом элемента HE выход ко- торого соединен с вторыми управляющими входами коммутаторов, вход устройства является выходом старшего разряда устройства, йрямые и. инверсные выходы каждого разряда счетчика соединены с ин@ормационнь)ми входами соответствующего коммутатора,. выходы коммутаторов .являются выходами соответствующих младших разрядов, устрой- © ства. . Е

1053112 р п.(п л

Изобретение относится к автоматике и вычислительной технике и может найти применение в высокопроизводительных вычислительных машинах и системах.

Известно устройство полного перебора всех и-разрядных кодов, представляющее собой двоичный счетчик с .последовательным переносом. Такое устройство позволяет последовательно перебрать все 2" кодовых и;разрядных комбинаций f1) .

Недостатком известного устройства является низкое быстродействие при переборе всех 2" кодов, связанное с тем, что выходной код формируется 15 только после прохождения сигнала переноса по всем разрядам счетчика.

Наиболее .близким к предлагаемому по технической сущности является устройство, содержащее счетчик с па- 2О раллельным переносом, счетный вход которого является входом, а прямые выходы разрядов — выходами устройства (2) .

Недостатком устройства являются большие временные затраты на полный перебор всех 2 кодов. Если время формирования одного кода s счетчике с параллельным переносом определяется выражением ЗО л t < = 4т + "ЧР где ь . - задержка на срабатывание л триггерных схему, - задержка цепей параллельного переноса, . 35 то время, затрачиваемое на полный .перебор всех и-разрядных кодов, ;ойределяется формулой

Во многих практичеСких случаях от счетчика требуется сформировать все 2П возможные и-разрядные кодовые 45 комбинации, причем последовательность их появления не конкретиэирована.

Целью изобретения является повышение быстродействия эа счет уменьшения временных затрат на полный пе ребор всех возможных и-разрядиых кодов.

Поставленная цель достигается тем, что устройство для перебора кодов, содержащее (n-1.)-разрядный двоичный счетчик (и — число разрядов в кодовых комбинациях), счетный вход которого подключен к входу устройства, дополнительно содержит элемент

НЕ и коммутаторы, причем вход устройства соединен с первыми управляю- 6О щими входами коммутаторов и входом элемента HH, выход которого соединен с вторыми управляющими входами комму таторов, вход устройства является выходом старшего разряда устройства, 65 прямые и инверсные выходы каждого разряда счетчика. соединены с информационными входами соответствующего коммутатора, выходы коммутаторов являются выходами соответствующих младших разрядов устройства.

Если вписать 2" кодовых комбинаций, последовательно возникающих на и-разрядном счетчике, то нетрудно заметить, что, взяв первые 2 - ком-. и-< бинаций, поразрядным инвертированием можно получить все остальные. Например, для трехразрядного счетчика

5-6-7-8-кодовые комбинации получаются как инверсии первых четырех:

1. 000

2. 001

3. 010

4. 0111

5 .. 100"

6. 101

7. 310

8. 11 1

Таким образом, для получения всех

2 кодовых комбинаций необходимо сформировать только первые 2 комП-1 бинаций, остальные комбинации будут получены инвертированием первых.

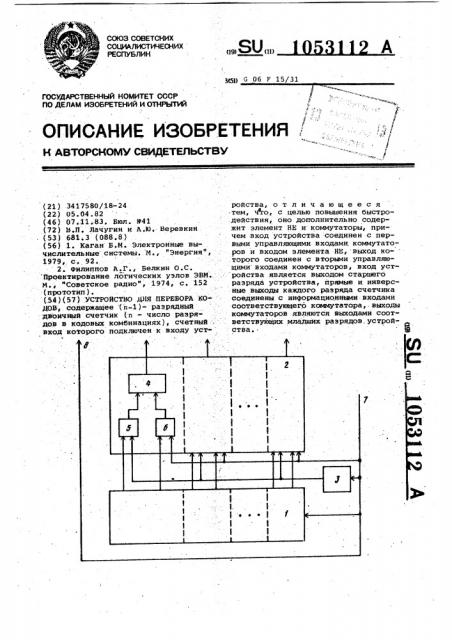

На чертеже представлена структур- ная схема устройства для перебора кодов.

Устройство содержит (и-1)-разрядный двоичный счетчик 1, коммутаторы

2, элемент НЕ 3, элемент ИЛИ 4, элементы И 5 и 6, вход 7 устройства и .выход 8 старшего разряда устройства.

Счетчик 1 предназначен для формирования 2" кодовых комбинаций и имеет прямые и инверсные выходы разрядов. Для определенности будем считать, что прибавление единицы происходит при переходе входного сигнала иэ единицы в нуль. Коммутатор 2 предназначен для передачи прямого или инверсного кода со счетчика на выход устройства в зависимости от управляющего сигнала, единичное значение которого означает передачу инверсного кода. Каждый разряд коммутатора 2 содержит элемент ИЛИ 4, h также элементы И 5 и 6.

Устройство работает следующим образом.

В исходном состоянии счетчик 1 обнулен, входной сигнал отсутствует, единичный сигнал с элемента HE 3 поступает на элементы И 5 всех разрядов коммутаторов 2, и прямой код

00...0 со счетчика 1 через элементы

ИлИ 4 поступает на выход устройства.

С приходом сигнала на вход 7 устройства коммутатор 2 переключается на передачу инверсного кода. Спустя время, определяемое задержкой коммутатора 2 („), через элементы И 6 и

ИЛИ 4 инверсный код 11...1 поступает на выход устройства, причем со1053112 2 (ст "зр "к) "ì °

Ь вЂ”;6) - К

-4Я =<5

q (5Л) к

Ъ !

Составитель В. Кайданов

Редактор Н. Лазаренко Техред Л.Микеш Корректор A. Зимокосов

Заказ 8873/47 Тираж 706

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, .Москва, Ж -35, Раушская наб., д. 4/5

Подп ис ное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 держимое счетчика 1 не изменяется.

Переход входного сигнала иэ .единицы в нуль увеличивает содержимое счетчика 1 на единицу и открывает коммутатор 2 для передачи прямого кода, в результате чего на выходе устройства получается код 00...01. С приходом второго сигнала на вход 7 устройства по"его переднему фронту считывается инверсный код со счетчика

1, т.е. 11...10, а по заднему фрон ту формируется следующий код,. т.е.

00...010 и т.д. Однократный перебор всех кодовых комбинаций заканчивается кодами 01...1 и 100...0.,Пля формирования и-разрядных кодов необхо- 35 дим (и-1)-разрядный счетчик, так как значение старшего и-го разряда перебираемых кодов, снимаемое с выхода 8 устройства, совпадает со значением входного сигнала. Так как 20 формирование асинхронного сигнала окойчания переносов требует значительных .апнаратурных затрат, то на практике на формирование каждого кода отводится одно и то же время с, определяемое максимальным временем переноса. В известном устройстве зто время определяется соотношением

„n и

$) "- l,g + с рр где ст — задержка при срабатывании 30 и триггерных схем; с р — задержка цепей параллельного переноса.

Время, затрачиваемое на полный перебор всех и-разрядных кодов, определяется выражением

35 (ст+ с эр).

В данном устройстве одна половйна и-разрядных кодов формируется эа время ("т "3 где к — задержка коммутатора, а другую половину кодов получают через промежуток времени, определяемый задержкой коммутатора т я и-4 (ль„)

Общее время формирования всех и-разрядных кодов в данном устройстве составляет

Таким образом, в предлагаемом устройстве по сравнению с известным временные затраты на полный перебор уменьшены в К раэ

Т "(л к ""** - "" ã) и-4 1л

Е (pt+ с р+ясс )

Учитывая, что при организации параллельного переноса в счетчике с л и Л

9Р асК, а<, =(l —, ) g получим

Таким образом, предлагаемое устройство обеспечивает повышение быст- родействия.