Цифровой частотный дискриминатор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) 3(5)) Н 03 0 13 00 Н 04 L 27 14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ""-Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbfTMA (21) 3336531/18-09 (22) 10.09.81 (46) 15.11.83. Вюл. М 42 (72) Е.П. Руднев . (53) 621.376.332 (088.8) (56) 1. Авторское свидетельство СССР

9 577698, кл. Н 04 L 27/14, 1976.

2. Патент США В 3660771; кл. 329-104, 02.05.72 (прототип). (54)(57) ЦИФРОВОЙ ЧАСТОТНЫИ ДИСЕРИNHHATOP, содержащий последовательно соединенные усилитель-ограничитель, вход которого является входом дискриминатора, и входной формирователь, последовательно соединенные генератор, делитель частоты и фазовый детектор, о т л и ч а ю щ и йс я тем, что, с целью повыаения точности измерения за счет регулирования частоты и Ширины полосы дискриминации, введены последовательно соединенные первый к второй формирователи одиночного импульса и распределитель импульсов и последовательно соединенные счетчик импульсов, буферный регистр и блок сравнения кодов, второй вход которого является входом цифрового управ-. ления шириной полосы дискриминации, а выход - выходом цифрового частотного дискриминатора, причем делитель частоты выполнен с пере-, менным коэффициентом деления, а фазовый детектор выполнен в виде формирователя импульса счета, пер- вый вход первого и второй вход второго формирователей одиночного импульса соединены с выходом входного формирователя, первый выход первого и выход второго формирователей одиночного импульса соединены соответственно с вторым и треть- им входами формирователя импульса счета, первый и второй выходы которого соединены соответственно с объединенными первым входом распредели-. теля импульсов и входом управления счетчика импульсов и вторым входом распределителя импульсов, третий вход которого является входом на- © чальной установки, выход генерато- е ра соединен с входом синхронизации счетчика импульсов, вход сброса которого, а также второй вход первого формирователя одиночного им-. пульса соединены с первым выходом распределителя импульсов„, второй выход которого соединен с входом разрешения записи буферного регистра, а вход сброса делителя частоты соединен с вторьим выходом первого формирователя одиночного импульса, при этом регулировка частоты дискриминации осуществляется изменением коэффициента деления, делителя частоты.

1054876

Изобретение относится к радиотехнике и может быть использовано в устройствах демодуляции сигналов, а такде для обнаружения наличия работающего канала связи в заранее за- . данной полосе частот. 5

Известен частотный дискриминатор содержащий формирователи, выполненные на логических элементах и пред назначенные для численного определения целых периодов входного сиг- 10 нала, и решающие блоки, предназначенные для последующей обработки результата (11.

Наиболее близким к предлагаемоыу является цифровой частотный дискри- 15 минатор, содержащий последовательно соединенные усилитель-ограничитель, вход которого является входом дискриминатора, и входной,формирователь, последовательно соединенные генератор, делитель частоты и фазовый детектор (2 .

Однако эти частотные дискриминаторы не позволяют регулировать величину полосы дискриминации от некоторой конкретной частоты Х до требуемого значения +М„, а также невозможно регулировать частоту дискриминаций, что приводит к недостаточной точности измерения.

Цель изобретения - повышение точности измерения за счет регулирования частоты и ширины полосы дискриминации., Цель достигается тем, что в цифровой частотный дискриминатор, содержащий последовательно соединенньж усилитель-ограничитель, вход которого является входом дискриминатора, и входной формирователь, последа вательно соединенные генератор, 40 делитель частоты и фазовый детектор, введены последовательно соединенные первый и второй формирователи одиночного импульса; распределитель импульсов и последовательно. соединен. ные счетчик импульсов, буферный регистр и блок сравнения кодов, второй вход которого является входом цифрового управления аириной полосы дискриминации, а выход - выходом цифрового частотного дискриминатора, причем делитель частоты выполнен с переменным коэффициентом деления, а фазовый детектор выполнен в виде формирователя иве ульса счета, первый вход первого и второй вход второго формирователей одиночного импульса соединены с выходом входного Формирователя, первый выход riepsoro и выход второго Формирователей одиноч» ного импульса соединены соатветст- — 6О венна с вторым и третьим входами Формирователя импульса счета, первый и второй выходы которого соединены соответственно с объединенными nep"" вым входом распределителя импульсов 65 и входом управления счетчика импульсов и вторым входом распределителя импульсов, третий вход которого является входом начальной установки, выход генератора соединен с входом синхронизации счетчика импульсов, вход. сброса которого, а также второй вход первого формирователя одиночнаго импульса соединены с первым выходом распределителя импульсов, второй выход которого соединен с входом разрешения записи буферного регистра, а вход сброса делителя частоты соединен с вторым выходом первого формирователя одиночного импульса, при этом регулировка частоты дискриминации осуществляется изменением коэффициента деления делителя частоты.

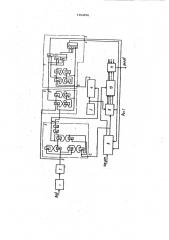

На фиг. 1 приведена структурная электрическая схема предлагаемого дискриминатора; на фиг, 2 — диаграм" мы, поясняющие его работу.

Цифровой частотны9 дискриминатор содержит усилитель-ограничитель 1, входной формирователь 2, генератор

Э, делитель частоты 4, выполненный с переменным коэффициентом деления, первый и второй формирователи 5 и 6 одиночного импульса, фазовый детектор, выполненный в виде Формиро« вателя 7 импульса счета, счетчик

8 импульсов, распределитель 9 импульсов, буферный регистр 10, блок

11 сравнения кодов.

Цифровой частотный дискриминатор работает следующим образом.

Входной синусоидальный сигнал (фиг. 2 а ) поступает на вход усилителя-ограничителя 1, на выходе которого формируется импульсная последовательность (фиг. 2б), сиифаэная входному сигналу. Эта импульсная последовательность поступает на вход входного формирователя

2, с выхода которого импульсы кареткой длительности (Фиг. 2в ), соответствующие передним (задним J фронтам входного сигнала, поступают на тактовые входы формирователей 5 и 6.

Импульс, соответствующий переднему

Фронту входного сигнала, выпеляется формирователем 5 (фиг. 2 г ) на его первом выходе и синхронизирует выходную частоту делители 4 частоты с частотой входного сигнала.

Сигналом со второго выхода Формирователя 5 разрешается работа формирователей 6 и 7. Формирователь 6 выделяет передний фронт следующего импульса с выхода входного формирователя 2 .(Фиг. 2д)(после Фронта входного сигнала, выделенного формирователем 5 ), Импульсы с выхода Формирователя 6 и делителя 4 частоты (Фиг. 2е ) поступают на соответствующие входы формирователя 7, на выходе которого Формируется импульс счета, 1054876 г) . 2

5%1

4,..,6 f 8 2 - Г " п=1

Из приведенного следует, что. ис ключая сравнение определенных разря дов, можно регулировать полосу дискриминацнн устройства. Регулмровку положения полосы дискриминации на оси частот регулируют изменением коэффициента деления делителя 4 частоты.

Используя данные возможности дискриминатора, можно оперативно опрв« делить наличие работающего канала связи на интересующей оператора частоте, либо в интересующем.диапазоне частот, что является одной из важных.нрикладнык задач техники связи. Возможно также использование предлагаемого устройства и для резания задач демодуляции в системах передачи данныс. длительностью, равной модулю разности периодов входного сигнала и сигнала дискриминации, снимаемого с выхода делителя 4 частоты (фиг. 2еР.

Длительность этого импульса просчитывается счетчиком 8 (фиг. 2ж 1 и с 5 помощью первого импульса распределителя 9 (фиг. 2з } записывается в буферный регистр 10. Затем с помощью второго импульса (фиг. 2и )распределителя 9 происходит сброс счетчи- ц) ка 8 и подготовка формирователя 5 для выделения последующего импульса из последовательности, синфазной входному сигналу, и описанный цикл повуоряетоя снова, корректн» руя содержимое буферного регистра

10. Содержимое счетчика 8 в нараллельном двоичном коде с выхода буФерного регистра 10 поступает на блок 11 сравнения, на первый вход которого также в.параллельном двоичном коде поступает код числа, соответствующего нулевому.значвwe. Сигнал íà въищдв схемы сравнения имеет вид - фиг. 2к..

При равенстве частоты входного сигнала и частоты дискриминации (частоты с iaacoga делителя 4 l. фор.мирователь 7 импульса счет не формирует, при этом иа его втором выходе выделяется короткий импульс, поступающий на второй вход распределителя 9. Импульс с первого выхода распределителя 9 переписывает в этом случае из счетчика В в буфер» ный регистр 10 нулевой код, в ос- 35 тальном работа устройства аналогична циклу, описанному ранее.

Содержимое буферного регистра 10 сравнивается с кодом, подаваемиа 46 на блок 11 сравнения (т.е. с ко;дом, соответствующим нулю 1. Регу: лировка полосы дискриминации происходит исключением сравнения определенных разрядов сравниваемого двоичного числа и двоичного нуля.

При сравнении всех разрядов сравниваемых кодов полоса дискримина» ции выроящается в частоту дискриминации f+ . При исключении сравнения младого разряда полоса дис» криминации увеличивается и становится равной

И„=1

К -1 где f — частота опорного генерато ра)

К вЂ” коэффициент деления дели-. теля 4 частоты; прн исключении первых двух разрядов

М2 г 2

К -9 при исключении первых трех разрядов

af

Я

К -49 при исключении первых в разрядов из

1054876

1054876 С of

ЗФ

ЖйР аею g

pOklEN Л

Корректор В. Бутяга

Подлисное

Составитель И. Грабилин

Редактор Н.Кнштулинец Техред И.Иетелева

Ю««ЮЮЮЮ Ю ЮЮ «« Ю««Ю

Закаэ 9117/56 Тираж 936

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий, 113035, Москва, Ж«35, Раушекая наб., д. 4/5

«Ю филиал ППП "Патент", r. Ужгород, ул. Проектная, 4