Устройство для демодуляции двоичных сигналов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ, содержащее блок преобразования входного сигнала , выходы которого подключены к входам блоков обработки сигналов, выходы которого соединены с входами сумматора, выход которого подключен к входу дискриминатора, а также регистр сдвига и блок формирования I двОичньис комбинаций, выходы кото;рый соединены с соответствующими , входами блоков обработки сигналов, о тлич а ю ще е с я тем что, с целью повышения достоверности при воздействии межсимвольной инffepфe ренции , введены регистс : памяти, мажоритарные блоки, коммутатор, распределитель импульсов записи и оперативный регистр, выходы которого подключены к одним входс1м регистров памяти, другие входы и выходы :которых соединены с выходами распределителя импульсов записи и с входгини. мажоритарных блоков, выходы которых подключены к одним входгил коммутатора, другие входы и выход которого соединены соответственно § с выходами распределителя импульсов записи и с входом регистра (Л сдвига, при этом дополнительные выходы блока формирования двоичных .комбинаций подключены к входам опе (ративного регистра, соответствующий вход которого соединен с выходом дискриминатора.

O% <П>

COOS СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(59 Н 04 4 27 22

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИ )

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

j (21) 3447547/18-09 (22) 31.05.82 (46) 15.11.83. Вюл. М 42 (72) В.П.Зайкин и А.Л.Покрасс (71) Куйбышевский электротехнический институт связи (53) 621.394.62(088.8) (56) 1. Авторское свидетельство СССР

9 341170, кл, H 04 В 15/00, 1970.

2. Авторское свидетельство СССР

9 794767, кл. Я 04 (. 27/22р 1979 (прототнп). (54)(57) УСТРОИСТВО ДЛЯ ДЕИОДУЛЯQHH QBOKEHHK СИ1 НАЛОВ, содержащее блок преобразования входного сигнала, выходы которого подключены к . входам блоков обработки сигналов, выходы которого соединены с входами сумматора, выход которого подключен к входу дискриминатора, à .также регистр сдвига и блок формирования ,,: двоичных комбинаций, выходы кото, рый соединены с соответствующщеи входами блоков обработки сигналов, о т л.и ч а ю щ е е с я тем„что, с целью повышения достоверности црн воздействии межсимвольной интерфе: ренции, введены регистры памяти, мажоритарные блоки, коммутатор, распределитель импульсов записи и оперативный регистр, выходы которого подключены к одним входам регист" .ров памяти, другие входы и выходы . которых соединены с выходами распределителя импульсов записи и с . входами. мажоритарных блоков, выходы которых подключены к одним входам коммутатора, другие входы и выход которого соединены соответственно с выходами распределителя импульсов записи и с входом регистра сдвига, при этом дополнительные выходы блока формирования двоичных

;комбинаций подключены к входам опе ративного регистра, соответств1еюций вход которого соединен с выходом дискриминатора.

1054924

Изобретение относится к технике радиосвязи и может использоваться в системах передачи дискретной информации по каналам связи с рассеянием энергии принимаемых сигналов во времени и по частоте.

Известно устройство для демоду:ляции двоичных сигналов, содержащее перемножители, выходы которых соединены через сумматоры с входами вычитающих блоков, первый дополни. тельный сумматор, блок оценки импульсной реакции и линию задержки, вход которой соединен с выходом блока преобразования входного сигнала, второй дополнительный сумматор, выход которого соединен с входом дискриминатора уровня сигнала, регистр сдвига, выходы которого соединены с первыми входами перемножителей (1)

Однако известное устройство имеет низкую достоверность.

Наиболее близким к изобретению по техническому решению является устройство для демодуляции двоичных сигналов, содержащее блок преобра зования входного. сигнала, выходы которого подключены к входам блоков обработки сигналов, выходы которых соединены с входами сумматора, выход которого подклюЧен к входу дискри.минатора, а также регистр сдвига и блок формирования двоичных КОМ6Ннаций, выходы которых соединены с соответствующими"входами блоков обработки сигналов Я .

Однако .это устройство имеет низкую достоверность при воздейтсвии межсимвольной интерференции.

Цель изобретения. — повышение достоверности при воздействии межсимвольной ийтерференции.

Цель достигается тем, что в уст ройство для демодуляции двоичных сигналов, содержащее блок преобразования входного сигнала, выходы которого подключены к входам блоков обработки сигналов, выходы которых соединены с входами сумматора, вы.ход которого подключен к входу . дискриминатора., а также регистр сдвига и блок формирования двоичных комбинаций, выходы которых соединены с соответствующими входами блоков обработки сигналов, введены . регистры памяти, мажоритарные бло-. ки, коммутатор, распределитель им пульсов записи и оперативный регистр, выходы которого подключены к одним входам регистров памяти, другие входы и выходы которых соединены соответственно с выходами распределителя импульсов записи и с вхо.дами мажоритарных блоков, выходы которых подключены к одним входам коммутатора, другие входы и выход которого соединены соответственно ла на интервале Т .

Записываем выражение для любого отсчета ожидаемого сигнала длительностью Т. Для этого вводим обозначения.

Пусть на интервале Т„ передан информационный символ а1 Р 13 тогда любой из остальных М-1 сим-! волов на интервале существования отклика канала длительностью Т> от

1-го символа обозначаем а + - 1, где к - номер посылки на интервале Т, (к 1, 2,...М), например, к=l соот45

50,ветствует элементу а, при к"2, по лучаем элемент а„ +< и т.д., g - - 4-ый отсчет реакции канала на

Ф

МОЮ элементарную посылку (01, N);:

М;„- k -ый отсчет длительностью Т сформированного сигнала на -ом интервале анализа длительностью Т9;

Т,;- интервал длительностью Т на котором сосредоточена вся реакция канала на -ую посылку, т.е. номер интервала анализа

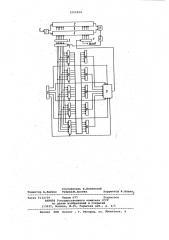

65 соответствует номеру посылки, с выходами распределителя импульсов записи и с входом регистра сдвига, при этом дополнительные выходы блока формирования двоичных комбинаций подключены к входам оперативного регистра, соответствующий вход которого соединен с выходом дискриминатора, На чертеже представлена структурная электрическая схема предла10 гаемого устройства.

Устройство для .демодуляции двоичных сигналов содержит блок 1 преобразования входного сигнала, блоки 2 обработки сигналов, блок 3 формирования двоичных комбинаций, регистр 4 сдвига, сумматор 5, дискриминатор б; оперативный регистр 7, регистры 8 памяти, распределитель 9 импульсов записи, мажоритарные

20 блоки 10 и коммутатор ll °

Устройство работает следующйм образом.

С выхода блока 1 сигнал по каждой компоненте в виде отсчетов 5 длительностью Т поступает на вход соответствующего блока 2 обработки сигналов, где в каждый момент Ту

Имеется М отсчетов сигнала, где М " .память канаЛа М = T>/Т, à T> - длнтельность реакции канала на элементарную посылку. . С выходов блока 3 на другие вхо-. ды соответствующего блока 2 обра;бстки сигналов в течение тактового интервала Т поочередно поступают 2

З5,различных двоичных комбинаций. длины.М.

Из них в блоке 2 на основе отсчетов реакции канала на элементарную посылку формируются все возможные

40 варианты ожидаемого входного сигна1054924. расположенной у правого края этого интервала.

Тогда л

Х к=,с" +к-Е gg л а весь сигнал Х; (вектор сигнала) на,интервале Т>,. х;=(х; .

Перебирай различные наборы а;, у в блоке 3, где жк-1, ф, — ), .блок 2 вулчисляет меру .близости df< между М;,.= Х; Й) Р (Рв 4;2") сформированным в. блоке 2 сигналом и анализируемым входным сигналом )(, f Х Ц на интервале Т, в смысле выбранного критерия. При этом предполагается, что ре.шение о предшествующих элементах . а„ ), где 1, принято достоверно и хранится в регистре 4 сдвига, сигналы из которого поступают в

;блок 2 для необходимых вычислений, Сигналы, ойображающие меру близости div д(Х;„, Х ;), с выходов .. блоков 2 поступают на сумматор 5, где вычисляется общая Мера близости между анализируемым сигналом, на

Т, и и -ым вариантом сформированного сигнала Й„р а, „з(ж„.„,>,, Яа выходе устройства импульс появляется всякий раз, когда сформированный вариант сигнала Е; оказы.— вается наиболее близким (более похо-. жим), на принимаемый сигнал Е:, ло сравнению со всеми ранее сформиро1 ванными на интервале Т) ..

Комбинация символов (ai< ), соот" ветствующая этому веткору2 р, sansсывается в оперативный регистр 7 сигналом с выхода дискриминатора 6„ .т.е. в конце T, интервала обработки в оперативном регистре 7 оказывает:ся записанной комбинация символов

0(р = pa Ä) > соответствующая сигналу Z;» наиболее близкому к принятому сигналу 2, .

Содержимое оперативного регистра 7 в конце i -ro интервала обра-.ботки, представляющее собой проме-. жуточное решение об М символах комбинации (а;, j переписывается в один

ss регистров 8 памяти сигналом с распределителя 9 импульсов записи, где эти промежуточные решения хранятся до вынесения окончательного решения о каждом символе комбинации (a; $ < т.е. в течение М тактовых интервалов T. В конце следующего

:(+1)-го интервала обработки в оперативном регистре 7 записывается комбинация символов о, „ (а;,<+g jj которая очередным сигналом с расПре:делителя 9 импульсов записи перепишется в следующий регистр 8 памяти.

Через М интервалов обработки в ре" гистрах 8 памяти оказывается инфор- мация о переданных символах(a;,a „,..., 4 н - E ph < " <ф м . нм(м-4) ..;a ...а

Предлагаемое устройство принимает

10 окончательное решение об элементе

:0; ж :в конце(+М-1)-го интервала обработки с использованием всех предыдущих И промежуточных решений способом мажоритарного декодирования.

f$:0ñóâ åñòâëÿåòñÿ это мажоритарными блоками 10, подключенными к соответствующим ячейкам регистров 8 памяти.

Так в конце ((+M-1)-го такта обработ.ки окончательное решение выносится об элементе а,, котЬрый хранится на главной диагонали регистров

8 памяти. С выхода соответствующего

:мажоритарного блока, входы которого подключены к ячейкам регистров 8 памяти, окончательное решение об элементе а(„„, через коммутатор 11 подается на вход регистра 4 сдвига. В конце (i +М-1)-го интервала обработки регистр 4 сдвига переписывает это значение а >ж в свою первую ячейку и на следующем интервале обработки только что вычисленное окончательное решение об а„, используется в качестве уже известного символа а, +)(2 . Другие ячей>> ки регистра 4 сдвига также получают

1новое содержание от соседних слева ,ячеек. Выходом всего устройства де;модуляции является первая ячейка регистра 4 сдвига.

46 Каждый такт указанной процеду..ры обработки повторяется.

Синхронность работы устройства !

:.обеспечивает распределитель 9 импульсов записи который, производя за45 пись в соответствующий регистр 8 па-.

;мяти, одновременно подключает ком::мутатор к мажоритарному блоку элемента а ц . Выходы этого мажори,тарного блока соединены с мчейкаgg IMs регистров 8 памяти.

Таким образом преимущество пред, лагаемого. устройства перед известными заключается в повышении досто-,,верности демодуляции без увеличения "времени задержки демодуляции. По"вышение достоверности достигается

:благодаря более полному использованию имеющейся информации о переданных символах на каждом из анализируемых интервалов и тем самым б© :снижается влияние ошибочных решений, полученных ранее. В результате по вышается достоверность передачи

ss@opMagss в системе связи.

1054924 ,Составитель Б.Полянский

Редактор A.Õèì÷óê ТехредМ,Костик, Корректор А.,Ильин

Заказ 9122/59 Тираж 677 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытии

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4