Устройство для нормализации двоичных чисел

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ ДВОИЧНЫХ ЧИСЕЛ, содержащее узел анализа, сдвигатель, регистр порядка, шифратор, причем вход устройства соединен с информационным входом сдвигателя и входом узла анализа, выход шифратора соединен с управлякацим входом одвигателя и -входом регистра порядка, выходы сдвигателя и регистра порядка являются соответственно первым и вторым выходами устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит преобразователь двоичного кода тетрад в код количества нулевых старших разрядов в тетрадах и коммутатор , причем вход узла анализа соединен с входом преобразователя двоичного кода тетрад в код .количества нулевых старших разрядов в тетрадах, выход которого соединен с информацион ным входом коммутатора, управляющий S вход которого соединен с выходом сл шифратора, выход коммутатора соединен с входом регистра порядка и с управлявшим входом сдвигателя, вход шифратора соединен с выходом узла анализа.

СОЮЗ СОВЕТСКИХ . СО14ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) 3(51) G 06 F 7 38

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

OO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3473137/18-24 (22) 02.06. 82 (461 23. 11. 83. Вюл. 9 43 (72) В.С.Возняк, 3.И.Домбровский .и И.A.Äóäà

71 Тернопольский финансово-экономический институт (531 681 ° 33 (088 ° 8) (56 ) 1. Патент Великобритании

Р 1323825, кл. 0 4 А, опублик.

1973.

2. Авторское свидетельство СССР

)) 397908, кл. G 06 F 7/38,. 1973.

3. Авторское свидетельство СССР

М 783792, кл. G 06 F 7/38, 1978 (прототип). (54)(57} УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ ДВОИЧНЫХ ЧИСЕЛ, содержащее узел анализа, сдвигатель, регистр порядка, шифратор, причем вход устройства соединен с информационным входом сдвигателя и входом узла анализа, выход шифратора соединен с управляющим входом одвигателя и

-входом регистра порядка, выходы сдвигателя и регистра порядка являются соответственно первым и вторым выходами устройства, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит преобразователь двоичного кода тетрад в код количества нулевых старших разрядов в тетрадах и коммутатор, причем вход узла анализа соединен с входом преобразователя двоичного кода тетрад в код .количества нулевых старших разрядов в тетрадах, выход которого соединен с информацион ным входом коммутатора, управляющий вход которого соединен с выходом шифратора, выход коммутатора соединен с входом регистра порядка и управляющим входом сдвигателя, вход шифратора соединен с выходом узла анализа.

1056181

55

Изобретение относится к вычислительной технике и может быть использовано при создании высокопроизводительных вычислительных систем.

Известно устройство для нормализации двоичных чисел, содержащее матрицу из элементов памяти, логические элементы И, ИЛИ и выполняющее сдвиг входной информации параллельно на требуемое число разрядов за один такт (1J .

Одна;;.о данное устройство для нормализации двоичных чисел содержит большое количество оборудования.

Известно устройство для нормализации чисел, содержащее последо- 15 вательно соединенные элементы логи", ческих уровней, каждый иэ которых содержит анализаторы содержимого на нуль, дешнфраторы величины сдвига, шифратор и элемент И $2) .

Недостатками этого устройства являются большой объем аппаратурных затрат и зависимость времени выполнения операции нормализации от разрядности нормализуемого числа.

Наиболее близким по технической сущности к изобретению является устройство для нормализации двоичных чисел, содержащее узел анализа, два дешифратора,. два шифратора, два сдвигателя и регистр порядка, при- 30 чем информационный вход первого сдви гателя .соединен с входом узла анализа и входом устройства выход узла анализа соединен с входом первого дешифратора, выход которого соединен З5 с входом первого шифратора, выход которого соединен с входом регистра порядка и управлян.щим входом первого сдвигателя, первый выход которого соединен с информационным входом второго сдвигателя, управляющий вход которого соединен с входом регистра порядка и выходом второго шифратора, вход которого соединен с выходом первого дешифратора, вход которого соединен с вторым выходом первого сдвигателя, выходы второго сдвигателя и регистра порядка являются первым и вторым выходами устройства (3) .

Недостатком данного устройства 50 является невысокое быстродействие.

Цель изобретения — повышение быстродействия устройства для нормализации двоичных чисел.

Поставленная цель достигается тем, что устройство для нормализации двоичных чисел, содержащее узел анализа, сдвигатель, регистр порядка, шифратор, причем вход устройства соединен с информационным входом сдвигателя и входом узла анализа, выход шифратора сообщен с управляющим входом сдвигателя и входом регисхра порядка, выходы сдвигателя и регистра порядка являются соответственно первым и вторым выходами уст- 65 ройства, содержит преобразователь двоичного кода тетрад в код количест* ва нулевых старших разрядов в тетрадах и коммутатор, причем вход узла анализа соединен с входом преобразователя двоичного кода тетрад в код количества нулевых старших разрядов в тетрадах, выход которого соединен с информационным входом коммутатора, управляющий вход которого соединен с выходом шифратора, выход коммутатора соединен с входом регистра порядка и управляющим входом сдвигателя, вход шифратора соединен с выходом узла анализа.

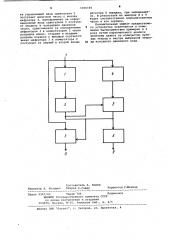

На чертеже приведена схема предлагаемого устройства для нормализации двоичных чисел.

Устройство для нормализации двоич» ных чисел содержит узел 1 анализа, коммутатор 2, шифратор 3, преобразователь 4 двоичного кода тетрад в код количества нулевых старших разрядов в тетрадах, сдвигатель 5, регистр

6 порядка, вход 7, первый и второй выходы 8 и 9 соответственно.

Устройство для нормализации двоичных чисел работает следующим образом.

Пусть на информационный вход 7 поступает П -разрядное двоичное чис О 0 д „Ol „g ... О „. Это iHCJIO IIOCTQ пает на вход узла 1 анализа, где разбивается на Й тетрад, начиная младших разрядов, где и = g q/q t скобки 3 Г означают округление до ближайшего большего числа) . При этом на выходе узла 1 образуется Н -разрядный код, содержащий информацию о тетраде, в .которой находится крайний старший значащий разряд нормализуемого h -разрядного входного двоичного числа. Этот код поступает на вход шифратора 3, который преобразует в нем место расположения старшей значащей тетрады в соответствующее двоичное число, вследствие чего на выходе шифратора 3 будет в соответствии с местом расположения старшей значащей тетрады определенное число.

Вместе с тем входное и -разрядное двоичное число поступает на вход преобразователя 4 в виде расчлененного на К тетрад числа, где преобразуется место расположения крайней справа единицы разряда в соответствующее двухраэрядное двоичное число.

При этом на выходе преобразователя 4 образуется Ц двухраэрядных двоичных чисел, которые поступают на информационный вход коммутатора 2. Одновременно на его управляющий вход поступает двоичное число с выхода шифратора 3. Это число в коммутаторе

2 выделяет только в соответствующей ей тетраде двухразрядное двоичное число, которое поступает на управляющий вход сдвигателя 5. Вместе «е тем

1056181

Составитель А. Клюев

Редактор A. Козориз Техред И.Гайду Корректор С.Шекмар.Заказ 9307/42 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 на управлякщий вход сдвигателя 5 поступает двоичное число с выхода шифратора 3. Одновременно на информационный вход сдвигателя 5 поступает входное п -разрядное двоичное число, сдвиганкаееся на определяемое шифратором 3 и коммутатором 2 число разрядов влево. Старшие и младшие разряды порядка с выходов соответственно шифратора 3 и коммутатора 2 поступают на первый и второй входы регистра 6 порядка, где запоминаются. В результате на выходах В и 9 будет соответственно нормализованное число и его порядок.

Положительный эффект предлагаемо5 ro устройства заключается в повышении быстродействия примерно в 2 раза путем параллельного анализа величины сдвига на количество нулевых тетрад и внутри выбранной тетра1р ды исходного двоичного кода.