Устройство для линеаризации характеристик измерительных преобразователей

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ЛИНЕАРИЗАЦИИ ХАРАКТЕРИСТИК ИЗМЕРИТЕЛЬНЫХ ПРЕОБРАЗОВАТЕЛЕЙ , содержащее блок вычитания и суммирования, счетчик и коммутатор. первый и второй выходы которого соединены соответственно с первьД4 и вторым входами блока вычитания и суммирования , третий вход которого явля ется входом аргумента устройства, а выход подключен к входу счетчика, подсоединенного разрядными выходами к соответствующим информационньм входам коммутатора, отличающееся .тем, что, с целью упрощения устройства, оно содержит оперативный запоминающий блок последовательного действия, вход выборки которого соединен с одним из разрядных выходов счетчика, выходы подключены к соответствующим управляющим входам коммутатора , а информационные входы яв- i ляются входами ввода коэффициентов линеаризации устройства.

(19) (И) .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3Ш 0 06 G 7 26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Р"Рчч,ъ

:/.„-, . " " ъ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ц, " :

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ @Амо q, „

1 (21 ) 3468976/18-24 (22) 12.07.82 (46) 23.11.83, Бюл. )(43 (72) М,Я.Сохрин, В.М.Бурковский, В.Б.Эстеркин, Н.Д.Кабанов и А.Н,Шкамарда (71) Государственное специальное конструкторское бюро теплофизического приборостроения (53) 681,3(088.8) (56) 1. Авторское свидетельство СССР ,М 483674, кл. G 06 I= 15/20, 1973.

2. Авторское свидетельство СССР по заявке )) 3278083/24, кл, .G 06 F 15/20, 1981 (прототип). .(54)(57) УСТРОЙСТВО ДЛЯ ЛИНЕАРИЗАЦИИ

ХАРАКТЕРИСТИК ИЗМЕРИТЕЛЬНЫХ ПРЕОБРАЗОВАТЕЛЕИ, содержащее блок вычитания и суммирования, счетчик и коммутатор, первый и второй выходы которого соединены соответственно с первым и вторым входамИ блока вычитания и сум.мирования, третий вход которого является входом аргумента устройства, а выход подключен к входу счетчика, подсоединенного разрядными выходами к соответствующим информационным входам коммутатора, о т л и ч а ю щ ее с я .тем, что, с целью упрощения устройства, оно содержит оперативный запоминающий блок последовательного действия, вход выборки которого соединен с одним из разрядных выходов счетчика, выходы подключены к соответствующим управляющим входам коммутатора а информационные входы яв- Ф

Ч е ляются входами-ввода коэффициентов линеаризации устройства.

1056220

Изобретение относится к измерительной и вычислительной технике и предназначено для использования в многоканальных измерительных системах с различными типами измерительных преобразователей, имеющими нелиней- 5 ные передаточные характеристики.

Известно устройство для линеаризации характеристик измерительных преобраэбвателей, которое содержит блок вычитания и суммирования импуль- 10 сов, два счетчика, коммутационную матрицу, дешифратор участков аппроксимации и делитель частоты (1 .

Недостатком устройства является то, что оно работает с однотипными измерительными.преобразователями, имеющими одинаковые нелинейные характеристики.

Наиболее близким по технической сущности к изобретению является устройство, содержащее блок вычитания и суммирования, два счетчика, делитель частоты, коммутатор, первый и второй выходы которого соединены соответственно с первым и вторым входами блока вычитания и суммирования, третий вход которого является информационным входом устройства, выход блока вычитания и суммирования сое.динен с входом первого счетчика, первый выход которого соединен с 30 информационным входом коммутатора, второй выход первого счетчика соединен с входом делителя частоты, выход которого подключен к входу второго счетчика, младшие разряды адресного 35 входа постоянного запоминающего блока соединены с выходом второго счетчика, выход постоянного запоминающего блока подключен к управляющему входу коммутатора, старшие разряды адресного 40 входа соединены с управляющим входом устройства.

Недостатком данного устройстВа является относительная сложность и трудность эксплуатации его при замене измерительных преобразователей. 45

Целью изобретения является упрощение устройства °

Поставленная цель достигается тем, что устройство, содержащее блок вычи-50 тания и суммирования, счетчик и коммутатор, первый и второй выходы которого соединены соответственно с первым и вторым в.".одами:, блока вычитания и суммирования, третий вход которого является входом аргумента устройства, а выход подключен к входу счетчика, подсоединенного разрядными выходами к соответствующим информационным входам коммутатора, содержит оперативный запоминающий блок 60 последовательного действия, вход выборки которого соединен с одним из разрядных выходов счетчика, выходы

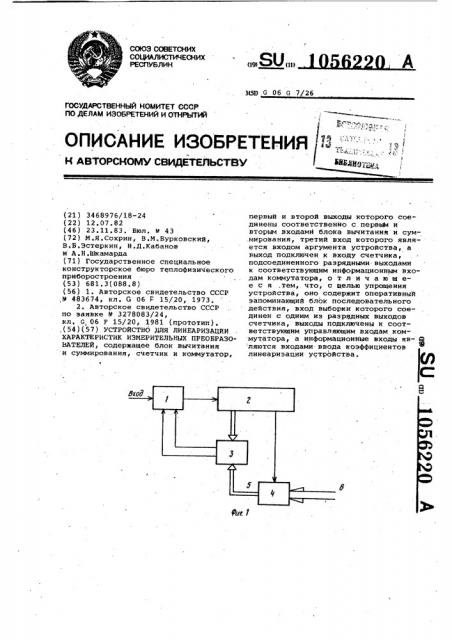

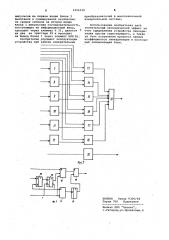

;подключены к соответствующим управля ющим входам коммутатора, а информационные входы являются входами ввода коэффициентов линеаризации устройстВа, На фиг. 1 изображена блок-схема устройства, на фиг. 2 — функциональная схема коммутатора, на фиг. 3 функциональная схема блока вычитания и суммирования.

Устройство (фиг, 1) содержит блок

1 вычитания и суммирования, вход аргумента которого соединен с выходом преобразователя параметра в число импульсов (не показан), а выход с входом счетчика 2. Выходы, счетчика

2 подключены к соответствующим информационным входам коммутатора 3, причем первый и второй выходы коммутатора 3 соединены с первым и вторым входами блока 1 вычитания и суммирования, К одному иэ разрядных выходов счетчика ? подключен вход выборки оперативного запоминающего блока 4 последовательного действия, выход 5 блока 4 соединен с управляющим входом коммутатора. Информационный вход

6 блока 4 соединен с входом ввода коэффициентов линеаризации устройст-. ва.

Коммутатор 3 (фиг. 2) содержит группу диференцирующих цепочек 7-12, входы которых являются информационными входами коммутатора 3. Выходы дифференцирующих цепочек 7-12 подключены к входам элементов И 13-18, вторые входы которых являются управляющими входами. коммутатора 3, Выходы элементов И 13-18 подключены к . входам элемента ИЛИ 19, выход кото.— рого является первым выходом коммутатора 3, Один из управляющих входов коммутатора 3 подключен к буферному усилителю 20. Выход буферного усилителя 20 является вторым выходом коммутатора 3 °

Блок 1 вычитания и суммирования (фиг, 3) содержит элемент И 21, один из входов которого соединен с третьим входом блока 1. К третьему входу блока 1 подключены первый вход элемента

И 22 и тактовый вход триггера 23.

Второй вход элемента И 22 является вторым входом блока 1 вычитания и суммирования, а третий вход элемента

И 22 подключен и прямому выходу триггера 23. Инверсный выход триггера 23 подключен к второму входу элемента

И 21 и входу триггера 24, другой вход которого является первым входом блока 1 вычитания и суммирования.

Прямой выход триггера 24 соединен с входом триггера 23. Выход элемента

И 21 соединен с тактовым входом триггера 25, выход которого соединен с первым входом элемента ИЛИ 26, второй вход которого соединен с выходом элемента И. 22, а выход является выходом блока 1 вычитания:и суммирования.

1056220

50.

60

Устройство работает следующим образом. . В оперативный запоминающий блок 4 последовательного действия заносятся коэффициенты линеаризации для очередного преобразования. Во время преобразования сигнала устройством линеаризации на .вход блока 1 вычитания и суммирования от преобразователя

"параметр — число импульсов" (не показан) поступает последовательность. импульсов. В начале преобразования на выход блока 4 выдается код, соответствующий первому участку кусочнолинейной аппроксимации исходной нелинейности, осуществляемый:данным устройством. Этот код поступает на управляющие входы коммутатора 3. Он разрешает прохождение соответствующего числа импульсов, сформированных на выходах счетчика 2, на входы блока 1 вычитания и суммирования. Это число импульсов добавляется к последовательности импульсов от преобразователя "параметр — число .импульсов" или вычитается из нее на данном участке аппроксимации нелинейной характеристики. В результате на вход счетчика 2 поступает линеаризвванная последовательность импульсов на дан" ном участке аппроксимации. При поступлении на вход счетчика 2 спределенного числа импульсов, соответствующего длине одного участка аппроксимации, на одном из разрядных выходов счетчика 2 вырабатывается импульс, который поступает на вход выборки оперативного запоминающего блока 4 последовательного действия. При этом на выход блока 4 поступает код., соответствующий следующему участку аппроксимации,. и работа устройства нроисходит аналогично работе на пер вом участке аппроксимации.

Разрядный выход счетчика 2, к которому подключен вход выборки блока 4, определяет длину участка аппроксимации, при этом длина участка в масштабе выходного параметра линеаризатора равна 2, где И вЂ” номер разряда н счетчика 2,. к которому подключен вход выборки блока 4.

На информационные входы коммута" тора 3 (фиг. 2) поступают импульсы с выходов счетчика 2. По переходу разрядов счетчика 2 в единичное состояние дифференцирующие цепочки 7-12 вырабатывают импульсы, прохождение которых через элемент И 13-18 на входы элемента ИЛИ 19 и на первый вход коммутатора 3 определяется логическими уровнями на соответствующих управляющих входах коммутатора. При этом число импульсов, которые проходят на первый выход коммутатора 3 эа цикл счетчика 2, равно коду, поступающему на управляющие входы коммута- тора 3. К одному из управляющих входов подключен вход буферного усилителя 20. Уровень сигнала, поступающего с буферного усилителя 20 на второй выход коммутатора 3, определяет, будут ли выходные импульсы коммутатора добавляться к входной последовательности импульсов на блоке 1 вычитания и сумМирования или будут запрецать прохождение соответствующего числа импульсов .входной последовательности,, Блок 1 вычитания и суммирования (фиг. 3) работает следующим образом.

Перед началом работы необходимо установить триггер 23 в нулевое состояние. На вход блока 1, являющийся информационным входом устройства, поступает импульсная последовательность от преобразователя параметра в число импульсов, частота которой

20 делится на два триггером 25 и поступает через элемент ИЛИ 26 на выход блока 1. При поступлении на первый вход блока 1 импульсов с первого выхода коммутатора 3 триггер 24 уста25 навливается в единичное состояние.

Логическая единица, поступающая на вход триггера 23 с выхода триггера

24, разрешает переключение триггера

?3 в единичное состояние. При этом уровень логического нуля, поступающий с инверсного выхода триггера 23 на вход триггера 24, сбрасывает триг.гер 24 в нулевое состояние. При этом . уровень логического нуля, поступающий с инверсного выхода триггера 23 на вход триггера 24, сбрасывает триггер

24 в нулевое состояние, Сформированный на инверсном выходе триггера 23 импульс в течение периода входной частоты запрещает прохождение одного

40 импульса с входа блока 1 через эле мент И 21 на вход триггера 25. Логический уровень на втором входе блока

1 вычитания и суммирования определяет режим работы блока. Если на вто45 ром входе логический нуль (режим

Вычитания), то сформированная на выходе триггера 25 импульсная последовательность через элемент ИЛИ 26 проходит на выход блока 1. Сформированная на выходе блока 1 последовательность соответствует вычитанию одного импульса из входной последовательности импульсов. Если на втором блоке 1 - логическая единица (режим суммирования), то сформированный на прямом выходе триггера 23 импульс разрешает прохождение на выход элемента И 22 одного импульса входной последовательности. Сформированный таким.образом импульс с выхода элемента И 22 поступает на вход элемента ИЛИ 26 и добавляется к импульсной последовательности, сформированной на выходе триггера 25. Полученная импульсная последовательность поступает на выход блока 1. При отсутствии

1056220 импульсов на первом входе блока 1 вычитания и суммирования независимо ох уровня сигнала на втором входе блока 1 импульсная последовательность, поступающая на информационный вход, проходит через элемент И 21, делится на два на триггере 25 и проходит на выход блока 1 через элемент ИЛИ 26, Изобретение упрощает эксплуатацию устройства при замене измерительных преобразователей в многоканальной иэмерительной системе.

Использование изобретения даст значительный. экономический эффект эа счет .удешевления устройства линеариэации против существующего, а также эа счет устранения процесса записи коэффициентов линеаризации в постоянный запоминающий блок.

ВНИИПИ . Закаэ 9306/44

Тираж 706 Подписное

Филиал ППП "Патент", г.Ужгород,ул.Проектная,4