Аналого-цифровой интегратор

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ИНТЕГРАТОР, содержащий интегрирующий усилитель, ключ, аналого-цифровой преобразователь , ..«цифроаналоговый преобразователь/ блок суммирования кодов приращений и формирователь интервалов интегрирования, первый выход которого подключен к стробирующим входам аналого-цифрового и -.Цифроаналогового преобразователей и входу разрешения суммирования блока суммирования кодов приращений, второй вы- . ход формирователя интегралов интегрирования подключен к управляквдем . входу ключа, вход которого является входом интегратора, соединенным с первым входом интегрирующего усилителя , а выход подключен к второму входу интегрирующего усилителя третий вход которого соединен с выходом цифроангалогового . преобразователя , а выход через анашого-цифровой преобразователь подключен.к входу цифроаналогового преобразователя .и первому информационному входу блока суммирования кодов приращений , выход которого является Iвыходом интегратора, отличающийся тем, что,с целью повышения точности интегрирования, в него введены дополнительный аналого-цифровой преобразователь, блок квантования по времени, формирователь импульсов, формирователь сигнала блокировки, первый и второй регистры, блок вычитания, блок элементов ИЛИ-НЕ, элемент НЕ, причем вход блока квантования по времени и вход дополнительного аналого-цифрового преобразователя соединены с входом интегратора, выход дополнительного аналого-цифрового преобразователя подключен к информационным входам первого и второго регист (Л ров, выход блока квантования по времени соединен с входом формирователя импульсрв, выход которого подключен к входам синхронизации дополнительного аналого-цифрового преобразователя, первого регистра и блока суммирования кодов приращений, а также к входу формирователя сигнала блокировки, выход которрго подо ел а 1ключен к входу блокировки второго регистра и к входу элемента НЕ, выход которого подключен к первому входу .блока элементов ИЛИ-НЕ, вторрй ND вход которого соединен с выходом л блока вычитания, а выходы первого и второго регистров подключенысоответственно к первому и вторюму ,входам блока вычитания, выход блока .элементов ИЛИ-НЕ соединен с вторым инфррмацирнным входом блока суммирования кодов приращений.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

3(5 ) С 06 3 1/00ф 6 06 G 7/186

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3484554/18-24 (22) 0508.82 (46) 23.11.83. Бюл, Р 43 (72) П.А. Сависько, А.А, Манько, A.À. Коекин, С-Л. Наугольных, и A,Ã. Зекуненко (53) 681.335(088.8) (56) 1. Авторское свидетельство СССР

9 578645, кл G 06 Л 1/00,. 1976.

1 2. Авторское свидетельство СССР .Р 842867, кл, G 06 J 1/00, 1979 (прототип1 . (54) (57) АНАЛОГО-ЦИФРОВОЙ ИН 1ЕГРА1ОР, содержащий интегрирующий усилитель, ключ, аналого-цифровой преобразователь,,цифроаналоговый преобразователь, блок суммирования кодов приращений и формирователь интервалов интегрирования, первый выход которого подключен к стробирующим входам аналого-цифрового и ",цифроаналогового преобразователей и входу разре- щения суммирования блока суммирования кодов приращений, второй выход формирователя интегралов интег- рирования подключен к управляющему входу ключа, вход которого является входом интегратора, соединенным с первым входом интегрирующего усилителя, а выход подключен к второму входу интегрирующего усилителя, третий вход которого соединен с выходом цифроаналогового. преобразователя, а выход через аналого-цифро вой преобразователь подключен.к входу цифроаналогового преобразователя. и первому информационному входу блока суммирования кодов приращений, выход которого является выходом интегратора, о т л И ч а ю шийся тем, что,с целью повышения точности интегрирования, в него введены дополнительный аналого-цифровой преобразователь, блок квантования по времени, формирователь импульсов, формирователь сигнала блокировки, первый и второй регистры, блок вычитания, блок элементов ИЛИ-НЕ, элемент НЕ, причем вход блока квантования по времени и вход дополнительного аналого-цифрового преобразователя соединены с входом интегратора, выход дополнительного аналого-цифрового преобразователя подключен к информацион - Е а ным входам первого и второго регистров, выход блока квантования по времени соединен с входом формирователя импульсов, выход которого подключен к входам синхронизации дополнительного аналого-цифрового преоб-, - разователя, первого регистра и блока суммирования кодов приращений а также к входу формирователя сигнала блокировки, выход которого под(ключен к входу блокировки второго регистра и к входу элемента НЕ, выход которого подключен к первому входу, блока элементов ИЛИ-НЕ, второй вход которого соединен с выходом блока вычитания, а выходы первого и второго регистров подключены соответственно к первому и второму ,входам блока вычитания, выход блока ,элементов ИЛИ-НЕ соединен с вторым информационным входом блока суммирования кодов приращений.

1056227

Изобретение относится к вычис,лительной технике и .может быть ис- пользовано при проектировании аналого-цифровых вычислительных средств .

Известен интегратор, содержащий блок интегрирования, аналого-цифровой преобразователь (АЦП), цифроаналоговый преобразователь(ЦАП1, блок суммирования кода приращения Щ .

Недостатком данного устройства является низкая точность интегри- 10 рования вследствие периодической помехи, Наиболее близким по технической сущности к предлагаемому изобретению является аналого-цифровой интег- 15 ратор, содержащий ключ, блок интегрирования, АЦП, ЦАП, блок суммирования кодов приращений, формирователь временных интервалов шага интегрирования (2$

Недостатком .известного интегратора является низкая точность интегрирования при воздействии в процессе интегрирования на его вход непериодической помехи, 25

Целью изобретения является повышение точности интегрирования.

Цель достигается тем, что в адаптивный аналого-цифровой интегратор, содержащий интегрирующий усилитель, ключ, аналого-,цифровой преобразо" ватель, цифроаналоговый преобразователь, блок суммирования кодов приращений и формирователь интервалов интегрирования, первый выход которого подключен к стробирующим входам аналого-цифрового и цифроаналогового преобразователей и входу, разрешения суммирования блока суммирования кодов приращений, второй выход формирователя, интервалов ин- 40 тегрирования подключен к управляющему входу ключа, вход которого является входом интегратора, соединенным с первым входом интегрирующего

УРилителя, а выход подключен к вто- 45 рому входу интегрирующего усилителя, третий вход которого соединен с выходом цифроаналогового преобразователя, а выход через аналоговоцифровой преобразователь подключен к входу цифроаналоговОго. преобразователя и первому информационному входу блока суммирования кодов приращений, выход которого является . выходом интегратора, введены дополнительный аналого-цифровой преобразователь, блок квантования по времени, формирователь импульсов,. формирователь- сигнала блокировки, первый и второй регистры, блок вычитания, группа элементов ИЛИ-НЕ, эле- . мент НЕ, причем вход блока квантования по времени и вход дополнительного аналого-цифрового преобразОвателя соединены с входом интегратора, выход дополнительного аналого- 65 цифрового преобразователя подключен к информационному входам первого и второго регистров, выход блока квантования по времени соединен с входом

;формирователя импульсов, выход которого подключен к входам синхронизации дополнительного аналого-цифрового преобразователя, первого регистра и третьему входу блока суммирования,кодов приращений, а также к входу формирователя сигналов блокировки, выход которого подклю" чен к входу блокировки второго регистра и к входу элемента НЕ, выход которого подключен к первому входу блока элементов ИЛИ-НЕ, второй вход которого соединен с выходом блока вычитания, а выходы первого и второго регистров подключены соответственно к первому и второму входам блока вычитания, выход блока элементов ИЛИ-НЕ соединен с вторым -информационным входом блока суммирования кодов приращений.

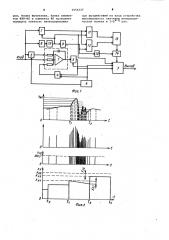

На фиг. 1 представлена схема интегратора; на фиг, 2 — эпюры сиг. налов, поясняющие принцип работы интегратора на фиг 3 — структурная схема блока суммирования кодов приращений

Аналого-циФровой интегратор (фиг. 1) содержит интегрирующий усилйтель 1, ключ,2, аналого-цифровой преобразоьатель (АЦП) 3, цифроаналоговый: преобразователь (ЦАП)

4, блок 5 суммирования кодов приращений,- формирователь 6 интервалов интегрирования, дополнительный аналого-цифровой преобразователь (АЦП) 7, блок 8 квантования по времени, формирователь 9 сигнала блокировки, элемент НЕ 10, первый регистр 11, второй регистр

12, блок 13 вычитания, блок 14 .элементов ИЛИ-НЕ, формирователь

15 импульсов.

Блок 5 суммирования кодов приращений (фиг 3) содержит два блока элементов И 16 и 17, блок элеМентов ИЛИ 18, два элемента И 19, генератор 20 импульсов, элемент

НЕ 21, сумматор 22 и элемент ИЛИ 23.

Интегратор работает следующим образом, При поступлении на вход аналогоцифрового интегратора медленно изменяющегося сигнала без помехи происходит йнтегрирование сигнала на интегрирующем усилителе 1, преобразование выходного сигнала интегрирования в цифровой код аналого-цифровым преобразователем 3, и этот код поступает на вход блока

5 суммирования кодов приращений

При этом на блоке 8 квантования импульсы стробирования отсутствуют, на выходе формирователя сигнала бло кирования 9 вЂ,логический "0", кото1056227

25

40

50

65 рый поступает на входы блока элемен-.. тов ИЛИ-НЕ 14 и тем самим блокирует значение, снимаемое с выхода блока

13 вычитания.

Далее при рассмотрении работы интегратора будем пользоваться графиками (Фиг. 2). При поступлении в момент М., помехи любой амплиту« ды длительностью а2 Т . где | — длительность помехиу

Т вЂ” период импульсов шага ! интегрирования.

На выходе блока 8 квантования появляются импульсы, частота которых прямо пропорциональна скорости изменения входного сигнала, Вид импульсов показан на графике

X8 = X> {Ц, фиг. 2 . Этн импульсы преобразуются Формирователем 15 импульсов и на его выходе имеют вид, показанный на.графике

Х J5 = Хц (Ц Фиг. 2 . Эти импульсы синхронизируют АЦП 7, регистр 11, блок 5 суммирования кодов приращений. Они же поступают на вход формирователя 9 сигнала блокировки, на выходе которого логическая "1" блокирует на регистре 12 последнее значение входного сигнала, поступившего непосредственно перед началом действия помехи.

Эта же логическая "1" преобразуется в логический "0"; который поступает на блок элементов ИЛИ-НЕ, открывая доступ сигнала с выхода блока 13 вычитания на блок 5 суммирования кодов приращений. При этом на регистре 11 фиксируются коды, соответствующие величине смеси сигнал/IIQMexa. Эти коды вычитаются на блоке 13 вычитания, на выходе которого имеем текущие значения помехи, фиксированные с частотой квантования блока

8 квантования. Значения кодов ийвертируются и складываются с кодом,записанным в блоке 5 суммированйя йодов приращений в момент времени t< ., Поясним работу этого блока. На фиг. 3 представлена его структурная,:схема, При поступлении сигнала с формирователя б на вход элемента НЕ 21, являющийся входом разрешения суммирования блока 5 суммирования кодов приращений, импульс формирователя 6 блокирует вход синхронизации и второй информационный вход блока 5, генератор 20 импульсов и поступает на .вход блока элементов И 17, вто рой вход которого является первым информационным входом блока 5 Одновременно происходит считывание и суммирование сумматором 22 значения интеграла с АЦП 3. Во время действия помехи при отсутствии сигнала на входе разрешения суммирования блока 5 суммирования кодов, на егр вход синхронизации поступают импульсы с формирователя 15 импуль . сов. Они поступают на вход блока элементов И 16, на второй вход которого поступают текущие инверти1 рованные значения помехи ° Сложение этих значений с находящейся в сумматоре 22 величиной происходит в, моменты формирования сигналов гене ратора 20 импульсов, частота ,импульсов которого определена временем быстродействия логических элементов. Таким образом, за время от момента tt до из сум,матора 22 вычитается интеграл помехи (на графике Х у = X y (t) фнг, 2 значение Хп„), В момент 6д на сумматор. поступает велйчина интегри-, рования с АЦП 3, но так как в предыдущем такте величина интеграла помехи вычлась заранее, то на выхо-, де блока 5 суммирования кодов приращений Формируется сигнал Х, В случае отсутствия процесса вичйтания интеграла помехи, на выходе блока 5 была бы величина Х (ЯП = Хлт) .

В результате работы аналого-цифро.— вого интегратора на результат интегрирования не влияет помеха. Таким образом, влияние помехи любой амплитуды с длительностью Уп 6 2Т полностью устраняется При этом Т выбирается так, что при максималь-. ной скорости изменения входной функции последующее значение АЦП 3, фиксированное сигналом формирователя б, будет отличаться от предыдущего на единицу младшего разряда АЦП.

Преимуществом изобретения по сравнению с базовым объектом,является повышение точности интегрирования при наличии на входе устройства непериодической помехи .любой амплитуды с длительностью менее двух периодов интегрирования. !

При этом выигрыш в точности интегрирования определяется выражением an + бная ма

С = -------"- = 1 +

Бд San где Sa> — ошибка, обусловленная разрядностью аналогоцифрового преобразователяу оцуп - ошибка, вносимая непериодической помехой.

Таким образом, введение в аналого-цифровой. интегратор дополни.тельного АЦП, блока квантования по времени, формирователя импульсов, формирователя сигнала блокировки первого и второго регист105б227

S ров, блока вычитания, блока элементов ИЛИ-НЕ и элемента НЕ позволяет повысить точность интегрирования при воэдействии на вход устройства максимального эначения непериодиИ -Я. ческой помехи в 1+2 раз.

Xq,Яг, 1056227

Составитель С. Белан

Техред М. Гергель

Редактор В., Иванова

КорректорО. Тигор

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 9309/44 . Тираж 706

ВНИИПИ. Государственного комитета СССР по делам изобретениЯ и открытий

113035, Москва, Ж-35, < Раушская наб ., д. 4/5