Четырехуровневый триггер

Иллюстрации

Показать всеРеферат

ЧЕТЫРЕХУРОВНЕВЫЙ-ТРИГГЕР, содержащий питающий р-п-р транзистор , эмиттер которого соединен с шиной питания, тактирующий п-р-п транзистор , база которого соединена с тактовой шиной, входной п-р-п транзистор , один из коллекторов которого соединен с его базой, блокирующий п-р-п транзистор, коллектор которого соединен с базой входного п-р-п транзистора, а эмиттеры входного п-р-п, блокирукидего п-р-п, тактирукнцего п-р-п и база питающего р-п-р транзисторов соединены с общей шиной/ отличающийся тем, что, с целью повышения степени интеграции и снижения потребляемой мощности триггера он содержит четыре п-р-п транзистора связи и шесть переинжектирующих р-п-р транзисторов. Ъазы которых соединены с общей шиной , эмиттеры п-р-п транзисторов связи соединены с общей шиной, первый коллектор первого п-р-п транзистора связи соединен с его базОй и коллектором первого переинжектирующего р-п-р транзистора и другим коллектором, входного п-р-п транзистора , эмиттеры первого переинжектирующегс р-п-р транзистора соединены с коллекторами второго,третьего , четвертого п-р-п .транзисторов связи и соответствующими коллекторами питающех о р-п-р транзистора, другие коллекторы которого подключены к эмиттерам соответствукяцих переинжектирукадих р-гп-р транзисторов , коллекторы второго, третьего (Л и четвертого из которых соединены с вторым, третьим, четвертым коллекторами первого п-р-п транзистора связи, базами второго, третьего и четвертого п-р-п транзисторов связи и первым, вторым и третьим коллекторами, тактирукяцего п-р-п транзистора, четвертый коллектор которого соединен с эмиттером пятого переинжектирующего р-п-р транзистора , коллектор которого подключен к базе блокирующего п-р-п транзистора, а коллектор шестого переинжектирующего р-п-р транзистора соединен с пятым коллектором первого п-р-п транзистора связи (I является выходом триггера.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

З(51) 0 11 С 11/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

К АВТОРСКОМУ СВИДЕТЕЛЪСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3421198/18-24 .(22) 09.04.82 (4 ) 23.11.83. Бюл. Р 43 (72 ) A.В. Ерохин и M.Ф. Пономарев (71.) Таганрогский радиотехнический институт им; В.Д. Калмыкова

° (53) 681.327.6(088.8) (56 ) 1. Букреев .И.Н. и др. Микроэлектронные схемы цифровых устройств.

М., "Советское радио", 1973.

2. "Transaction on computers", I, v. 12, December, 1977, T Т.Dao, Е.I. McCluskees, L.Ê. Russell, Mueltivalued Integrated Injection Logic (прототип ).(54)(57) ЧЕТЫРЕХУРОВНЕВЫЙ ТРИГГЕР, содержащий питающий р-n-p транзистор, эмиттер которого соединен с шиной питания, тактирующий n-p-n транзистор, база которого соединена с тактовой шиной, входной и-р-и транзистор, один из коллекторов которого соединен с его базой, блокирующий и-р-и транзистор,,коллектор которого соединен с базой входного и-р-и транзистора, а эмиттеры входного n-p-n, блокирующего п-p-n, так: тирующего и-р-и и база питающего р-и-р транзисторов соединены с общей шиной, отличающийся тем, что, с целью повышения степени интеграции и снижения потребляемой мощности триггера,он содержит четыре и-р-и транзистора связи и шесть переинжектирующих р-и-р транзисторов, I (19) (11) оазы которых соединены с общей шиной, эмиттеры и-р-и транзисторов связи соединены с общей шиной, первый коллектор первого и-р-и транзистора связи соединен с его базОй и коллектором первого переинжектирующего р-и-р транзистора и другим коллектором, входного и-p-n транзистора, эмиттеры первого переинжектирующего p-n-p транзистора соединены сколлекторами второго, третьего, четвертого п-р-п,транзисторов связи и соответствующими коллекторами питающего р-и-р транзистора, другие коллекторы которого подключены к эмиттерам соответствующих переинжектирукицих p-.n-p транзисторов, коллекторы второго, третьего и четвертого из которых соединены с вторым, третьим, четвертым коллекторами первого n--p-n транзистора связи, базами второго, третьего и четвертого и-p-n транзисторов связи и первым, вторым и третьим коллекторами. тактирующего и-р-и транзистора, четвертый коллектор которого соединен с эмиттероМ пятого переинжектирующего р-и-р транзистора, коллектор которого подключен к базе блокирующего n-p-n транзистора, а коллектор шестого переинжектирующего р-и-р транзистора соединен с пятым коллектором первого и-р-и транзистора связи ф является выходом триггера.

1056268

Основными недостатками известного триггера являются большая занимаемая площадь на кристалле и потребляемая мощность.

Целью изобретения является повышение степени интеграции и снижение потребляемой мощности.

Поставленная цель достигается тем, что четырехуровневый триггер, содержащий питающий р-п-р транзистор,змиттер которого соединен с шиной питания, тактирующий и-р-и транзистор, база которого соединена с тактовой шиной, входной и-р-и транзистор, один из коллекторов которого соединен с его базой, блокирующий n-p-n транзистор, коллектор которого соединен с базой .входного и-p-n транзистора, а эмиттеры входного n-p-п, блокирующего п-р-п, тактирующего и-р-и и база питающего р-и-р транзисторов соединены с общей шиной, содержит четыре и-р-и транзистора связи и шесть переинжектирующих р-и-р транзисторов, базы которых соединены с общей шиной, эмиттеры и-р-и транзисторов связи соединены с общей шиной, первый коллектор первого и-р-и транзистора связи соединен с его базой и коллектором первого переинжектирующего

p-n-p транзистора и другим коллектором входного n-.p-n транзистора, эмиттеры первого переинжектирующего р-и-р транзистора соединены с коллекторами второго, третьего, четвертого и-р-и транзисторов связи и соответствующими коллекторами питающего р-и-р транзистора, другие коллекторы которого подключены к эмиттерам соответствующих переинжектирующих р-и-р транзисторов, коллекторы второго, третьего и четвертого из которых соединены с вторым, третьим и четвертым коллекторами первого и-р-и транзистора связи, базами второго, третьего и четвертого и-р-и транзисторов связи и первым, вторым и третьим коллекторами тактирующего и-р-и транзистора, четвертый коллектор которого соединен с эмиттером пятого переинжектирующего .p-n-р транзистора, коллектор которого подключен к базе блокирующего и-р-и транзистора, а коллектор шестого переинжектирующего р-и-р транзистора соединен с пятым коллектором первого

n-p-n транзистора связи и является выходом триггера.

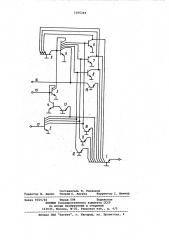

На чертеже представлено предлагаемое устройство.

Четырехуровневый триггер содержит питающий р-и-р транзистор 1, тактирующий и-р-и транзистор 2, входной

Известны многостабильные триггеры: трехстабильный, построенный на трех элементах ИЛИ-ЙЕ, соединенных таким образом, что вход каждого иэ элементов подключен на входы двух 10 других, кроме того, каждый имеет дополнительно два входа, каждый из которых попарно объединяется с аналогичными входами соседних элементов, образуя установочные входы триг- 5 гера; и четырехстабильный,.построенный на элементах И-НЕ, при этом каждый из установочных входов .подключается к входам остальных элементов схемы, исключая элемент, на выходе которого должен формироваться рабочий уровень при подаче установочйого сигнала (1) .

Недостатками многостабильных триггеров такого типа являются сложность, большое количество входных и выходных шин, обусловленное использованием двоичного кода, и сравнительно большая занимаемая площадь.

Наиболее близким по технической сущности к изобретению является четырехуровневый D-триггер. Триггер состоит из кнантизатора и схемы управления. Квантиэатор состоит из первого и-р-и транзистора, один из коллекторон которого соединен с его 35 базой, а остальные три коллектора— с соответствующими базами нторого, третьего и четвертого и-р-и транзисторов, коллекторы которых соединены с соответствующими базами пятого, 40 шестого и седьмого и-р-и транзисторов, один из коллекторов каждого из которых соединен с собственной базой, а два других в две группы: одна— с ныходом, а другаЯ - с базой вось- 45 мого и-р-и транзистора, первый коллектор которого соединен с его базой, а, второй — с базой первого и-р-и транзистора. Схема управления и-р-и транзисто. ра, один иэ коллекторов которого . соединен с его базой, а другой — с базой первого и-р-и транзистора, тактирующего и-p-n. транзистора, один из коллекторов которого соединен с базой восьмого и-р-и транзистора, а другой - c базой блокирующего и-р-и. транзистора, коллектор последнего соединен с базой входного транзистора. Питание осуществляется через р-и-р транзистор-инжектор, ко- 60 тарый задает разные токи в базы и-р-и транзисторов, причем в базы пятого, шестого, седьмого и блокирующего и-р-и транзисторов по 1 кванту тока, в базы первого и вось- g5

Изобретение относится к интегральной электронике, в частности к многостабильным триггерам, предназначенным для использования в вычислительной и измерительной технике. мого — по кванта тока, а в базы второго, третьего и четвертого соответственно 0,5, 1,5 и 2,5 кванта тока f2) .

1056268 и-р-и транзистор 3, блокирующий и-р-и транзистор 4, первый, второй, третий и четвертый и-р-и транзисторы 5 — 8 связи соответственно и шесть переинжектирующих p-n-p транзисторов 9-14.

К входу 15 триггера подключены база и первый коллектор входного и-р-и транзистора 3 и коллектор блокирующего и-р-и транзистора 4. С выходом

16 соединены один из коллекторов и-p-n транзистора 5 связи и коллек- 1О тор переинжектирующего р-n-p транзистора 14. К тактирующегому входу

17 подключена. база тактирующего и-р-и транзистора 2.

Триггер работает следующим образом.

Питающий р-и-р транзистор 1 задает в эмиттеры переинжектирующих и-р-и транзисторов уровни. тока. В эмиттеры лереинжектирующих р-п-р транзисторов

10 и 13 задается уровень тока 0,5 I в эмиттеры р-n-p транзистора 9ток I, в эмиттеры р-и-р транзистора

11 — 1,5 Хр, транзистора 12 - 2,5 транзистора 14 — 3 I . Уровню тока

Io соответствует, найример, ток

100 мкЛ. Это обеспечивается геометрией и взаимным расположением коллекторов транзистора 1.

При подаче импульса тока на вход

17 в зависимости от уровня входного тока 0 Хо 2 I, 3 Io триггер устанавливается в соответствующее соетояние и сохраняет его до появления следующего импульса.

В исходном состоянии на входе 17 отсутствует ток, транзистор 2 закрыт, транзистор 4 открыт базовым током через транзистор 13 и шунтирует вход 15, триггер в одном иэ устойчивых состояний. 40

Если на вход 17 задать ток,транзистор 2 откроется, отведет ток, задаваемый в транзистор 13, транзистор 4 закроется, кроме того,транзистор 2 отведет ток, задаваемый 45 в базы трензисторов 6 — 8, последние, закроются.

При отсутствии тока на входе 15 транзистор 3 закрыт, в базу транзистора 4 через транзистор 9 задает50 ся 3 Io, коллекторы последнего могут отвести такой же ток, поэтому при прекращении импульса тока на входе 17 транзистор 5 отведет базовые токи транзисторов 6 — 8, последние закроются, а в базу транзистора

5 через транзистор 9 задается 3

Триггер в устойчивом состоянии. В выходной шине ток равен нулю, так как ток 3 Х,, задаваемый в транзистор

14, полностью отводится коллектором транзистора 5.

Если на вход 17 задать ток и задать уровень тока Io на вход 15, то коллектор транзистора 3 отведет та, кой же ток от базы транзистора 5, в результате базовый ток последнего равен 3 Io- Io = 2 Хр. При прекращении импульса тока «а вход 17 кол.лекторы транзистора 5 полностью отведут токи, задаваемые в базы транзисторов 6 и 7, и часть тока, зада ваемого в базу транзистора 8. Транзисторы 6 и 7 закроются, а транзистор. 8 откроется и отведет ток одного эмиттера транзистора 9. В базу ,транзистора задается ток 2 Io.Триггер в устойчивомсостоянии, и ток на выходе 16 равен разнице между током коллектора транзистора 14 и коллектора транзистора 5: 3 I, — 2 Io = I .

Если на вход 15 задать уровень тока 2 Io и задан ток на выходе 17, то ток, задаваемый в базу транзистора 5, равен Io, и при прекращении импульса тока йа входе 17 коллекторы транзистора 5 отведут полностью ток базы транзистора 6 и частично токи баз транзисторов 7 и 8, последние откроются, отведут таки двух эмиттеров транзистора 9, и в базу транзистора 5 через тракзистор 9 задается ток Хр. ТриггЕр в устойчивом состоянии, а ток на выходе 16 равен

2Хр .

Если на вход 15 задать уровень тока 3Io и задан ток на входе 17, то ток базы транзистора 5 равен нулю, и при прекращении импульса тока на вход 17 коллекторы транзистора 5 ток не отводят; транзисторы 6 — 8 открыты и отводят токи эмиттеров транзистора 9, в базу транзистора 5 ток не задается, в выходной шине ток равен 3 Io.

Изобретение позволяет в сравнении с известным устройством сократить обобщее число p-n-p и п-р-и транзисторов на 30 и 37% соответственно.

10566268

Составитель B беленков

Редактор В. Данко Техред С. Легеза Корректор С. Шекмар

Заказ 9315/46 Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4