Устройство для резервного энергоснабжения блока микропроцессорной памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ РЕЗЕРВногоэнертхх:НАБ:«Ения влокд МИКРОПРОЦЕССОРНОЙ ПАМЯТИ, с од8ржаще-з первый транзистор типа, эмиттер которого прецназначен цпя поцкпючения к первому источнику питания, второй транзистор р-п-р типа, эмиттер которого предназначен цпя поцкпючения к второму истрчнику питания, а коппектор соединен с коллектором первого транзистора f)-n-p типа, и шиной питания микропроцессорной памяти, цепитепь напряжения, прецназиаченный апя поцкпючения к первому иствчнику питания отличающееся тем, что, с пепью повышения нацежностк и расширения функиионапькых возможноотей , в него ввецены транзистор п-р-« типа , операционный усилитель, стабилитрон, цва циоаа и семь резисторов, причем первый вхоа операционного усилителя соединен с средней точкой ценителя иапр жения, второй вхоа операционного усипитепя соединен с катоцом стабипитрона и через первый резистор прецназначен для подключения к второму источнику питания , аноц стабилитрона соединен с о&щей шиной, выхоц операционного усилителя через первый циоц и второй резистор i соецинен с базой транзистора п-р-п TIPпа ,а через второй диоц и третий резис (Л тор - с базой второго транзистора р-п-р типа, при этом эмиттер транзистос ра п-р-п типа соединен с обшей шиной, коллектор, через четвертый резистор соецинен с базой первого транзистора р-п-р типа, а межцу базой и эмиттером кажцо го транзистора включены соответствен но пятый, шестой и седьмой резисторы. ел at 00 О5 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН. (19) (11) g 1) Н 02 J 9/06

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЦТИЙ

I Ъ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3468495/24-07 (22) 12.07. 82 (46) 23.11.83. Бюл. Хя 43 (72) B. И. Махов и И. Г. Фипьнер (53) 621.316.925.4 (088.8) (56) 1. Бепецкий B. В. Теория и практические метоцы резервирования рациоэпектронной аппаратуры, М., Энергия", 1977, с. 268-270, рис. "4-22.

2. "Эпектроника, % 3, т. 50, 1977, с. 59-60. (54)(57) УСТРОЙСТВО llJIH РЕЗЕРВ НОГО ЭНЕРГОСНАБ)КЕНИЯ БЛОКА МИКРОПРОЦЕССОРНОЙ ПАМЯТИ, содержащее первый транзистор р-н-р типа, эмиттер которого предназначен цпя поцкпючения к первому источнику питания, второй транзистор р-н-р типа, эмиттер которого. предназначен цпя поцкпючения к второму истрчнику питания, а коппектор соединен

3 с коппектором первого транзистора р-и-р типа, и шиной питания микропроцессорной памяти, цепитепь напряжения, прецназначенный цпя поцкпючения к первому истпч« нику питания о т п и ч а ю щ е е с я тем, что, с пепью повышения напежности и расширения функпионапьных возможностей, в него ввецены транзистор и-р-п типа, операционный усипитепь, стабипитрон, пва пиоца и семь резисторов, причем первый вхоц операционного усипитепя соединен с средней. точкой цепитепя напряжения, второй вхоц операционного усипитепя соединен с катоцом стабипитрона и через первый резистор предназначен цпя поцкпючения к второму источнику питания, аноц стабипитрона соецинен с общей шиной, выход операпионного усипитепя через первый пиона и второй резистор соецинен с базой транзистора и-р-п ти па, а через второй пиона и третий резистор - с базой второго транзистора р-п-р типа, при этом эмиттер транзистора п-р-п типа соединен с общей шиной, коппектор. через четвертый резистор соецинен с базой первого транзистора р-п-р типа, а межпу базой и эмиттером каждо го транзистора вкпючены соответствен но пятый, шестой и сецьмой резисторы.

1056363

- Изобретение может быть испопьзовано в преобразоватепях энергии постоянного тока, в частности в источниках питания микропроцессорной памяти.

Известно устройстВо цпя защиты па 5 мяти соцержащее ряц стабипитронов, циоцов и резисторов (1)

Нецостатком известного устройства явпяется повышенный расхоц энергии.

Наибопее бпиэким по технической сущ

:,ности к прецпагаемому явпяется устройство цпя зашиты бпока микропроцессор- ной памяти, соцержащее первый транзис» тор р-п-р типа, эмиттер которого" соеци нен с первым истпчником питания, вто- 15 рой транзистор р п-р типа, эмиттер которого соецинен с вторым источником питания, а коппектор соединен с коннектором пврвого транзистора и шиноч питания ( микропроцессорной памяти„цепитець напря 20 жения поцкпючен к первому источнику пи» тания, база второго транзистора соецинена с средней точкой цепитепя напряжения, база первого транзистора через резистор соединена с вторым источником 25 питания (2J

В известном устройстве при отказе первого источника питания происхоцит автоматическое перекпючение на второй источник питания. При этом вкпючается первый транзистор и вппючается второй. транзистор. Первый транзистор выкпючаеъ. ся, когда напряжение первого источни- ) ка становится меньше, чем. напряжение второго источника, При этом необхоци35 мо учитывать пацение напряжения на перехоце база-эмиттер первого транзистора и на его базовом резисторе. Второй транзистор вкпючается, когда напряжение

40 на срецней точке цепитепя напряжения (по абсопютной величине) становится: бопьше, чем напряжение на его эмиттере. При этом необхоцимо учитывать паде ние kIB перехоце база эмиттер второго транзистора. Ин этого спецует, что выключениР первого транзистора и вкпюченне второго транзистора опрецепяются разными параметрами, разных эпементов.

Поэтому при некотором соотношении нап ряженнй источников питания и вепичин

50 резисторов оба транзистора .могут ока заться выкпюченными ипи же оба транэйстора могут оказаться вкпюченными.

Б первом спучае у потребитепя исчезает напряжение питания. Во втором спучае второй транзистор оказывается открытым I инверсно. И в первом и во втором спучае снижается нацежность устройства.

IleIrk изобретения — повышение падеж» ности и расширение функпионапьныхвозможностей.

Поставпенная цепь цостигается тем, .что в устройство цпя резервного энергоснабжения бпока микропроцессорной памяти, соцержащее первый транзистор р-п-р,. типа, эмиттер которого прецназначен цпя поцкпючения к первому источнику питания, второй транзистор р-и-р типа, эмиттер которого предназначен цпя поцкпючения к второму источнику питания, а коппектор соецинен с коннектором первого транзистора р-п-р типа и шиной пи тания микропроцессорной памяти, цепитепь напряжения, прецназначенный цпя поцкпючения к первому источнику питания, ввецены транзистор п-р-п типа, операционный усипитепь, стабипитрон, цва циоца и семь резисторов, причем первый вхоц операционного усипитепя соецинен с срецней точкой цепитепя напряжения, второй вход операционного уси. питепя соецинен с катоцом стабипитрона и через первый резистор прецназначен цпя покпючения к второму источнику питания, анод стабипитрона соецинен с общей шиной, выхоц операционного усипитепя через первый циоц и второй резистор: соецинен с базой транзистора п-р-п типа, а через второй циоц и третий резистор - с базой второго транзистора типа р-п-р, при этом эмиттер транзистора п-р-и типа соецинен с общей шиной, коппектор через четвертый резистор соецинен с базой первого транзистора р-п-р типа, а межцу базой и эмиттером каж . цого транзистора вкпючены соответственно пятый, шестой и седьмой резисторы.

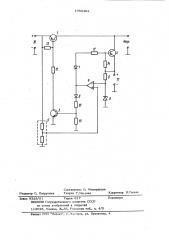

На чертеже прецставпено прецпагаемое устройство, Устройство соцержит первый и второй транзисторы 1,2 р-п-р тина, транзистор 3,; и-р и типа, операционный усипитепь 4, цепитепь 8 напряжения, стабипитрон 6, первый и второй циоцы 7 и 8, с первого по четвертый резисторы 9 - 12 ограничивающие пятый, шестой и седьмой резко торы 13 - 15 резисторы утечки, первый и второй источники 16 и 17 питания, причем первый источник 16 питания соецинен с эмиттером транзистора 1. 1Ыэа первого транзистора 1 соецинена с коппекто ром транзистора 3 через четвертый резистор 1 2,эмиттер транзистора 3 соецинен с об щей Шиной,а его база через второй резистор 10, второй циоц 8 соединена с выхоцом операционного усипитепя 4, выхоц операционного усипитепя 4 через первый циоц 7

3 1056 и третий резистор 11 соединен с базой второго транзистора 2, эмиттер второго транзистора 2 соецинен с вторым источником 17 питания, коппекторы первого и второго транзисторов 1 и 2 поцкпюче- 5 ны к нагрузке, т. е. к шине питания микропроцессорной памяти. Первый источник 16 питания соецинеь с цепитепемб напряжения. Срецняя точка цепитепя 6 соецинена с первым вхоцом операционно- 0 го усипитепя 4,.второй вхоц операционного усипитепя 4 соецинен с катоцом стабипитрона 6, а аноц поспецнэго соецй.,нен с общей шиной, второй источник пйтания через" ограничивающий первый резистор 9 соединен с катоцом стабипи рона 6, межцу базой и эмиттером каж цого из транзисторов 1 - 3 поцкпючены пятый, шестой и сецьмой резисторы утечки 13 - 15 соответственно, питание щ операционного усипитепя 4 произвоцится от источника 17.

Питание операционного усипитепя 4 может быть. осуществпено также через циоцный эпемент ИЛИ, соециненный с источниками 16 и 17

При номинапьных напряжениях первого и второго источника питания устройство работает спецующим образом. Напря жение на первом вхоце операционного усипитепя 4 превышает напряжение на втором егв вхоце. Транзистор 2 окажеч ся закрытым, поскопьку напряжение на выхоце операционного усипитепя 4 равно напряжению питания источника 17, а так> 35 же благоцаря пороговым свойствам ци опа 7 и перехоца база-эмиттер транзистора 2.

При этом провоцящей окажется цепь,состоящая из спецующнх эцементов: выхоц операционного усипитепя 4 - циоц 8 « ® резистор 10 - перехоц база-эмиттер транзистора 3. Транзистор 3 открыт и своим

363 4 коппекторным током через резистор 12 поццерживает открытым и насыщенным транзистор 1. В резупьтате первый источник питания оказывается поцкпюченным к нагрузке через транзистор 1.

При отказе первого источника пита» ния ипи при постепенном уменьшении его напряжения уровень напряжения на пер» вом вхоце операционного усипитепя 4 становится меньше, чем на втором вхоце.

BcqeqcTBHe этого напряжение на выхоце операционного усипитепя 4 скачкообразно уменьшается цо нупя. При этом выкпючается транзистор 3 и тоанзистор 1. Диоц 8 выпопняет ропь порогового эпемента и способствует уцерживанию транзистора 3 в области отсечки коппекторного тока, Оцновременно открывается транзистор 2, . поскопьку появпяется ток в пепи, состоящей из эпементов: перехоц эмиттер-база транзистора 2 - резистор 11-циоц 7выхоц операционногв усипитеця 4. В резупьтате второй источник питания оказывается поцкпюченным к нагрузке через транзистор 2.

Таким образом, при отказе -основного источника питания происхоцит автома тическое перекцючение на резервный исто;ник питания цпя прецотвращения потери информадии, записанной в запоминающем устройстве. При восстановпении основного источника пронсхоцит откпючение резерв ного источника и поцкпючение шины питания микропроцессорной памяти к основ ному источнику.

В устройстве перекпючение транзистэров, коммутирующих источники питания, происхоцит строго согпасованно. Кроме того номинапы напряжений первого и второго источников могут быть выбраны произвопьно ипи же могут изменяться в процессе работы устройства.

1О56363

- Корректор В. Гнрняк

Поцписное

Заказ 9328/51 Тираж 617

ВНИИПИ Госуцарственного комитета СССР по цепам изобретений и откръ1тий

113035, Москва, Ж-35, Раушская наб., ц. 4/5

Фипиап ППП "Патент", г, Унтороц, уп. Проектная, 4

Составитепь О. Мещерякова

Рецахтор С. Патрушева . Техрец Т,Маточка