Вычислительное устройство

Иллюстрации

Показать всеРеферат

1. ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО , содержащее два блока памяти, k умножителей, сумматор и микропрограммный блок управления, причем первый вход устройства соединен с информахшонным входом первоТо блока памяти, выходы которого соединены с первыми входами соответствующих умножителей, выходы сумматора.соединены соответственно с инЛормациоН ными входами второго блока памяти, выходы которого являются выходами устройства и соединены с первой группой информационных входов сумматора , выходы микропрограммного блока управления, с первого по третий, соединены соответственно с управляющими входами первого и второго блоков памяти и сумматора, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит регистр, блок задержки. причем второй вход устройства соединен с информационным входом регистра , выход которого соединен с вторым входом первого умножителя и информационным входом блока задержки , выходы которого с первого по (k-0-й соединены соответственно с вторыми входами умножителей, со второга по k-и, выходы умножителей соединены с второй группой инбормационных входов сумматора, упраллякг111Ие вхо.пм регистра и блока задержки соединены соответственно с четвертым и пятым выходами микропрограммного блока управления. 2. Устройство по п. 1, о т л и3 чающееся тем, что блок за- (Л держки содержит (k-l) групп триггеров по п триггеров в каждой (п-число разрядов, на которое производится умножение), k-2 элемента задержки , элемент И, генератор импульсов, триггер,управления, причем управляющий вход блока задержки соединен ел с установленным входом триггера управления, выход которого соединен с X) первым входом элемента И, второй 1зход которого соединен с выходом генератора импульсов, входы триггеров первой группы соединены с информационным входом блока задержки, выходы триггеров каждой из групп соединены с соответствуюп(им выходом блока задержки и входами триггеров последующей группы, входы синхронизации триггеров групп с первой по (и-2)-ю соединены соответственно с выходами соответствуюршх элементов задержки, выходы каждого из которых соединены с выходом последующего

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) з(Я) 606 F 7

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2 1 ) 3365868/ 1 8-24 (22) 14.1?.81 (46) 30.11.83. Бюл. Р 44 (72) В.В, Валик, В.А. Дядюра, Ю.С. Каневский, В.И. Лозинский и А.В. Пененко (71) Киевский ордена Ленина политехнический институт им.-50-летия Великой Октябрьской социалистической революции и. Украинское производственное геологическое .объединение по геок(зическим работам (53) 681.3?5(088.8) (56) 1. Заявка ФРГ Р 2855722, кл,(06 г 7/52, опублик. 1979, 2, Заявка Японии И - 5?-22218, кл. 6 06 F 7/38, опублик, 1977 (прототип), (54) (57 ) 1 . ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее два блока памяти, умножителей, сумматор и микропро" граммный блок управления, причем первый вход устройства соединен с информационным входом первого блока памяти, выходы которого соединены с первыми входами соответствующих умножителей, выходы сумматора,соединены соответственно с информационными входами второго блока памяти, выходи которого являются выходами устройства и соединены с первой груп- пой информационных входов сумматора, выходы микропрограммного блока управления, с первого по третий, соединены соответственно с управлявщими входами первого и второго блоков памяти и сумматора, о т л ичающее с я тем, что, с целью сокращения аппаратурных затрат, оно содержит регистр, блок задержки, причем втЪрой вход устройства соединен с информационным входом регистра, выход которого соединен с вторым входом первого умножителя и информационным входом блока задержки, выходи которогo с первого по (k-1)-й соединены соответственно с вторыми входами умножителей, со второго, по k -й., виходь умножителей соединены с второй группой информационных входов сумматора, управлявwe входи регистра и блока задержки соединены соответственно с четвертым и пятым выходами микропрограммного блока управления, 2, Угтройство по п. 1, о т л ич а ю щ е е с я тем, что блок задержки содержит {к-1) групп триггеров по и триггеров в каждой (и-число разрядов, на которое производится умножение), k"2 элемента задержки, элемент И, генератор импульсов, триггер, управления, причем управляющий вход блока задержки соединен с установленным входом триггера уп.равления, выход которого соединен с первым входом элемента И, второй

)зход которого соединен с выходом генератора импульсов, входы триггеров первой группы соединены с информационным входом блока задержки, выходи триггеров каждой из групп соединены с соответствующим выходом блока задержки и входами триггеров последующей группы, входы синхронизации триггеров групп с первой ло (k-?)-ю соединены соответственно с выходами соответствующих элементов задержки, выходы каждого из которых соединены с выходом последующего

w z ao элемента задержки, входы синхрониэа- ны с входом (k-2) "го элемента задержции (k-1)-й группы триггеров соедине ки и выходом элемента И.

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных систем.

Известно вычислительное устройст-.

5 во, выполняющее параллельно операции умножения. при вычислении сумм произведений, содержащее"запоминающие блоки множимых и множителей, за110 поминающий блок результатов и сумматоры

Недостатком устройства является низкая производительность при выпол. ненни действий над матрицами, Наиболее близким по технической сущности к предлагаемому является вычислительное устройство, содержащее четыре блока памяти, k умножителей, сумматор и блок управления, причем входы первого и второго блоков памяти являются соответственно первым и вторым входами устройства, выходы первого и второго блоков

6 памяти соединены соответственно с первыми и вторыми входами соответствующих умножителей, выходы которых соединены с соответствующими входами третьего блока памяти, выходы которо го соединены с первой группой входов сумматора, выходы которого соедийены соответственно с входами четвертого блока памяти, выходы которого являются выходами устройства и соединены с второй группой входов сумматора, выходы с первого по пятый 35 блока управления соединены соответственно с управляющими входам первого, второго, третьего и четверто- го блоков памяти, управляющим входом сумматора (2), 40

Недостаток известного устройства - значительные аппаратурние затрати при вычислении суммы векторов, каждый из которых представляет собой 45 произведение симметричной матрицы на соответствующий вектор-столбец,,определяемой следующим выражением:

C„=A 8,tA B t 7АкВк " „В к+ t."„t Ан 8й

С =4Ва+А Вз "+4Вм+Акч Вк. " 1 8 +

° °

Cg=AAg8ggtgtAy„ ggt" +Ам Ви+м-1 где A1, A — элементы векторовстолбцов;

Ь„„,, g, К вЂ” элементы симметричных матриц;

С .,Ск - элементы вектора результата.

Цель изобретения — сокращение аппаратурних затрат при вычислении суммы векторов, каждый из которых представляет произведение симметричной матрицы на соответствующий вектор столбец.

Поставленная цель достигается тем, что вычислительное устройство, содержащее два блока памяти, к умножителей, сумматор и микропрограммный

4 блок управления, причем первый вход устройства соединен с инФормационным входом первого блока памяти, ° выходы которого соединены с первыми входами соответствующих умножителей, выходы сумматора соединены соответ" ственно с информационными входами второго блока памяти, выходы которого являются выходами устройства и соединены с первой группой ин4юрмационных входов :сумматора, выходы микропрограммного блока управления, с первого по .третий, соединены соответственно с управляющими входами первого и второго блоков памяти и сумматора, содержит регистр, блок задержки,.причем второй вход устройства соединен с инАормационным входом регистра., выход которого соединен с вторым входом первого умножителя и индюрмационным входом блока задержки, выходы которого с первого по (k"1)" и соединены соответственно с вторыми:входами умножителей, со второго по k"é, выходы умножителей сое"

3 1057 динены с второй группой инАормацион— ных входов сумматора, управляющие входы регистра и блока задержки соединены соответственно с четвертым и пятым выходами микропрограммного блока управления.

Г пок задержки содержит (k-1) групп по п триггеров в каждой (n-число разрядов, на которое производится умножение), k-2 элемента задержки, 10 элемент И, генератор импульсов, триггер управления, причем управляющий вход блока задержки соединен с уставновленным входом триггера управления, выход к6торого соединен с l5 первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, входы триггеров первой группы соединены с информационным входом блока задержки, выходы 20 триггеров каждой из групп соединены с соответствующим выходом блока задержки и входами триггеров последующей группы, входы синхронизации триггеров групп с первой íî (k-2)-ю сое- 25 динены соответственно с выходами соответствующих элементов задержки, выходы каждого из которых соединены с выходом последующего элемента задержки, входы синхронизации (k-1) -й группы триггеров соединены с входом (k-?)-го элемента задержки и выходом элемента И.

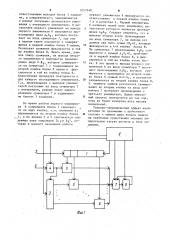

На Аиг. 1 представлена схема вычислительного устройства; на Аиг. 2 .35 схема блока задержки; на Лиг. 3— пример реализации схемы блока управ, ления.

Вычислительное устройство содержит первый блок-1 памяти, первый вход 2 4, устройства, блок 3 задержки, регистр 4, второй вход 5 устройства, умножители 6, сумматор 7, второй блок-8 памяти, микропрограммный блок 9 управления.

Блок 3 задержки содержит тригге-: ры 10 элементы 11 задержки, элеиент И 1?, генератор 13 импульсов, триггер управления 14, Блок 9 содержит блок 15 памяти, регистр 16 адреса, генератор l 7, регистр 18 микро50 команд, дешифратор 19, счетчик 20.

Блок 3 задержки работает следующим образом, Работа осуществляется по тактам, дюрмируемым внутренним генератором 13, Частота следования импульсов с генератора 13 определяет-. .ся временем, необходимым сумматору

940 4

7 для сложения двух чисел, Триггер

14 управления устанавливается во время пуска первого умножителя 6, сбрасывается при приеме всего множителя на 1 "й умножитель 6 llpH условии отсутствия очере) ного запуска первого умножителя. Тактирующие mr"" калы записи в 1, 2. ° ., -2 линейки триггеров образуются на 1, 2..., k-2... k"? элементе задержки соот ветственно, Каждый элемент задержки задерживает тактирующий сигнал на соответствующую группу триггеров на время, необходимое триггерам следующей группы для записи индюрмации.

Йримером блока задержки может служить набор сдвиговых регистров.

Ялок 9 работает следующим образом. В счетчике 20 устанавливается количество тактов работы устройства.

По начальному адресу, установленному в регистре 16 адреса из блока

l5 памяти считывается первая микрокоманда, поступающая на вход регистра 18 микрокоманд. При наличии импульса от генератора 17 осуществляется путем микрокоманды на регистр

18 микрокоманд, откуда микрокоманда поступает на дешифратор 19, выра-. батывающий совокупность управляющих сигналов, Далее под воздействием описанного выше синхроимпульса из содержимого счетчика вычитается единица. На второй вход регистра 16 адреса с выхода регистра микрокоманд поступает адрес следующей микрокоманды. Процесс продолжается до тех пор пока счетчик 20 не установится на нуль.

Вычислительное устройство работает следующим образом.

В исходном состоянии блок 1, регистр 4, блок 3 задержки и блок 8 обнулены, По входу 2 на вход блока 1 подается множимое А1, а на вход регистра 4 по входу 5 — множитель В1. После того, как множимое и множитель заАиксируются соответственно в первой ячейке блока 1 и регистре 4, начинает работать первый умнояитель 6, а содержимое регистра 4 поступает на блок 3 задержки, в котором задержка между двумя последовательными выходами определяется временем, необходимым для работы сумматора 7, на такое же время задерживается и пуск . каждого очередного умножителя, связанного с со1057940, Во время работы первого умножителя 6 содержимое блока 1 сдвигаетФ ся на одну ячейку, т, е. множимое А1 перемещается во вторую ячейку- блока 30 ,1, а по входам 2 и 5 считывается следующая пар а опер андо в (А 2 и В 2), ко1 торая к моменту окончания работы ответствующим выходом блока 3 задерж ки, а следовательно, задерживается и момент получения результатов умно-. жения с очередного умножителя, Б результате первого умножения на выходе первого умножителя 6 получается прсизведение вида А В, которое поступает на вход сумматора 7, где оно в первом такте слагается с содержащимся в первой ячейке блока 8 нулем.

Результат сложения фиксируется в той же ячейке блока 8. Через время, равное такту слбжения, на выходе второго умножителя 6 получается произведение вида О-В1, которое суммируется на сумматоре 7 с содержащимся во второй ячейке блока 8 нулем и фиксируется в той же ячейке блока 8.

Аналогичная процедура повторяется и для каждого последующего умножителя, Т.е. произведения с выходов умножителей поступают на вход сумматора 7 с интервалом, равным циклу одного сложения сумматора 7 и задаваемому блоком 3 задержки, первого умножителя 6 фиксируется соответственно в первой ячейке блока

1 и в регистре 4, Первый умножитель

6 начинает новый цикл умножения, ре5 зультатом которого является произведение А2В2. Следует отметить, что к моменту подачи этого произведения на вход сумматора 7 на выходе его должна уже быть сумма ОВ +О, которая

10 фиксируется в k-й ячейке блока 8.

На сумматоре 7 произведение А В сум2 7 мируется с суммой А1В +О, хранящейся в первой ячейке блока 8, и фиксируются в той же ячейке этого бло15 ка. В это время с выхода второго умножителя 6 на вход сумматора 7 поступает произведение А В, . которое сум— мируется с хранящейся во второй ячейке блока Я суммой 0+0 В, и результат запоминается во второй ячейке блока 8, К моменту записи результата суммирования во вторую ячейку на вход сумматора 7 поступает произведение с третьего умножителя, Далее описанный процесс повторяется до тех пор, пока не будет исчерпан весь массив множителей.

Технико-экономический эффект изобретения по сравнению с прототипом состоит н замене двух блоков памяти на требую|чие существенно меньших аппаратурных затрат регистр и блок задержки.

1057940

1057940

Составитель А. Клюев

Редактор С. 1Оско Техоед С.Легеза Комлектов И. Эрдели

Заказ 9464/51 Тираж 706 Подписное

ВН1ПО1И Государственного комитета СССР по делам изобретений и открытий

113035 Москва _#_<-35 ???????????????? ??????, ??. 4>

Л.

Филиал ППП "Латеит", г. Ужгород, ул. Проектная, 4