Запоминающее устройство

Иллюстрации

Показать всеРеферат

:ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель информации, первый ограничительный элемент на диоде, адресные блоки, входы которых являются адресными входами устройства , .одни выходы адресных блоков соединены с адресными входами накопителя информации, входы разрешения выборки и записи-считывания которого являются соответствующими входами устройства, первый выход накопителя информации подключен к катоду диода, другие выходы адресных блоков и второй выход накопителя информации подключены к одной шине питания, о тличающееся тем, что, с целью упрощения и повЕлиения быстродействия , оно содержит выпрямитель на стабилитроне, второй ограничительный элемент на резисторе и блок элементов И-НЕ, одни входы которого подключены к третьему выходу накопителя информации, другие входы блока элементов И-НЕ являются входом разрешения считывания устройства, а выходы соединены с информационными входами накопителя информации и О 9 являются информационными выходами устройства, катод стабилитрона сое (Л динен с катодом диода, а анод - с .другой шиной питания, один вывод резистора подключен к входу разрешения выборки накопителя информации, а другой - к одной шине питания.

(1Е (И) СОЮЗ СОВЕТСНИХ

РЕСПУБЛИН

3 G 11 С 17 00

ПО ДЕЛАМ ИЗОБРЕТЕНИИ И ОТНРЬГГИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н AETGPC!!OMV !ВИДЕТЕ/ЯСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР (21) 3239214/18-24 (22) 26.01.81 (46) 30;11.83. Бюл. 9 44 .(72) Ю.Я.Берсон, Е,Я.Марголин и B.È.Øàãóëèí (53) 681.327.6(088.8) .(56) 1. Особенности построения ППЗУэ на КИОТ ИС, — Сборник "Конструирование и производство запоминающих устройств". Материалы семинара. Л., 1980, с. 50.

2. Микросхемы интегральные.

ОСТ 11340-79, .с. 185-189 (прототип). (54)(57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель информации, первый ограничительный элемент на . диоде, адресные блоки, входы которых являются адресными входами устройст-. ва, .одни выходн адресных блоков соединены с адресными входами накопителя информации, входы разрешения выборки и записи-считывания которого являются соответствующими входами устройства, первый выход накопителя информации подключен к катоду диода, другие выходы адресных блоков и второй выход накопителя информации подключены к одной шине питания, о тл и ч а ю щ е е с я тем, что, с целью упрощения и повышения быстродействия, оно содержит выпрямитель на стабилитроне, второй ограничительный элемент на резисторе и блок элементов И-НЕ, одни входы которого подключены к третьему выходу накопителя информации, другие входы блока элементов И-НЕ являются входом разрешения считывания устройства, а выходы соединены с информационными входами накопителя информации и С2 являются .информационными выходами устройства, катод стабилитрона соединен с катодом диода, а анод - с ,другой шиной питания, один вывод . резистора подключен к входу разрешения выборки накопителя информации, а другой — к одной шине питания. !

1057990 1

Изобретение относится к вычисли тельной технике и дискретной автоматике, и может быть использовано в качестве перепрограммируемого постоянного запоминающего устройства (ППЗУ), например имитатора однократ- 5 нопрограммируемых ПЗУ, или в качестве энергонезависимого оперативного запоминающего устройства (ОЗУэ).

Известны ЗУ с сохранением информации при отключейии питания, содер- Я жащие источник автономного питания (аккумулятор, батарея элементов) и обеспечивающие неограниченное число циклов перезаписи. Такие ЗУ имеют один номинал питания удобнее при 15 записи информации, чем, на ример, ЗУ на энергонезависимых интегральных микросхемах, и поэтому в ольшей степени удовлетворяют условиям построения ППЗУ иди ОЗУэ Щ и (2) .

Требования, предъявляемые к ППЗУ (имитатор ПЗУ): высокое быстродействие в режиме считывания, обеспечение оперативного режима занесения информации, полнЬя конструктивная и функциональная совместимость с имити- 25 руемым устройством, хранение информации.в течение длительного времени, .высокая нагрузочная способность по выходу — являются более жесткими, чем требования к ОЗУэ, и поэтому 30 решение вопроса построения имитатора

ПЗУ делает очевидной реализацию более простых вариантов.

Известные ЗУ характеризуются низким быстродействием и малой нагру- З5 зочной способностью, связанные с использованием маломощных БИС памяти с целью уменьшения энергопотребления от батарейного источника, а также сложностью ЗУ, обусловленной наличи-. ем нескольких последовательных элементов в батарее и дополнительного разъема для ввода информации в режи- ме записи.

Наиболее близким по технической сущности к предлагаемому является

ЗУ, содержащее ОЗУ с информационными входами и выходами, адресные буферные схемы, контакты питания которых соединены с автономным источником питания и через диод - с клеммой 50 питания ЗУ., которая связана с фильтром питания (конденсатором) (2) . !

Ъ

Известное устройство обеспечивает хранение информации при отключении питания и удобно, при занесении информации, однако обладает недостатками, которые затрудняют его использование в качестве имитатора ПЗУ: сложность и большие габариты из-за наличия фильтра питания, большого 60 числа элементов источника автономного питания, большого числа контактов разъема, занятых под входные и выходные сигналы, недостаточно высокое быстродействие в режиме считы- gg вания из-за особенностей временной диаграммы БИС накопителя и медленныМ адресных буферных схем.

Кроме того, в устройстве низка нагруэочная способность информационных выходов и повышено потребление мощности в режиме хранения иэ-за подключенных к автономному источнику. буферных схем.

Цель изобретения — упрощение устройства и повышение его быстродействия.

Поставленная цель достигается тем, что запоминающее устройство, содержащее накопитель информации, первый ограничительный элемент на диоде., адресные блоки, входы которых являются адресными входами устройства, одни выходы адресных блоков соединены с адресными входами накопителя информации, выходы разрешения выборки и записи - считывания которого являются соответствующими входами устройства, первый выход накопителя информации подключен к катоду диода, другие выходы адресных блоков и второй выход накопителя информации подключены к одной шине питания, содержит выпрямитель на стабилитроне, второй ограничительный элемент на резисторе и блок элементов И-НЕ, одни входы которого подключены к третьему выходу накопителя информации, другие входы блока элементов И-НЕ являются входом разрешения считывания устройства, а выходы соединены с информационными входами накопителя информации и являются информационными выходами устройства, катод стабилитрона соединен с катоцом диода, анод - с другой.шиной питания, один выход резистора подключен к входу разрешения выборки накоцителя информации, а другой — к одной. шине питания.

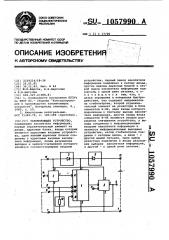

На чертеже представлена блок-схема ЗУ.

Адресные входы накопителя 1 информации соединены с выходами адресных блоков 2,.информационные выходы — с входами блока 3 элементов И-НЕ, выходы которого соединены с информациониым входом накопителя 1 и являются информационными выходами

4 устройства ° Первый выход накопителя (контакт питания) соединен с катодами диода 5 и стабилитрона 6, второй выход накопителя 1 и вторые выходы адресных блоков 2 и блоков 3

{контакты питания) соединены с общей шиной 7. Входы разрешения выборки и записи-считывания накопителя 1 являются вхбдами соответственно 8 разрешения выборки и 9 режима работы. устройства. Выход 8 разрешения выборки соединен через резистор 10 с шиной 7. Вторые входы блока 3 элемен1057990 тов И-НЕ являются входом 11 разреше-: дом накопителя 1, не влияют íà его ния считывания устройства. рабочим так как запись в накопитель

Аноды диода 5 и стабилитрона 6 - запрещена потенциалами на входах 8 подключены соответственно к шинам 12 и 9, (В этом режиме аккумулятор поди 13 питания..Входы адресных. блоков 2 заряжается через диод 5 и стабилит- являются адресными входами 14 уст- 5 рон-6, обеспечивая одновременно ройства, с шиной 12 которого соеди- фильтрацию возвожных выбросов в иены третьи выходы (контакты пита- цепях питания). ния) адресных блоков 2 и блока 3 При работе устройства в качестве элементов И-НЕ. ОЗУ с сохранением информации на вход

На шины 12 и 7 подают - татное щ 8 подают импульсы выборки. Запись в питание, на шине 13 и 7 подают пита- ОЗУ производится через выходы 4 по ние от автономного источника (акку- выбранному адресу при высоком уровмулятора). не сигнала на входе 9 и низком — на

Принцип работы устройства состоит входе 11. Считывание информации пров следующем. изводится через выход 4 при низком В режиме записи питание блоков 2 уровне сигнала на входе 9 и высоком и 3 осуществляется через шины 12 и на входе 11. При отключении пита7,питание накопителя — через те же ния накопитель 1 переводится в режим шины и диод 5 (в этом режиме так- хранения с питанием от аккумялятора же происходит подзарядка аккумуля- при минимальном потреблении энергии тора через диод 5 и стабилитрон 6). 2О благодаря низкому уровню напряжения

На входы 8 и 9 подают соответственно на входе 8, обеспечиваемому с помосигналы разрешения выборки и режима . щью резистора 10. работы, на вход 11 подают эапрещаю- Технико-экономическая эффективщий потенциал. Элементы И-НЕ блока 3 ность устройства, по сравнению с закрыты и не препятствуют записи ин- 25 прототипом, заключается в упрощении формации через выходы 4 в накопитель за счет: уменьшения числа контактов, 1 по адресу, код которого поступает необходимых для вхОдных информацйонна адресные. входы накопителя с ад- ных сигналов и сигналов, обеспечиваресных входов 14 через блоки 2. ющих режим записи, что позволяет

В режиме хранения при отключении 3O отказаться от дополнительного раэъевнешнего источника питание накопите- ма; уменьшение числа элементов питаля 1 осуществляется с помощью стаби- ния автономного источника, так как литрона 6 (череэ шину 13 от аккуму - в режиме хранения БИС памяти требуют лятора). меньшего напряжения питания, а буферНа входе 8 разрешения выборки у5 ные схемы отключены (в режиме обращечерез резистор 10 поддерживается ния стабилитрон компенсирует разнинулевой потенциал, переводящий нако цу между рабочим, напряжением и наппитель 1 в режим хранения с малым . ряжением хранения); отказа от конпотреблением энергии. Блоки 2 и 3 денсаторов фильтров питания, так обесточены благодаря диоду 5 и не как фильтрация осуществляется через потребляют энергии. цепь стабилитрона.

В режиме считывания (при работе Повышение быстродействия в предла- в качестве имитатора ПЗУ входы 8 и гаемом устройстве заключается в

9 устройства разведены на контакты организации работы накопителя в режиразъема, которые в штатном ПЗУ нахо- . -ме постоянной выборки и, следовательдятся под постоянным потенциалом: 45. но, отказа от лишних тактов задержки, ll+ lt

Н И

+ или 0 питания. Это, как прави- а также в использовании более ло, запараллеленные контакты питания, быстродействующих буферных схем. которые в имитаторе распараллелены) Кроме того, устройство позволяет накопитель 1 получает питание через повысить нагрузочную способность шины 12,7 и диод 5, блоки 2 и 3 . 59 выходов и уменьшить потребляемую через шины 12, 7. Наличие соответ- от источника автономного питания ствующих потенциалов на входах 8 мощность. и 9 устройства обеспечивает режйм Реализация признаков изобретения считывания накопителя 1. Информация, позволяет уменьшить габариты, упросэаписанная в накопитель 1 и соответ- 55 тить устройство, повйсить его быстроствующая коду адреса поданному с вхо- действие и нагрузочную способность, дов 14 через блок 2 на адресные входы сохранить функциональное назначение .накопителя 1, считывается с выхода 4 контактов. разъема, т.е. решить запри подаче на вход 11 сигнала разреша- дачу конструктивной и функциональной ющего считывание. Сигналы на выходе :имитации ПЗУ а также построения

4, соединенном с информационным sxo- ПНЗУ и ОЗУ с сохранением информации.

68

ВНИИПИ Заказ 9586/53 Тираж 594 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4