Высоковольтное логическое устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК цд) Н 03 К 19/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3450381/18-21 (22) 07.06.-82 (46) 30.11.83. Бюл. Ю 44 (72) В.И. Громов, Б.А. Гарбуз, О.Е. Хочинов, Р.Е. Богуславский, В.А, Бедно. и П.И. Салкаэян (ДЗ) 621.374(088.8) (56).1. Digits,I Integrated Circuit.

Data Book, ЯргeIura company, 1973, р. 323, ig. 604-432.

2 . Fugusu 1978, т. 29, 9 4, с. 139-142; MB 481 (прототип). (54)(57) ВЫСОКОВОЛЬТНОЕ ЛОГИЧЕСКОЕ

УСТРОЙСТВО,: содержащее входной элемент И, фазорасщеплякщий транзис тор первого типа проводимооти, коллектор которого через резистор соединен с шиной низковольтного источника питания, а база - с выходом вкодного элемента И, и высоковольтный сложный инвертор на двух транзисторах первого типа проводивюсти, база первого из которых соединена через развязывак фий диод с эмиттером фазорасщепляющего тран» эистора, о т л и ч а ю щ е е..с ф. тем, что, с целью исключения пот„„SU„„1058060 А ребления мощности от высоковольтного источника питания в состоянии низкого уровня выходного сигнала и увеличения быстродействия, в него дополнительно введены отражатель тока на двух транзисторах первого типа проводимости и двух диодах смещения, и транзистор второго типа . проводимости, причем коллектор фазорасщепляющего транзистора соединен с базой первого транзистора от- ражателя тока, эмиттер которого через первый и второй диоды смещения подключен к базе второго транзис .тора отражателя тока, эмиттер которого соединен с общей шиной и через реэистор - с его базой, а коллектор I подключен к базе первого транзис« тора отражателя тока, коллектор которого соединен с базой транзистора второго типа проводимости, эмиттер которого подключен к шине высоковольтного источника питания и че- В рез резистор соединен с его базой, коллектор соединен с базой второго транзистора высоковольтного инвертора.

1058060

И к = И эб1 + И + И к н ъ 1,6 — 1,8 В, меньший отпирающего потенциала ба4 зы транзистора 6, равного И +

+ 2U> см 1 9 — 2 1 В.

Транзистор 6 и последовательно с ним включенные транзисторы 11 и

16 запираются. На выходе элемента формируется низкий уровень выходного сигнала И к эн15 =0, 2 — О, б В.

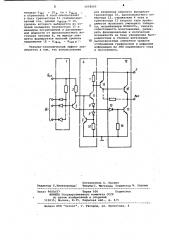

Если на один или несколько входов элемента U 1 подать низкий уровень напряжения, то фазорасщепляющий транзистор 2 и последовательно с ним соединенные диод 13 и и- выходной транзистор 15 запираются.

Ток, протекающий по резистору 3, при запертом транзисторе 2 поднимает потенциал базы транзистора 6

ЬО до уровня И 67 ) И б. + 2 1 см и открывает его, транзистор б — в свою очередь, отпирает последовательно подключенные транзисторы 11 и 16, В установившемся режиме на базе транзистора б устанавливается поИзобретение относится к вычислительной и импульсной технике и микроэлектронике, в частности к интегральным схемам (ИС) для управления газоразрядными индикаторными панелями (ГИП) переменного и постоянного тока.

Известна ИС, содержащая входной логический элемент И, фазорасщепляющий транзистор и сложный инвертор, позволяющая коммутировать высокоуровневые сигналы (1 (.

Недостатками указанной ИС являются большой уровень потребляемой мощности и невозможность коммутирования напряжения выше 20-30 B.

Наиболее близким к предлагаемому по технической сущности является высоковольтное логическое устройство, содержащее входной логический элемент И, фазорасщепляющий транзистор, запитываемые от низковольтного источника питания, и высоковольтный выходной инвертор, позволяющий коммутировать уровни напряжения до 100 В (23.

Недостатком известного устройства является недостаточно высокбе быстродействие и потребление мощности от высоковольтного источника питания в состоянии, когда на выходе элемента низкий уровень выходного напряжения, что приводит. к значительному снижению КПД источников питания, увеличению габаритов устройств управления.

Цель изобретения — исключение потребления мощности от высоковольтнОго источника питания в состоянии низкого уровня выходного сигнала и увеличение быстродействия высоковольтного логического устройCTSa.

Для достижения поставленной цели в высоковольтное логическое устройство, содержащее входной элемент

И, фазорасщепляющий транзистор первого типа проводимости, коллектор которого через резистор соединен с шиной низковольтного источника питания- а база — с выходом входного элемента И, и высоковольтный сложный инвертор на двух транзисторах первого типа проводимости, база первого иэ которых соединена через раэвязывающий диод с эмиттером фазорасщепляющего транзистора„ дополнительно введены отражатель тока на двух транзисторах первого т па проводимости и двух диодах смещения, и транзистор второго типа проводимости, причем коллектор фаэорасщепляющего транзистора соединен с базбй первого транзистора отражателя тока, эмиттер которого через первый и второй диоды смещения подключен к базе второго транзистора отражателя тока, эмиттер которого соединен с общей шиной и через резистср — с его базой, коллектор подключен к базе первого транзистора отражателя тока, коллектор которого соединен с базой транзистора второго типа проводимости, эмиттер которого подключен к шине высоковольтного источника питания и через резистор соединен с .его базой, коллектор соединен с базой первого транзистора высоковольтного инвертора.

На чертеже изображена электрическая схема высоковольтного логического элемента.

Высоковольтный логический эле .мент содержит входной элемент И 1, фазорасщепляющий транзистор 2 с коллекторным резистором 3, запитываемые от низковольтного источника питания, отражатель 4 тока, построенный на транзисторах 5 и 6 первого типа проводимости, резисторе 7, диодах 8 и 9 смещения и токозада-, ваемом резисторе 10, транзистор 11 второго типа проводимости, и высоковольтный инвертор 12, запитываемый от высоковольтного источника питания, включающий развязывающий диод 13, резистор 14 и выходные транзисторы 15 и 16 первого типа проводимости.

Устройство работает следующим образом.

Когда на все входы элемента И 1 подается высокий уровень напряже ния, сткрываются и насыщаются фазо35 расщеплякщий транзистор 2 и выходной транзистор 15. Ток, протекающий по резистору 3, перехватывается иэ базы транзистора б в коллектор транзистора 2, на котором устанавлива4g ется уровень напряжения

1058060

b9

Составитель С. Пронин

Редактор С. Квятковская, Техред С. Мигунова Корректор М лароши

Заказ 9600/57 Тираж 936 Подписное

ВНИИПИ .Государственного комитета СССР по делам изобретений и открытий

113035; Москва, Ж-35, Ра гшская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 тенциал И б + 2И см + И и отражатель 4 тока обеспечивает в базу транзистора 11 стабилизированный ток, равный Изб /R 10, уровень которого выбирается из условий насыщения транзистора 11 и минимума потребляемой и рассеиваемой мощности от высоковольтного источника питания Е, на выходе элемента формируется высокий уровень напРЯжениЯ (Š— И эб Ь - Икун yq )

Технико-э кономический эффект з аключается в том, что использование для включения верхнего выходного транзистора 16, высоковольтного инвертора .12, отражателя 4 тока н транзистора 11 второго типа проводимости позволяет, уменьшить габариты, потребляемую мощность, снизить себестоимость изготовления, расширить функциональные и логические воэможности на базе увеличения быстродействия и степени интеграции

10 высоковольтных элементов средств

) отображения графической и цифровой информации на ГИП переменного тока и постоянного.