Множительное устройство

Иллюстрации

Показать всеРеферат

МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее регистры сомножителей, регистр произведения, блок памяти, коммутатор, первую схему сравнения, причем выходы регистров сомножителей соединенй с соответствуквдими входами первой схемы сравнения и информационными входами коммутатора, управляющий вход которого подключен к выходу первой схемы сравнения, выход блока памяти подключен к входу регистра произведения, первый и второй выходы коммутатора соединены с сооветствующими адресными входами блока памяти, отличающееся тем, что, с целые сокращения объема оборудования пута«1 уменьшения информационной емкости блока памяти , оно дополнительно содержит вторую и третью схемы сравнения дешифратор , входы которого соединены с выходами второй и третьей схем сравнения, первые входы которых под™ ключены к первому и второму выходам коммутатора соответственно, а вто: рые входы - соответственно к первому j и второму входам констант устройства, выходы дешифратора подключены к управляющим входам блока памяти.

„„SU„„,1059567 A

СВОЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

3GD 5 06 E 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЙ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3384270/18-24 (22) 15. 10. 81 (46) 07. 12. 83. Вюл. rrr 45 (7 2) A. В. Комаров (53) 681.325(088.8) ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (56) 1. Ринзбург С.A. и Любарский

Ю. Я. функциональные преобразователи с аналого-цифровым представлением информации. М, Энергия, 1973, с. 63, рис. 3-6.

2. Авторское свидетельство СССР йо заявке Р 3223577/18-24, кл. й- 06 F 7/52, 1980 (прототип). (54)(57) МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее регистры сомножителей, регистр произведения, блок памяти, коммутатор, первую схему сравнения, причем выходы регистров сомножителей соединенй с соответствующими входами первой схемы сравнения и информационными входами коммутатора, управлякщий вход которого подключен к выходу первой схемы сравнения, выход блока памяти подключен к входу регистра произведения, первый и второй выходы коммутатора соединены с сооветствующими адресными входами блока памяти, о т л и ч а ю щ ее с я тем, что, с целью сокращения объема оборудования путем уменьшения информационной емкости блока памяти, оно дополнительно содержит вторуго и третью схемы сравнения„ дешифратор, входы которого соединены с выходами второй и третьей схем сравнения, первые входы которых подключены к первому и второму выходам 3 коммутатора соответственно, а вто:— ,рые входы — соответственно к первому и второму входам констант устройства выходы дешифратора подключены к управлякщим входам блока памяти.

1059567, Изобретение относится к вычислительной технике и может быть использонано также в устройствах автоматики.

Известно множительное устройство, содержащее первый и второй АБЛ, 5 запоминакщее,устройство (ЗУ) и

ПЛП Г1 g.

Недостатком данного устройства является сложность,. обусловленная сложностью ЗУ, информационная емкость 10 которого равна Р = N ° N, С- разрЯдных слон, где К = 2", n - число разрядов сомножителей (выходного кода AIlH).

Наиболее близким техническим решением к предлагаемому является мно- )5 жительное устройство, содержащее регистры сомножителей, регистр произведения, блок памяти, коммутатор, схему сравнения, причем выходы регистров сомножителей соединены с соответствующими входами схемы сравнения и информационными входами коммутатора, управлякщий вход которого подключен к выходу схемы сравнения, выход блока памяти подключен к. входу

perистра произведения, первый и нторой выходы коммутатора соединены с соответствующими адресными входами блока памяти Г2 3.

Недостатком известного устройства является большой объем оборудования, обусловленный большой информационной емкостью блока памяти, которая равна P -- М (М +1) /2. о, Бель изобретения — сокращение объема оборудования путем уменьшения информационной емкости блока памяти.

Пос тав ле -, .ая цель достигается тем, что множительное устройство, содержащее регистры; сомножителей, регистр 40 произв едения, 3 Элок памяти, коммутатор, первую схему сравнения, причем в ыходы рег ис тров сомножителей с оединены с соответствующими входами первой схемы сравнения и информаци- 45 онными входами коммутатора, управляющий вход которого подключен к ныходу первой схемы сравнения, ныход блока памяти подключен к входу регистра произведения, первый и второй выходы 50 коммутатора соединены с соответствующими адресными входами блока памяти, дополнительно содержит вторую и третью схемы сравнения, дешифратор, входы которого соединены с выходами второй и третьей схем сравнения, первые входы которых подключены к первому и второму выходам коммутатора соответственно, а вторые входы— соответственно к первому и второму входам констант устройства, выходы дейшифратора подключены к управлякщим входам блока памяти.

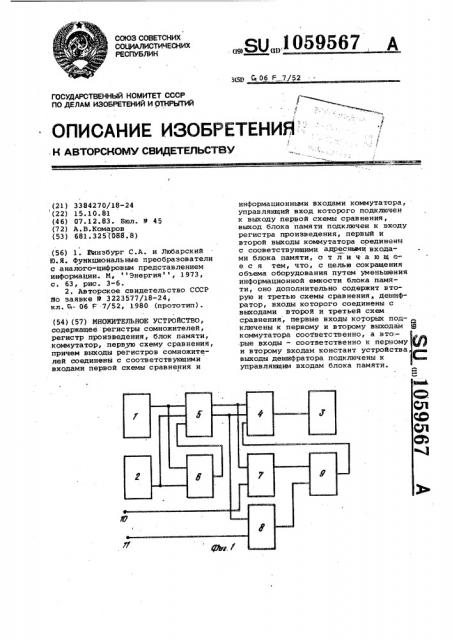

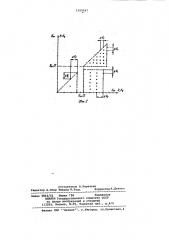

На фиг.1 приведена структурная схема множительного устройства; на фиг.2 †.диаграмма распределения памяти при и= 4.

Множительное устройство содержит регистры 1 и 2 сомножителей, регистр

3 .произведения, блок. 4 памяти, коммутатор 5, первую схему б сравнения, причем выходы регистров 1 и 2 сомножителей соединены с соответствующими входами первой схемы б сравнения и информационными нходами коммутатора

5, управляющий вход которого подключен к выходу первой схемы 6 сравнения, выход блока 4 памяти подключен к входу регистра 3 произведения, первый и второй выходы коммутатора

5 соединены с соответствующими адресными входами блока 4 памяти, а также вторую и третью схемы 7 и 8 сравнения и дешифратор 9, входы которого соединены с выходами второй и третьей схем 7 и 8 сравнения, первые входы которых подключены к первому и второму выходам коммутатора 5 соответственно, а вторые входы — соответственно к первому и второму входам 10 и 11 констант устройства,, выходы дешифратора 9 подключены к управляющим входам блока 4 памяти.

Множительное устройство работает следующим образом.

Н

Бифровые коды сомножителей Х и, хранящиеся соответственно в регистрах 1 и 2 сомножителей, через коммутатор 5 поступают на адресные входы, блока 4 памяти. При этом из ячейки памяти. блока 4 памяти, соответствующей комбинации числа на адресных входах блока 4 памяти, н регистр 3 произведения считывается заранее занесенный н ячейку памяти код произведения .2Н, соответствующий сомножителям "Хн и У . Коммутатор 5 совместно с первой схемой б сравнения уменьшает информационную емкость блока 4 памяти за счет использования перестановочности действия умножения. Дополнительное уменьшение информационной емкости блока 4 памяти (а значит, и упрощение устройства в целом) может быть достигнуто в результате использования неравномерного шага дискретизации сомножителей. Можно показать, что где дх, д Y — шаг дискретизации по X и V соответственно;

Š— относительная погрешность выполнения операции умноже н и я;

Z максимальное значение произведения;

1059567

10 постоянный масштабный коэффициент.

Формулы (1) и (2) показывают, что минимальный шаг дискретизации ь Х . =ь Х и ьУ . = ь Y соответГПМНП 1 ти A

5 ствует диапазонам изменения переменных Y и Х соответственно

Если Йоследнйе соотношения не выполняются, т.е. 0< Г

0 4 Х < Х /2, то шаг дискретизации может бйть удвоен, т.е. дX = 2ьХ и ь Г =2ь (соответствен2 2 1 но. Это позволяет весь объем памяти 15 блока 4 памяти разбить на три мас.сива (фиг. 2; точками помечены значе-. ния сомножителей, для которйх имеется ячейка произведения). Для первого массива характерно выполнение 20 услов ий

Поэтому дискретизация в этом масси 25 ве идет с шагами аХ„и ь Y„Можнопоказать, что информациойная емкость. этого .массива составляет веЛичину

Р = М /8+ М/4.

Для второго массива характерно 3() выполнение условий

Х с,х 24 Х(Х„,сх 0 6 (Ч,,их/2 (4

ПоэтомУ дискРетизация в этом мас сиве идет с шагами ЬХ2 и Ь Y„;. Можно показать, что информационная емкость этого уассива составляет величину

Р = М /8.

Для третьего массива характерно выполнение условий

0<Ха Х „„/г; O(Y< Y„„/2 (5)

Поэтому дискретизация Ъ этом массиве идет с шагами ЬХ2 и at<. Можно показать, что информационная емкость этого массива составит величину

Р = (42/32 + N/ 8.

Суммарная информационная емкость блока 4 памяти боставляет величину 50 р + 2 P3 =9N /Ы+зм/8, (ь) Формула (б) показывает, что применение неравномерного шага дискретизации по Х и Y приводит к уменьшению информационной емкости блока 4 памяти. Вторая схема 7 сравнения производит сравнение Х с Хц /

/2

4 - р ц

Если при этом Х Ъ- Хц /2, то на ц т с х ее выходе формируется сигнал логического нуля, в противном случае— сигнал логической единицы. Третья схема 8 сравнения производит сравнейие Y с 1 „/2. Если 1ц >, /2 то íà de выходе.формируется сйгйал логического нуля.- Код Хц „/2 на второй вход второй схемы 7 сравнения подается с входа 10 констант устройства, код Чц /2 на второй вход цmax третьей схемы 8 сравнения подается с входа 11 констант устройства. Дешифратор 9 анализирует выходные сигналы второй и третьей схем 7 и 8 сравнения и на основе этого фиксиру-. ет выполнение условий (3) — (5) . При этом активизируется один из трех его выходов и связанный с этим выХодом массив памяти блока 4 памяти.

Это достигается тем, что каждый выход дешифратора 9 соединен с входом Выбор кристалла всех .микросхем памяти, входящих в состав соответствующего массива памяти блока 4 памяти.

Преимущество предлагаемого устройства по сравнению с прототипом

,проявляется в уменьшенной информационной емкости блока 4 памяти °

Количественно это уменьшение может характеризовать коэффициент В, определяемый следующим образом:

Р

6-" - NN 1 — 21,7, (Т!

98 /46+ЗМ/4 и

Формула (7) показывает, что при

М r 10 информационная емкость .блока памяти предлагаемого устройства в

1,7 раза меньше информационной емкости блока памяти прототипа. При этом выигрыш в уменьшении объема оборудования путем уменьшения информационной емкости блока памяти существенно превосходит потери, связанные с наличием второй и третьей схем сравнения и дешифратора.

1059567

Составитель В.Березкин

Редактор A.Îãàð Техред M.Íàäü .КорректорА.дзятко

Завез. 9842/53.- Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, ° д.4/5

Филиал ППП Патент, r.Óæãîðîä, ул.Проектная,4