Устройство для логарифмирования двоичных чисел

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ ДВОИЧНЫХ ЧИСЕЛ, содержащее первый блок деления, регистр старших разрядов аргумента, выход которого соединен с входом первого блока памяти и с первыми входами первого и второго сдвигатёлей, выход регистра младших разрядов аргумента подключен к вторым входам первого и второго сдвигатёлей, выход второго блока памяти соединен с первым информационным входом первого коммутатора, выход которого подключен к первому входу первого сумматора, выход второго коммутатора соединен с вторьдм входом первого сумматора, вход которого подключен к входу регистра результата, выходы блока синхронизации соединены с управляющими входами регистров старших и младших разрядов аргумента, первого и второго коммутаторов, первого и второго регистров и третий сдвигатель,отличающее ся тем, .что,.с целью повышения быстродействия , в него-дополнительно введены второй сумматор, второГ- блок деления и третий регистр, причем выход регистра старших разрядов аргумента соединен с информационным входом первого регистра, выход которого подключен к входу второго блока памяти, выход регистра младших разрядов аргумента соединен с информационным входом второго регистра, выход которого подключен к первому информационному входу второго коммутатора и информационному входу третьего сдвигателя , выходы первого и в орого сдвигателей соединены с первыми информационными входами первого блока деления и второго сумматора соответственно , выход первого блока памяти (Л подключен к второму информационному входу первого блока деления, выход которого соединен с вторым входом второго сумматора, выход которого подключен к информационному входу третьего регистра, выход которого соединен с первым информационным входом второго блока деления, второй вход которого подключен к выходу пер ел вого сумматора, выход второго блока со СП деления соединен с вторым информационным входом второго коммутатора, выход третьего сдвигателя подключен vl к второму информационному входу первого коммутатора, выходы блока синю хронизации соединены с управляющими входами первого и второго блоков деления , третьего регистра, третьего сдвигателя и регистра результата.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„яф„,10Ю572

З{5П G 06 Г 7/556

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3397952/18-24 (22) 10.12.81 (46) 07.12.83. Бюл. Р 45 (72) М.Ю.Плотников, В.И.Потапов и A.Н.Флоренсов (71) Омский политехнический институт (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

Р 593212, кл. G 06 F 7/556, 1978.

2. Авторское свидетельство СССР

Р 9?4705, кл. {, 06 Р 7/556, 1980 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРО-

ВАНИЯ ДВОИЧНЫХ ЧИСЕЛ, содержащее первый блок деления, регистр старших разрядов аргумента, выход которого соединен с входом первого блока памяти и с первыми входами первого и второго сдвигателей, выход регистра младших разрядов аргумента подключен к вторым входам первого и второго сдвигателей, выход второго блока памяти соединен с первым информационным входом первого коммутатора, выход которого подключен к IIBpBo входу первого сумматора, выход второго коммутатора соединен с вторым входом первого сумматора,.вход которого подключен к входу регистра результата, выходы блока синхронизации соединены с управляющими входами регистров старших и младших разрядов аргумента, первого и второго коммутаторов, первого и второго регистров и третий сдвигатель,о т л и ч а ю щ е е с я тем, .что, с целью повышения быстродействия, в него -дополнительно введены второй сумматор, второй блок деления и третий регистр, причем выход регистра старших разрядов аргумента соединен с информационным входом первого регистра, выход которого подключен к входу второго блока памяти, выход регистра младших разрядов аргумента соединен с информационным входом второго регистра, выход которого подключен к первому информационному входу второго коммутатора и информационному входу третьего сдвигателя, выходы первого и второго сдвигателей соединены с первыми информационными входами первого блока деления и второго сумматора соответст- щ

С венно, выход первого .блока памяти подключен к второму информационному входу первого блока деления, выход которого соединен с вторым входом второго сумматора, выход которого подключен к информационному входу третьего регистра, выход которого соединен с первым информационным входом второго блока деления, второй (, вход которого подключен к выходу пер-, вого сумматора, выход второго блока и деления соединен с вторым информа- (ф ционным входом второго коммутатора, выход третьего сдвигателя подключен к второму информационному входу первого коммутатора, выходы блока синхронизации соединены с управляющими входами первого и второго блоков деления, третьего регистра, третьего сдвигателя и регистра результата.

1059572

Изобретение относится к вычислительной технике и может быть исполь эовано н качестве цифрового генератора значений логарифмической функции.

Известно цифровое устройство для 5 логарифмирования двоичных чисел, которое содержит регистр старших разрядов аргумента, соединенный с адресными входами двух блоков памяти и регистр младших разрядов аргумента, 10 вход которого через сдвигатель,первый коммутатор и сумматор подключен к выходному регистру (1 g.

Основным недостатком подобных устройств является большой объем постоянной памяти, требуемый для хранения таблиц коэффициентов, что существенно сужавт область применения подобных устройств и позволяет их использовать лишь н малораэрядных

ЦВМ.

Наиболее близким к предлагаемому является устройство для логарифмирования двоичных чисел, которое содержит регистр старших разрядов ар- 25 гумента, соединенный с адресным входом блока памяти и с входами второго и третьего сднигателя„ регистр младших разрядов аргумента, выход которого соединен с вторыми входами первого и второго сдвигателя, первый блок деления, входы которого соединены.с выходами первого блока памяти и вторым сдвигателем, второй блок памяти, выход которого подключен к первому входу первого коммутатора, второй нход которого соединен с выходом третьего сдвигателя, а выход подключен к первому входу первого сумматора, второй вход которого соединен с выходом второго коммутатора, а выход 40 связан с регистром результата, и блок .синхронизации Г2 3.

В известном устройстве значительно снижается емкость блоков памяти по сравнению с устройством-аналогом, но заметно увеличивается время вычисления логарифма, что связано с двукратным последовательным применением операции деления.

Цель изобретения - повышение про- 50 изводительности устройства.

Поставленная цель достигается тем, что в устройство для логарифмирования двоичных чисел, содержащее первый блок деления, регистр старших разрядон аргумента, выход которого соеди нвн с входом первого блока памяти и с первыми входами первого и второго сдвигатвлей, выход регистра младших разрядов аргумента подключен к вторым входам первого и второго сдвигателвй, выход второго блока памяти соединен с первым информационным входом первого коммутатора, выход которого подключен к первому входу пер- . ,вого сумматора, выход-.второго коммутатора соединен с вторым входом первого сумматора, выход которого подключен к входу регистра результата., выходы блока синхронизации соединены с управляющими входами регистров старших и младших разрядов аргумента, первого и-второго коммутаторов,первого и второго регистров и третий сдвигатель, дополнительно ннедены второй сумматор, нторои блок деления и третий регистр, причем выход регистра старших раэрядон аргумента соединен с информационным входом первого регистра, выход которого подключен к входу второго блока памяти, выход регистра младших разрядов аргумента соединен с информационным входом второго регистра, выход которого подключен к первому информационному входу второго коммутатора и информационному входу третьего сднигателя, выходы первого и второго сднигателей соединены с первыми информационными входами первого блока деления и второго сумматора соответственно, выход первого блока памяти подключен к второму информационному входу первого блока деления, выход которого соединен с вторым входом второго сумматора, выход которого подключен к информационному входу третьего регистра, выход которого соединен с первым информационным входом второго блока деления, второй вход которого подключен к выходу первого сумматора, выход второго блока деления соединен с вторым информационным входом второго коммутатора, выход третьего сдвигателя подключен к второму информационному входу первого коммутатора, выходы блока синхронизации соединены а управляющими входами первого и второго блоков деления, третьего регистра, третьего сдвигателя и регистра результата.

Вычисление натурального логарифма от нормализованного аргумента

x(1/2 «< х<1) производится в устройст- ве на основе следующих соотношений

6п X= F(<)

F (Х) = ЕпХ,+ЗЬХ/ „(Х)

Р (Х)=4Хо+ )(-2 Х о!(2 Хо+ и X)

Здесь х — опорная. часть аргумента, представленная К-старшими разрядами аргумента, а ь х — приращение аргумента, представленное ь -К-двоичными разрядами, где v — общее количество разрядов требуемое для представления аргумента х.

Значения (ь K и-2Хс, зависящие

z только от опорной части аргумента, нычисляются предварительно и заносятся в таблицы, реализованные на блоках постоянной памяти.

1059572

50.F (xi=4x iьх-2х 1(2х iьх) В третьем такте работы устройства по сигналу блока 18 синхронизации значение Р X поступает на третий регистр 10, значение Ьх поступает на второй регистр 7„ а значение xg на первый регистр 2. При этом значение

2дх, сформированное.на третьем сдвигателе 15, через первый коммутатор 60

16 поступает на второй вход первого сумматора 13, на второй вход .Которого поступает значение дх, переданное через второй коммутатор 12. Значение

Зфх с выхода первого сумматора посту-65

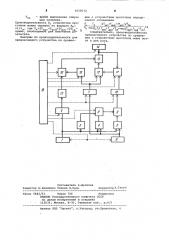

На чертеже представлена блок-.схема предлагаемого устройства.

Устройство содержит регистр 1 старших разрядов аргумента, первый регистр 2, первый блок 3 памяти, первый и второй сдвигатели 4 и 5 сост- 5 ветственно, регистр б младших разрядов аргумента, второй регистр 7,первый блок 8 деления, второй сумматор

9, третий регистр 10, второй блок 11 деления, второй коммутатор 12, первый 10 сумматор 13, регистр 14 результата, третий сдвигатель 15, первый коммутатор 16, второй блок 17 памяти.и ,блок 18 синхройизации.

Первый и второй сдвигатели 4 и 5 15 реализуют операции Х вЂ” 4Х +дХ, и Ф 2Х +дХ соответственно, которые заключаются в сдвиге старших разрядов аргумента на 2 и 1 разряд влево и заполнении освободившихся разрядов 20 нулями.

Предлагаемое устройство для логарифмирования двоичных чисел работает следующим образом.

В первом такте, работы устройства 25 по сигналу блока 18 синхронизации происходит прием означения. аргумента х на регистры старших 1 и младших б разрядов аргумента. Значение X c выхода .регистра 1 старших разрядов аргумента передается на адресные входы первого блока 3 памяти, на выходе которого появляется значение

2х2, поступающее на вход делимого первого блока"8 деления, и на входы 35 первого и второго сдвигателей 4 и 5, на другие входы которых поступает значение дх с выхода регистра б младших разрядов аргумента. На выходах первого и второго сдвигателей 4 40 и 5 формируются значения 2х +дх, поступающие на вход делителя первого блока 8 деления, и 4, поступающее на второй вход второго сумматора 9.

ВО ВТороМ такте пО сигналу блОки 45

18 синхронизации запускается первый блок 8 деления и результат операции поступает на первый вход второго сумматора 9, на выходе которого образуется значение пает на вход делимого второго блока

11 деления, на вход делителя которого передается значение F (Х), с выхода третьего регистра 10. Одновременно с этим блок 18 синхронизации выдает сигналы управления для первого такта работы устройства, обеспечивая тем самым прием нового значения аргумента Х и его последующую обработку, описанную выше.

В четвертом такте работы по сигналу блока 18 синхронизации второй блок 11 деления выполняет операцию деления и через второй коммутатор 12 передает результат на первый вход первого сумматора 13, на второй вход которого передается через первый коммутатор 16 значение PnXО с выхода второго блока 17 памяти. На выходе первого сумматора 13 формируется значение, F(X)=СпХ +Зд Х!F<(X). ОцновРеменно с этим блок 18 синхронизации выдает сигналы управления для второго такта работы устройства, обеспечивая тем самым правильную последовательность работы блока устройства, приводящую к формированию значения промежуточного результата F„(X) на выходе второго сумматора 9 для нового значения.аргумента х.

В пятом такте работы устройства по сигналу блока синхронизации значение F(X) с выхода первого сумматора 13 принимается на регистр 14 результата. Одновременно с этим блок

18 синхронизации выдает сигналы управления для первого и третьего тактов работы устройства, что обеспечивает последовательности функционирования блоков устройства, описанные выше для соответствующих тактов его работы.

Оценим производительность Р" данМ ного устройства, определяемую количеством вычисленных значений логарифма в единицу времени:

P =1/па (Т„,Т„1, где Т - ape&a выполнения первого и

0 второго тактов работы, Т вЂ” время выполнения третьего

l и четвертого тактов устройства. т =Тзд +Твуб+тдел+тсд т =т „+т +тде „, 2 тсм > здесь Т „ — время записи информации на регистр;

Т,5 — время выборки информации из блока памяти

Т вЂ” время выполнения операции сдвига на сдвигателе, время выполнения операДйА ции деления;

1059572

Составитель A.Øóëÿïoâ

Редактор A Âëàñåíêî Техред И.Надь Корректор A ° Òÿñêî

Заказ 9842/53, Тираж 70б Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035; Москва, E -35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãoðoä, ул.Проектная, 4

Т вЂ” время выполнения операции сложения.

Производительность Р„ устройства прототипа можно оценить по формуле Р =

=1/т и, где Т„=2Т „+T. 8 2Т „+ Г время, необходимое для йолучения результата.

Выигрыш по производительности для предлагаемого устроиства по сравнению с устройством прототипа определяется отношением

Т 2Т +Т +2Т +2Т и оп выб дел - см

P д (Т,Т ) Т +Т +Т +гпсцс(Т < Т +Т 1=2 заа дЕл сы бабi сда см!

СледЬвательно, производительность предлагаемого устройства по сравнению с устройством прототипа выше почти в два раза.