Цифровой частотный детектор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ЗСЮ Н 0З О З/00

1l

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ГЮ ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3398109/18-09 (22) 19.02 ° 82 (46) 07.12.83. Бюл. 9 45 (72) А.М. Агиэим, Л.Е. Добродняк и А.Е. Фриш (71) Львовский ордена Ленина политехнический институт им. Ленинского комсомола (53) 621. 376. 33 (088. 8) (56) 1 ° Патент Японии и 52-35274, кл. 98/5/Е 21 H 03 D 3/00, 08.09.77

2, Авторское свидетельство СССР

Ф 841081 кл, Н 03 D . 3/00, 23, 06, 81 (прототип), (54)(57) ЦИФРОВОЙ ЧАС101НЫЯ ДЕТЕК 1ОР, содержавший входной формирователь, первый D --триггер, последовательно соединенные генератор тактовых импульсов и счетчик, дешифратор, первые входы которого соединены с выходами счетчика, а вторыес переключателем детектируемой частоты, последовательно соединенные выходной формирователь и фильтр ниж„„SU„„ 1059659 А них частот, причем выход входного формирователя подсоединен к Ц -входу первого D -триггера, прямой выход которого подключен к .входу выходного формирователя, о т л и ч а ющ и и с я тем, что, с целью расширения диапаэона детектирования в область верхних частот, в него введены второй Р -триггер, 6 -вход ко. торого соединен с выходом входного формирователя, одновибратор,первый и второй элементы И, первые входы котОрых подключены к прямым выходам. соответственно первого и второго

D-триггеров, выход первого элемента

И соединен со счетным входом второго D -триггера, а выход второго эле- Е

С2 мента И вЂ” со счетным входом .первого

D-триггера, инверсный выход которого соединен с его. -входом, а вторые входы первого и второго элементов И объединены между собой и подсоединены к выходу одновибратора, вход которого подключен к выходу дешифратора.

1059659

Изобретение относится к измерительной технике и может быть использовано в устройствах для частотного детектирования в широком диапазоне частот с обеспечением линейной зависимости выходного напряжения от час- 5 тоты входного сигнала.

Известен цифровой частотный детектор, содержащий входной формирователь, делитель частоты, тактовый генератор, элементы И и ИСКЛЮЧАЮЩЕЕ

ИЛИ, а также фильтр нижних частот (11 .

Однако известное устройство обладает большой погрешностью детектирования, зависящей оТ формы входного сигнала, качества входного формирователя, и из-за отсутствия синхронизации фазы колебаний тактовой частоты и входного частотно-модулированного сигнала.

Наиболее близким к предлагаемому по технической сущности является цифровой частотный детектор, содержащий входной формирователь, первый 0 -триггер, последовательно соединенные генератор тактовых импульсов и счетчик, дешифратор, первые входы которого соединены с выходами счетчика,. а вторые — с переключателем детектируемой частоты, последовательно соединенные выходной формирователь и фильтр нижних частот, при этом выход входного формирователя подсоединен к R -входу первого В -триггера, прямой выход которо го подключе н к входу выходного формирователя (.2) .

Однако известный цифровбй частот» 35 ный детектор обладает недостаточно широким частотным диапазоном детектирования.

Цель изобретения — расширение

Jyr диапазона детектирования в область 40 верхних частот.

Для достижения цели в цифровой частотный детектор, содержащий входной формирователь, первый )3 -триггер, последовательно соединенные генера- 45 тор тактовых импульсов и счетчик, дешифратор, первые входы которого соединены с выходами счетчика, а вто» рые — с переключателем детектируемой частоты, последовательно соединенные выходной формирователь и фильтр нижних частот, причем выход входного формирователя подсоединен к ((-входу первого 1) -триггера, прямой выход которого подключен к входу 55 выходного формирователя, введены второй 9 -триггер, 5 -вход которого соединен с выходом входного формирователя, одновибратор, первый и второй элементы И, первые входы которых подключены к прямым выходам соответственно первого и второго D триггеров, выход первого элемента И соединен со счетным входом второго

2-триггера, а выход второго элемента

И вЂ” со счетным входом первого 3 †. 65 триггера, инверсный выход которого соединен с его П -входом, а вторые входы первого и второго элементов И объединены между собой и подсоединены к выходу одновибратора, вход которого подключен к выходу дешнфратора.

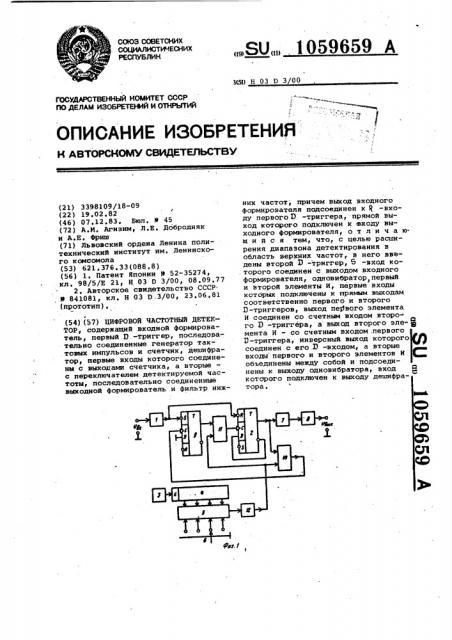

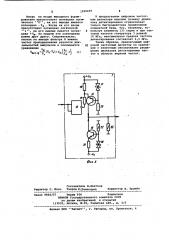

На фиг.1 представлена структурная электрическая схема цифрового частотного детектора; на фиг.2 — принципиальная электрическая схема выходного формирователя.

Цифровой частотный детектор содержит входной формирователь 1, первый 1) -триггер 2, генератор 3 тактовых импульсов, счетчик 4, дешифратор 5, переключатель б детектируемой частоты, выходной формирователь 7, фильтр 8 нижних частот, второй 1) триггер 9, первый и второй элементы

И 10 и 11, одновибратор 12, причем выходной формирователь 7 содержит инвертор 13, резистор 14, транзисторы

15 и 16, стабилитроны 17 и 18., резисторы 19-23.

Цифровой частотный детектор работает следующим образом.

В момент перехода входного сигнала через нуль (например, из минуса в "плюс ) на выходе входного формирователя 1 появляется короткий по длительности импульс, соответствующий логическому сигналу 0, который по входу 5 устанавливает второй Э -триггер 9 в состояние 1 а по входу К устанавливает первый

D триггер 2 в состояние 0 . Первый тактовый импульс со счетчика 4 через дешифратор 5 и одновибратор 12, а также через второй элемент И 11 поступает на счетный вход D -триггера 2 и устанавливает его в состояние 1" . Первый тактовый импульс через первый элемент И 10 на счетный вход

3-триггера 9 не проходит, так как на его первом входе имеется потенциал логического 0, а длительность импульса на выходе одновибратора 12 мала. Через промежуток времени Т /2 второй тактовый импульс проходит на счетный вход D -триггеров 2 и 9 через элементы И 11 и 10 соответственно,9 -триггеры 9 и 2 переходят в состояние 0 . В этом состоянии оба 1) -триггера находятся до момента окончания первого периода Т», где

Тк — период входного сигнала. При следующем переходе входного сигнала через нуль (иэ минуса в плюс ) цикл работы детектора повторяется.

Выходной формирователь 7 содержит управляемый через инвертор 13 и резистор 14 источник тока положительной полярности на транзисторе 15, стабилитроне 17 и резисторах 19 и 20, а также источник тока отрицательной полярности на транзисторе 16, стабилитроне 18 и резисторах 21 и 22, резистор 23 суммирующий.

1059659

Явг. Р

Составитель В.Цветков

Редактор С. Юско Техред В.далекорей

Корректор И. Эрдейи

Заказ 9856/57 Тираж 93б Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. ужгород, ул. Проектная, 4

Когда на входе выходного формирователя присутствует потенциал логи» ческого 0, на его выходе имеется потенциал - Ми ° Когда Hà его входе ,присутствует потенциал логической 1, на его выходе имеется потен- 5 циал +:Чи. По модулю эти потенциалы. равны друг другу. Следовательно, сигнал на выходе фильтра 8 нижних частот пропорционален разности длительностей импульсов и описывается щ уравнением Ч

"м (С»

Ч„,„, * — (7o.ò.1=Ч„ — - (1) с* „

B предлагаемом цифровом частот- ном детекторе верхнюю границу диапазона детектирования ограничивает только быстродействие применяемой элементной базы. Так, например, используя элементы 133 серии и при тактовой частоте генератора 3 равной

10 МГц, максимальная средняя частота детектирования составляет 4,5 ИГц.

Таким образом, предлагаемый цифровой частотный. детектор по сравнению с известным обеспечивает расюи рение диапазона детзктируемых час-. тот в область. верхних частот.